CORDIC算法在跟踪环中的应用与FPGA实现

2010-09-25李玉柏

王 雷, 李玉柏, 潘 军

(电子科技大学 通信与信息工程学院,四川 成都 611731)

0 引言

CORDIC由Volder.J在1959年提出[1],1971年J.S.Walther提出了改进的统一CORDIC算法[2],把圆周运算、双曲旋转和直线旋转统一到一个CORDIC迭代方程里,为统一的硬件实现提供了理论基础。CORDIC算法从算法本身入手,将这些复杂的超越函数分解为简单的加法和移位运算,而且该算法是一种规则的算法,可以很容易在硬件上实现。目前CORDIC算法已经被成功地应用于FFT,DCT等数字信号处理等领域。

CORDIC统一迭代公式如式(1),定义一个三维向量{[xk,yk, zk]},在 k > 0 时进行迭代[3]:

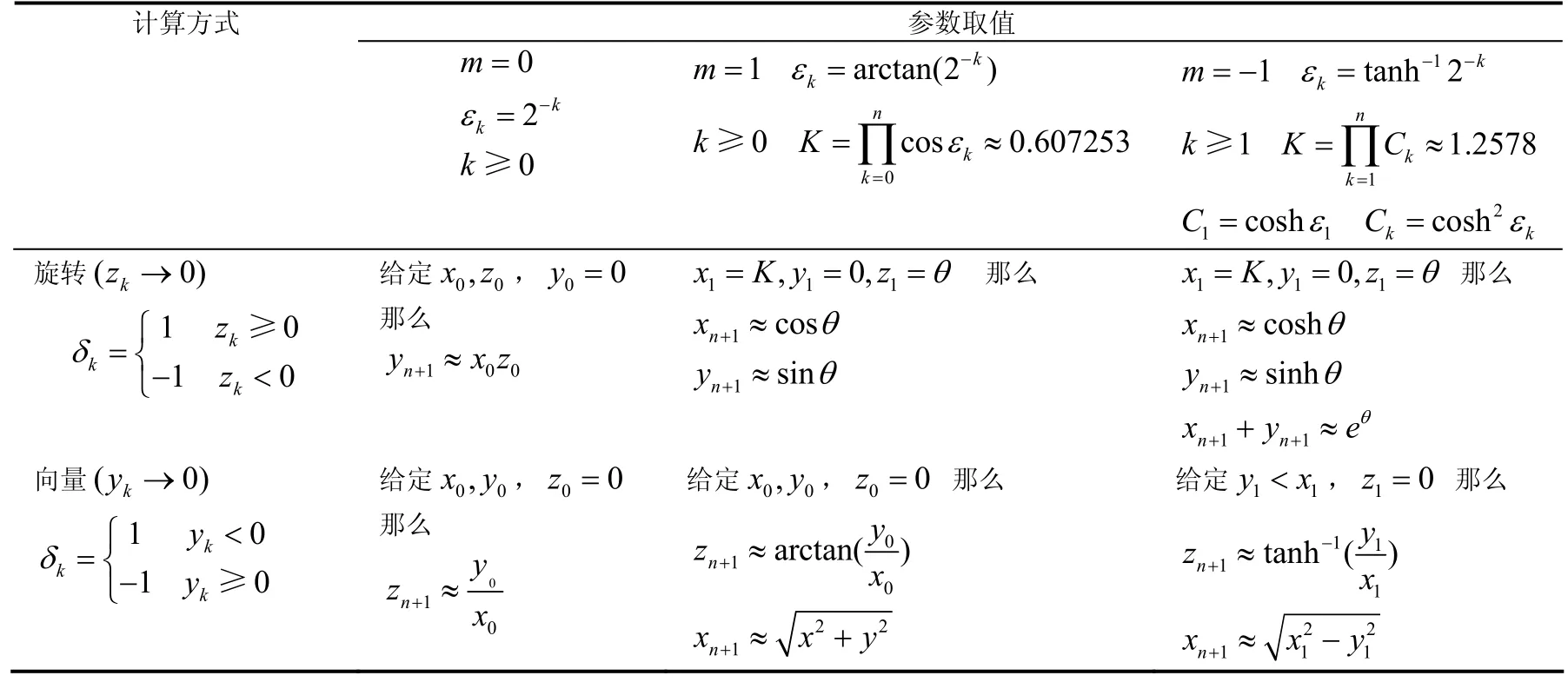

其中εk,初始状态{[x0,y0,z0]}以及m决定了算法计算的结果。 δk(= ±1)是在每次迭代过程中决定的,使计算能够不断地接近结果。具体函数计算方法可参考表1。

在跟踪环路的鉴相器中,计算结果范围都在CORDIC算法最大输入范围之内,不需要进行有效输入范围扩展。在实现通用的统一CORDIC算法计算时,可采用Argument Reduction算法来进行输入范围的扩展。

1 GPS信号跟踪环路

信号跟踪环路在信号捕获完成之后启动。码环(DLL)生成PRN码的复制码,并使它和接收码对准。锁频环(FLL)和锁相环(PLL)产生一个正弦载波,并保持其频率与接受的载波频率一致[4]。码和载波的这些操作称为信号跟踪。

图1是GPS信号跟踪环路的结构图,其中载波环鉴相器包括了PLL和FLL的鉴别器,在这个跟踪环路中,总共有3个鉴别器需要实现。其中每个鉴相器都有多种计算方法,性能都不相同。为了实现最好的跟踪效果,都选择了最大似然估计的鉴别器[5],表2中为各个环路中的最大似然鉴别器[6]。

这里要实现的鉴相器,是使用统一的CORDIC算法,能在一个CORDIC基本运算单元上实现三种鉴相器功能的鉴相器。

图1 跟踪结构

表1 CORDIC算法原理

表2 环路鉴相器算法

2 CORDIC算法仿真

这里需要仿真来确定需要进行CORDIC算法时所需要的宽度和迭代次数。为了保证环路计算的精度,需要保证计算结果误差在1 %之内。在matlab中对不同迭代次数对精度的影响进行了仿真,这里使用了全精度的浮点数进行计算。

从图2可以看出,全精度计算时,在迭代到第10次时,就可以保证把向量模的误差在1 %以内,保证误差角度小于0.1°。在上面的全精度计算中,对特殊输入值0,都进行了单独的处理,简化计算,防止出现错误。

根据前面全精度仿真结果,为了使鉴相器达到1%的精度,迭代次数要大于10次。从跟踪环路的时间安排以及计算精度考虑,在本鉴相器中采用的迭代次数是80次。

3 鉴相器结构

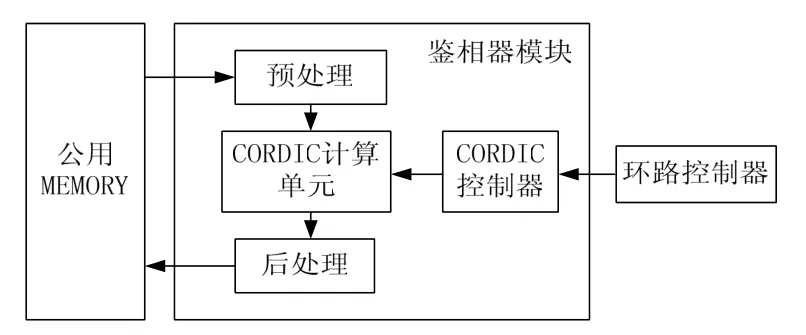

鉴相器结构如图3所示。

图中鉴相器模块包括预处理模块、CORDIC计算单元、后处理模块和CORDIC控制模块。预处理模块从公用MEMORY中读取21位的有符号数积分信息,然后进行位扩展,在积分结果后面加入64比特0并扩展符号位,使总位数变为110位,保证计算过程中不会出现溢出的情况,并且留下了充足的保护位。预处理结束后,数据进入CORDIC计算模块,CORDIC控制器根据环路控制器送出的指示信号,控制CORDIC计算模块进行PLL、DLL或FLL的鉴相运算。运算结束后,数据进入后处理模块,根据进行鉴相的类型,后处理模块会把结果信息存入公用MEMORY的指定地址,完成鉴相操作。

图2 迭代次数与误差百分比关系

图3 鉴相器结构

该结构利用CORDIC统一迭代公式,在一个CORDIC计算模块中实现了多种超越函数的计算,节省了硬件资源,也保证了计算结果的精度。

4 结语

该鉴相器的Verilog代码在VCS环境中进行了验证,结果表明计算结果误差均小于1 %,满足跟踪环路需求。图4是RTL仿真结果。

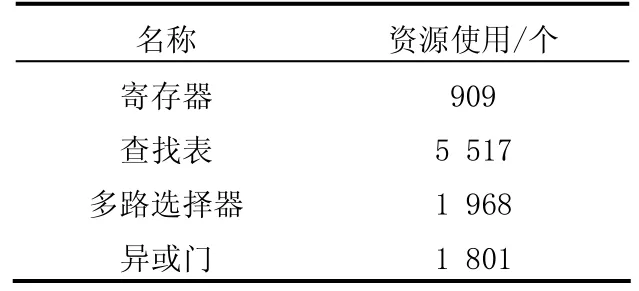

该鉴相器的实现方法,使用时分复用的方法,根据跟踪环路的特点在统一的结构上实现了三种鉴相运算,与传统鉴相器实现方法相比,充分利用了FPGA资源。在Xlinx的Virtex5 lx220上使用Synplify进行综合,占用资源情况如表3示。

从下面的列表可以看出,由于计算位宽比较大,所以使用寄存器比较多。位宽大的加法器也占用了很多逻辑资源。以后可以在计算的位宽以及加法器优化上面对该鉴相器进行改进。在GPS与BD2双模信号跟踪环路中使用该鉴相器,在Xlinx的Virtex5 lx220上进行了测试,测试结果表明环路性能良好,可以很好的进行导航比特的解调和定位。

图4 鉴相器RTL仿真结果

表3 资源占用情况分析

[1] VOLDER J E. The CORDIC Trigonometric Computing Technique[M].IRE Trans.on Electron Computing,1959(08):330-334.

[2] TIMMERMANN D, SUNSBO I. Area and Latency Efficient Cordic Architectures[J]. Circuits and Systems,1992(03):1093-1096.

[3] PRATAP Misra,PER Enge.Global Positioning System Signal,Measurements,and Performace[M].Second Edition.Beijing:Publishing House of Electronics Industry,2008.

[4] 徐长雷,蔡德林,刘晓琴.基于软件无线电的载波跟踪环研究及仿真[J].通信技术,2007,40(11):113-115.

[5] WALTHER J S. A Unified Algorithm for Elementary Functions[J].Proc. AFIPS Conference,1971(38):389-385.

[6] 陈启兴,任国强,吴钦章.一种新数字锁相环[J].通信技术, 2008,41(06):86-87.