挠性印制电路板板边插头的优化设计

2024-03-22翟可鹏

钱 燚 翟可鹏,3 冯 卓

[1.珠海景旺柔性电路有限公司,广东 珠海 519000;2.广东省精密柔性电路工程技术研究中心,广东 珠海 519000;3.景旺电子科技(龙川)有限公司,广东 河源 517373)

0 引言

在高频信号传输过程中,电路设计过程中如果考虑不全面,将会使高速传输的数字信号出现串扰、反射、衰减等影响信号完整性的问题[1]。为保证信号完整性,通常要求在设计阶段进行信号仿真,确保电路设计合理。

信号仿真中,S参数(散射参数)能够表征传输线阻抗、隔离度、耦合、信号的衰减等,因此S参数无疑是一种重要的射频(radio frequency,RF)参数。挠性印刷电路板(flexible printed circuit board,FPCB)板边插头测试S参数前,需要验证板边插头设计的合理性,如果板边插头回路设计不合理,接地通孔(grounding throughhole via,GND VIA)与地线之间的回流传播间距可能产生寄生电容,对于信号插入损耗波形来说,回流传播在高频区间段内产生谐振,会导致信号传输质量降低。

本文针对板边插头进行优化设计,以减小GND VIA 与地线之间回流传播间距对信号插入损耗出现谐振点的影响。

1 影响分析

1.1 影响插入损耗因素

插入损耗是指在传输系统的某处由于元器件的插入而发生负载功率的损耗,表示为该元器件插入前负载上所接收到的功率与插入后同一负载上所接收到的功率以分贝dB 为单位的比值。影响传输线插入损耗的因素见表1。

表1 影响插入损耗的因素

由表1 可知,导体损耗、介质损耗由材料性质决定,反射损耗、辐射损耗通过设计阻抗线、表面屏蔽等方式减小。板边插头测试信号与实际信号的差异分析串扰影响较大:GND VIA 与板边插头接地线间的回流传播距离过长,信号传输中产生耦合电流,使线路间产生串扰,造成插入损耗测试波形出现谐振,导致插入损耗数据偏大。因此要分析FPCB 信号线耦合损耗(串扰)原因,以降低串扰影响。

1.2 串扰的影响

串扰是指信号在传输通道上传输时,因电磁耦合对相邻的传输线产生不期望的影响,对被干扰信号注入了一定的耦合电压和耦合电流[2]。根据麦克斯韦定律,只要有电流存在就会有磁场存在,磁场之间的干扰就是串扰。还可能会导致传输数据的丢失和传输错误[3]。

FPCB产品空间受限,板边插头接地线段悬空设计形成“天线效应”,且GND VIA 与板边插头接地线间回流传播产生耦合电流,使信号本身衰减并与邻近信号干扰,影响传输线传输信号质量。若串扰增大到一定值会致使信号传输误码,系统稳定性变差,甚至出现信号中断现象。

2 实物分析

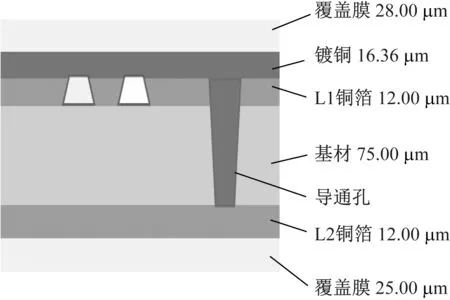

2.1 叠构说明

本实验选取双面柔性基铜板镀铜制作线路、与覆盖膜压合作为叠层结构,采用差分线设计测试板,具体叠构如图1所示。

图1 产品实际叠构图

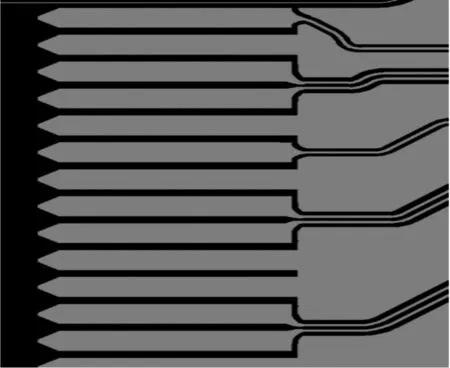

2.2 板边插头及测试线设计

FPCB 板边插头设计如图2 所示。板边插头地线与GND VIA 间有一段回流传播距离产生耦合电流,造成串扰;而板边插头末端为悬空段,此段线路会形成向外辐射的天线[4],产生电磁辐射,干扰FPCB 传输线传输信号质量。S参数测试过程板边插头与测试探针标准间距不匹配,在实际测试中需要在板边插头末端增加设计一段测试线才能进行损耗测试。

图2 FPCB板边插头设计

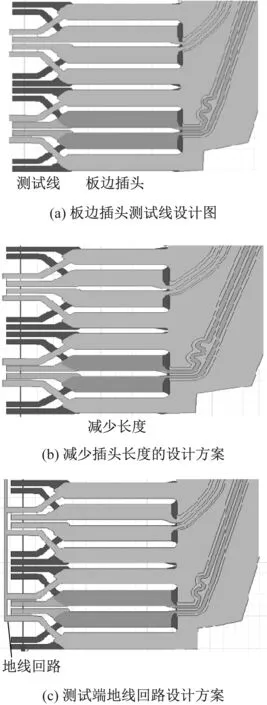

基于以上分析,本文验证优化前设计、缩短板边插头长度、测试端地线相连形成回路3 种方案,如图3 所示。通过信号损耗测量、信道眼图拟合分析、史密斯圆图对比验证分析3 种方式,验证对比3 种方案的信号传输变化情况,得出更优的设计方案。

图3 板边插头测试线设计

3 验证测试

3.1 测试仪器及校准方法

测试设备:矢量网络分析仪E5071C、探针台、GSSG 350探针1对、校准片。

校准方法:短路开路负载传输(short-openload-through,SOLT)校准方式中,与网分连接的探针在已知特性的校准片上进行短路、开路、连接负载与直通连接校准,通过网分处理测试数据并消除测试误差。

3.2 信号损耗验证

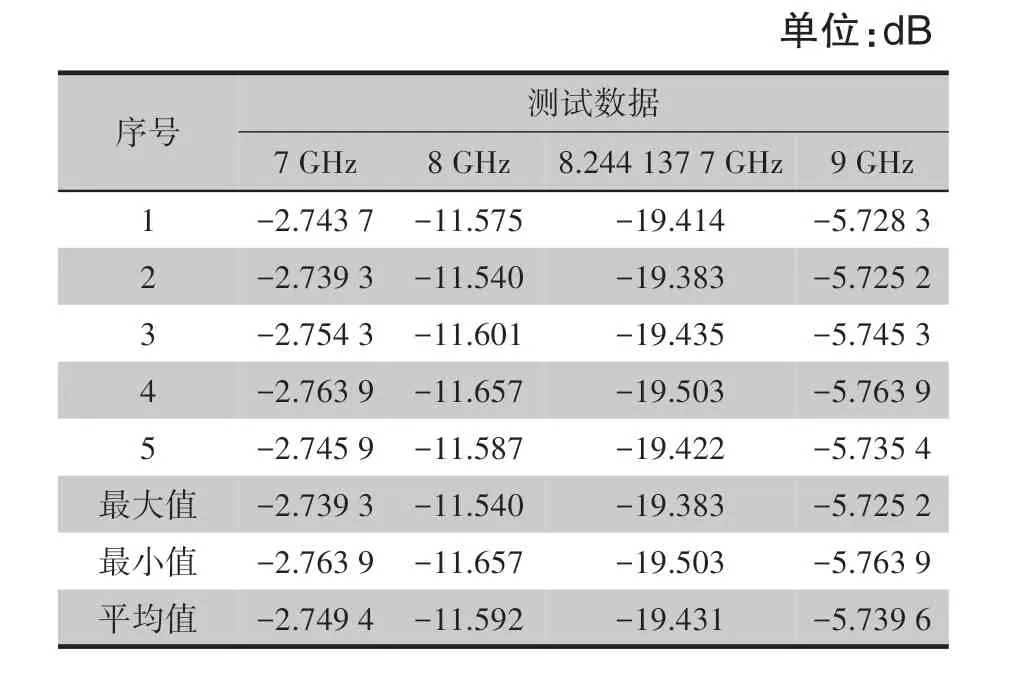

3.2.1 设计方案优化前的测试数据

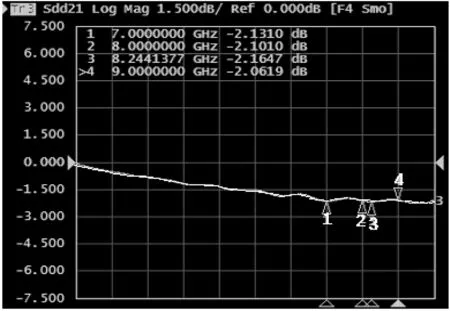

优化设计前插入损耗测试结果如图4和表2所示。因信号线间产生串扰,可以从测试图及表中看出,在8.244 137 7 GHz 频点插入损耗波形出现谐振,其传输信号质量最差,导致此基频信号传输质量也随着降低。

图4 优化设计前插入损耗测试

表2 优化前设计测试数据

3.2.2 缩短板边插头长度的产品测试数据

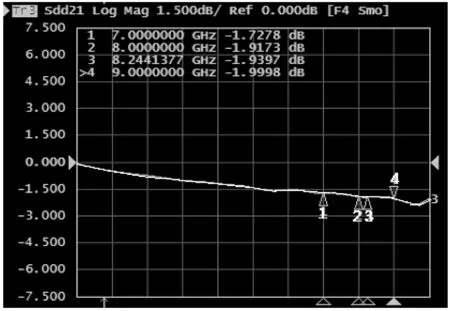

缩短板边插头长度,减少与GND VIA 回流传播路径,从而避免产生串扰,抑制谐振点,改善谐振频率点上的信号传输质量,设计方案如图3(b)所示。

缩短板边插头长度设计方案插入损耗测试结果见图5 和表3。由图5 可见,在8.244 137 7 GHz频点的谐振有所改善,其测试数据趋于正常,但损耗波形稍有抖动。

图5 缩短板边插头设计方案插入损耗测试

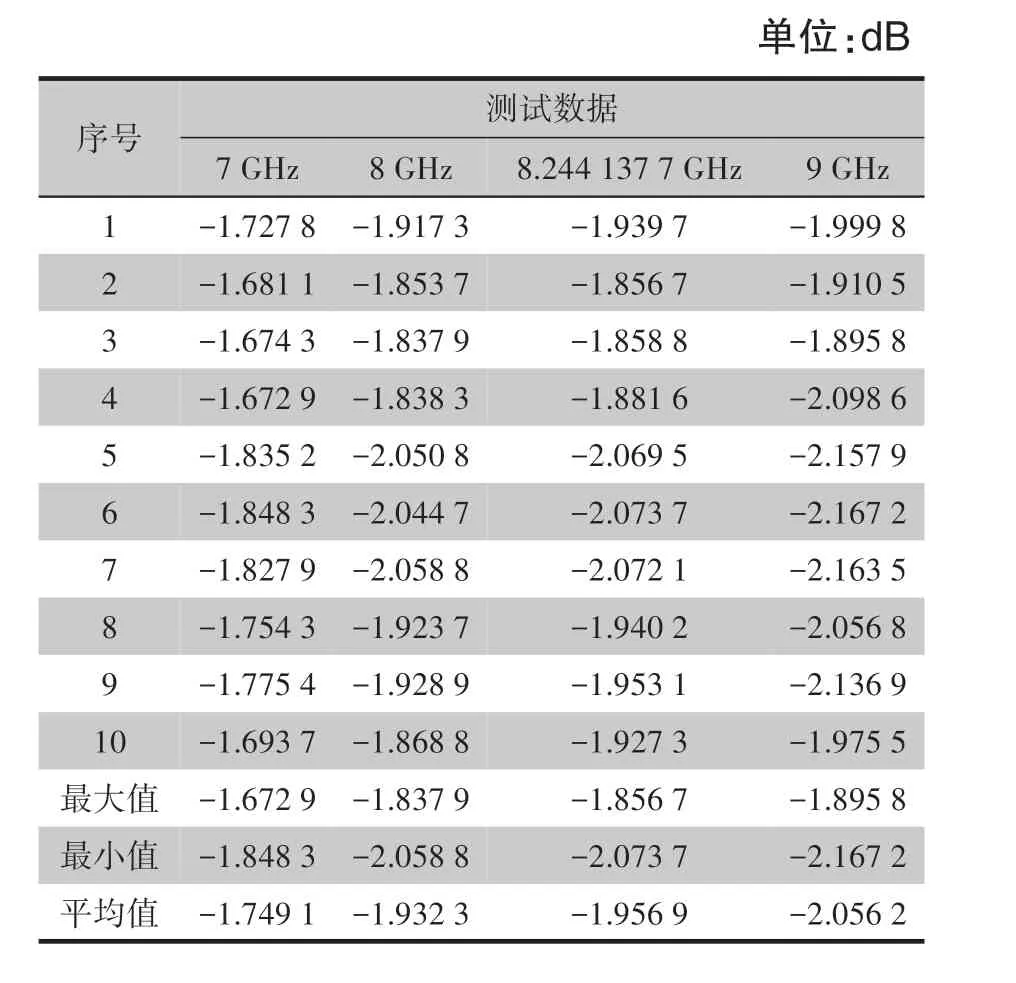

表3 缩短板边插头设计方案测试数据

3.2.3 测试端地线相连形成回路方案测试数据

将接地线测试端相连形成回路减小电磁辐射、电磁干扰和避免寄生电容形成串扰,提升信号传输质量,从而提高整个系统运行的稳定性,设计方案如图3(c)所示。

测试端地线相连形成回路设计方案插入损耗测试如图6 和表4 所示。由图6 和表4 可见,原在8.244 137 7 GHz 频点的谐振消失了,测试数据恢复正常,损耗波形更加平滑。

图6 测试端地线相连形成回路方案插入损耗测试

表4 测试端地线相连形成回路方案插入损耗测试数据

对比分析优化设计前后的插入损耗图及测试数据表明:缩短板边插头长度方案和测试端地线相连形成回路设计方案,与优化前对比,在出现谐振的8.244 137 7 GHz 频点插入损耗数据均进行有改善;测试端地线相连形成回路设计方案的插入损耗波形在7、8、9 GHz 等频点损耗波形相对缩短板边插头长度方案更加平滑,数据结果与缩短板边插头长度方案对比也更优。

3.3 信道眼图分析

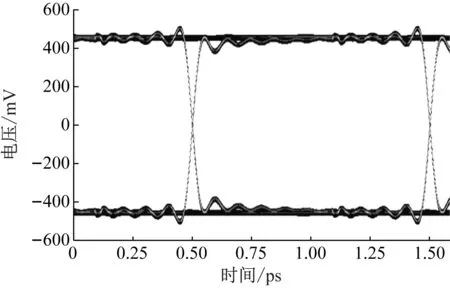

从网络分析仪中保存优化前后产品的实际测试的数据,导入仿真软件中进行信道眼图拟合观察,如图7和图8所示,同时得到信道眼图参数见表5,优化前后产品信道眼图的眼宽及眼高数据对比见表6。

图7 设计方案优化前信道眼图

图8 设计方案优化后信道眼图

表5 设计方案优化前后信道眼图参数

表6 设计方案优化前后信道眼图眼高与眼宽对比

在眼宽相同情况下,眼高数据较大抗干扰能力较强,传输质量高。由图7、图8 和表5、表6可知,2 种优化后方案均能提高信道的眼图质量,优化后2 种方案中,测试端地线相连形成回路方案比缩短板边插头设计方案的眼高数据稍大,说明测试端地线相连形成回路方案改善眼图的效果更好。

3.4 史密斯圆图对比

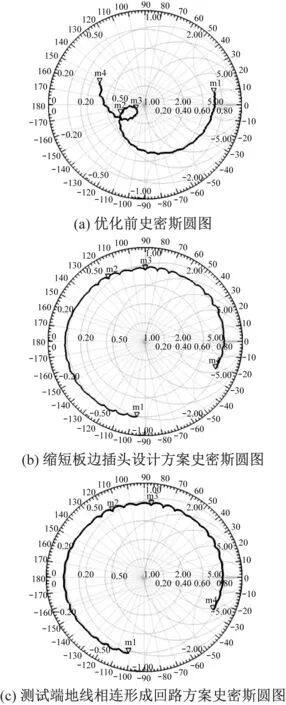

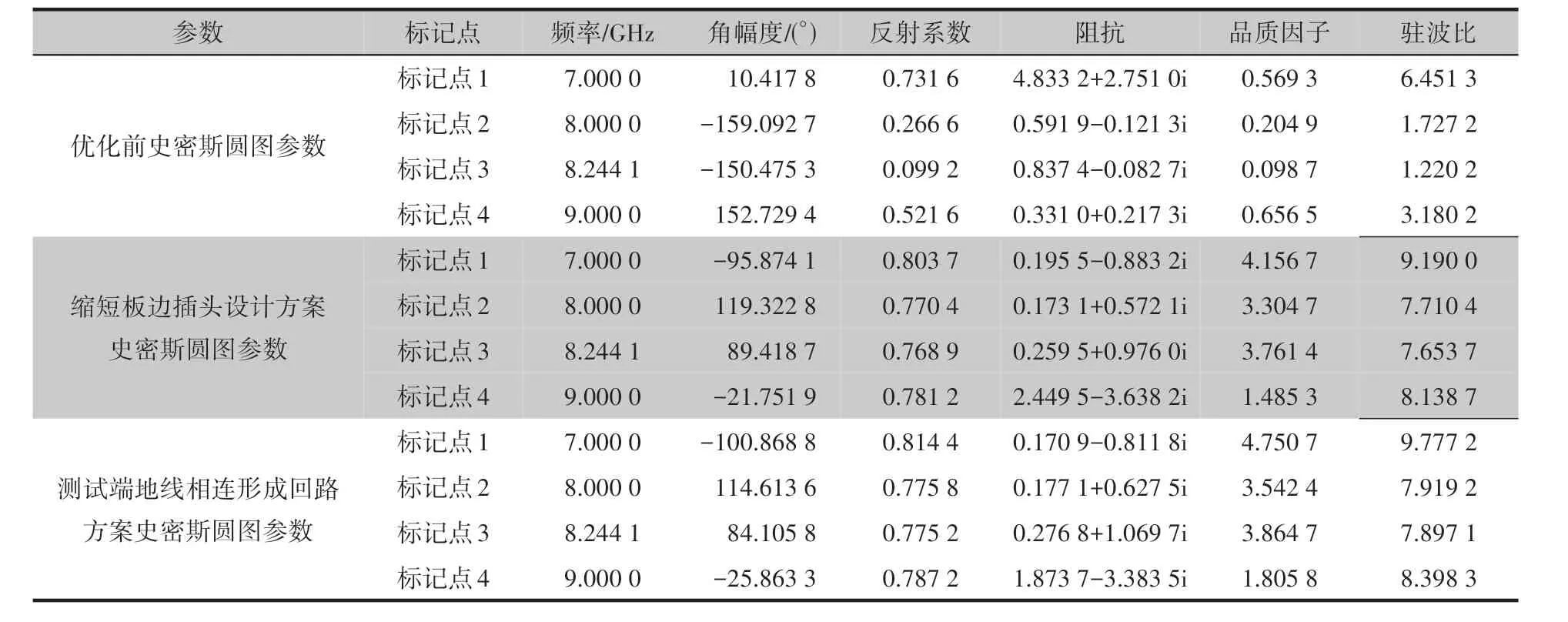

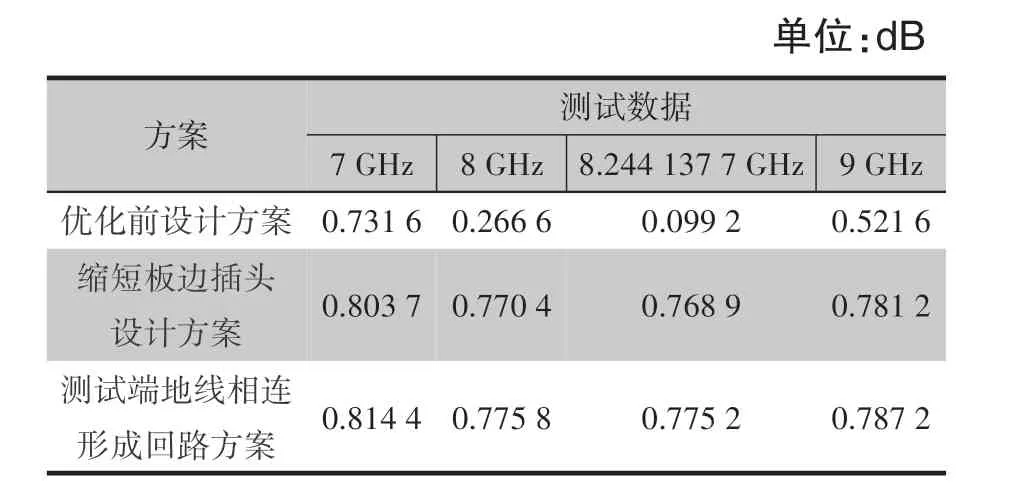

从网络分析仪中保存优化前后产品的实际测试的数据,导入仿真软件中进行插入损耗史密斯圆图拟合。史密斯圆图如图9 所示,参数见表7,三者反射系数(Γ)对比见表8。

图9 优化前后插入损耗史密斯圆图

表7 优化前后史密斯圆图参数

表8 优化前后插入损耗史密斯圆图反射系数Γ对比

在插入损耗波形出现谐振的情况下,史密斯圆图中反射系数Γ数值越小则信号反射越少,相邻线间电流的影响越大,造成信号插入损耗越多;反之在插入损耗波形平稳变化的情况下,史密斯圆图中Γ数值越大则信号反射越多,造成信号插入损耗越少。由表7可知,比较优化前后3种设计方案在不同频率的反射系数值,优化前设计方案在谐振频点处反射系数急剧下降至最低值,而优化设计后的插入损耗史密斯圆图中反射系数较为稳定。从表8 反射系数数值方面来看,测试端地线相连形成回路方案略高于缩短板边插头设计方案,说明测试端地线相连形成回路方案的改善效果要优于缩短板边插头设计方案。

4 结语

本文从串扰的形成方面分析和解决传输信号插入损耗波形出现谐振的问题。对FPCB 板边插头产品,接地线的回路设计、减少GND VIA 与板边插头接地线间的距离和缩短板边插头的长度,可以减小电磁辐射、电磁干扰及寄生电流的产生。随着高频高速电路设计更加复杂化,要求损耗越来越低,信号传输速度更快、更完整,要求电磁辐射与干扰问题在模拟设计及试样阶段就得到解决。因此,更多的电路设计需要在设计阶段就要对插入损耗进行分析、仿真模拟、实物测试、优化设计,以达到最佳设计方案。本文从串扰的发生及解决开展分析,提供了一种可行的思路,供同行参考借鉴。