基于MPSOC和HLS的图像处理算法验证系统研究

2024-03-18申俊星褚立柱

申俊星,褚立柱

(商丘职业技术学院,河南 商丘 476100)

随着机器视觉的发展,视频图像处理技术已经被广泛应用在智能手机、汽车电子、工业物联网等领域.为了全面评价图像处理算法的效果,在图像处理算法开发过程中,对算法的动态实时验证必不可少[1].ARM处理器对于实现复杂的图像处理算法有着优异的表现,而FPGA凭借流水线计算结构和重构性,可以较好实现图像实时处理和算法更新[2].MPSOC同时具备ARM和FPGA在图像处理中的优点,可以满足图像处理算法的动态验证需求.同时,高层次综合(High Level Synthesis, HLS)技术可以将高级语言转换成底层硬件描述语言,高效完成图像处理算法的硬件实现过程,以进行硬件加速,减少开发成本和时间,加速设计生产力[3].

本文设计了一种基于MPSOC和HLS的图像处理算法验证系统,通过HLS技术高效完成图像处理算法的硬件实现,以进行硬件加速,同时与图像传感器采集的图像数据进行比对,完成对图像处理算法的动态验证,同时基于LVDS设计了板间图像传输接口,通过FPGA级联为后续实现大型复杂图像处理算法的验证提供了充足的扩展空间.

1 系统架构

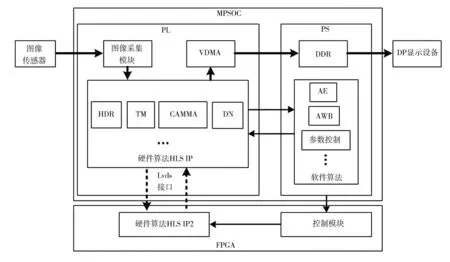

图像处理算法验证系统设计方案,如图1所示.其中,MPSOC包括PL部分中的图像采集模块、硬件算法HLS IP 和VDMA模块,以及PS部分的DDR和软件算法模块.

图1 图像处理算法验证系统架构

图像采集模块用于采集图像传感器的图像数据,并按照AXI-Stream协议将图像数据流传输给硬件算法HLS IP.硬件算法HLS IP利用HLS技术实现图像处理算法,包括HDR(High-Dynamic Range)、TM(Tone Mapping)、GAMMA、DN(denoise)等子模块.HDR算法通过多帧不同亮度图像融合,使图像拥有更高的动态范围和更多的图像细节.TM模块为色调映射,用于压缩位宽和动态范围.GAMMA模块功能是对图像做非线性变换,主要用于协调自然亮度和主观灰阶感受的.DN模块的主要作用是图像降噪.为了满足不同应用的需求,可根据系统功能灵活调整不同子模块进行互相串联,实现硬件算法HLS IP整体功能的改变,同时通过AXI-Lite协议建立该模块与PS端的连接,PS端可根据软件算法或用户需要发送指令,控制和调整各硬件算法子模块的参数.VDMA模块在PS的控制下完成图像数据流在PL和PS中DDR的交互,同时通过VDMA模块内部的GenLock锁帧机制实现图像处理和图像显示两侧的帧率匹配,且保证显示图像不撕裂和不分层.最后,DDR中的图像数据直接从PS端送至DP显示设备上显示.

PS中的软件算法一般用来实现较为灵活、易于调整、需要调试的算法,如AE算法中的场景识别、曝光策略、AWB算法中的色温估计和增益计算等,也可以根据硬件资源和用户需求灵活调整,为了满足实时性要求,PS中的软件算法不宜过于复杂,只需通过参数策略实现对其他硬件算法IP的参数计算和调整,不对图像数据流进行处理.

当验证大型复杂图像处理算法IP时,单板MPSOC的资源可能无法满足需求.因此,为了实现图像数据流板间传输,设计了板间互联LVDS接口,该接口具有很好的可拓展性.级联的FPGA包括硬件算法HLSIP2及其控制模块,硬件算法HLS IP2可根据系统功能和应用需求灵活调整.控制模块用于接收MPSOC中PS 的指令,进而将参数传递给硬件算法HLS IP2.

1.1 HLS实现硬件算法加速

开源计算机视觉(OpenCV)被广泛应用于开发计算机视觉应用,使用XILINX公司的HLS高级语言综合工具,可以快速实现从OpenCV图像处理设计到RTL代码的转换,并直接在FPGA上实现实时图像处理.HLS将OpenCV函数库转化成可综合的HLS视频库,该视频库与OpenCV具有类似的接口和算法,比如与Mat相对应的xf::cv::Mat数据类型,被用于模型化视频像素流处理.HLS视频库主要针对FPGA架构,实现了专门面向FPGA的优化,比如定点运算、行缓存(line buffer)和窗口缓存(window buffer)等[4].

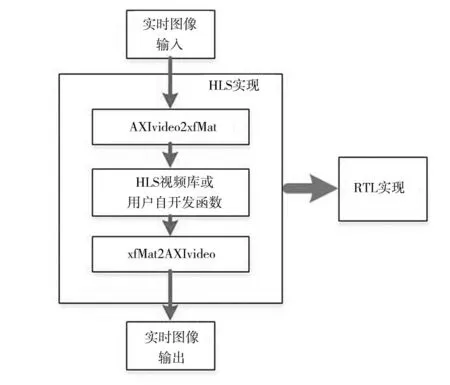

HLS对图像处理算法硬件实现的过程,如图2所示,实时图像输入采用AXI4-stream协议.HLS在实现图像算法时,首先将图像数据转换成Mat数据类型,然后通过HLS视频库或者用户自开发功能函数实现图像处理功能,最后再转换成AXI4-stream协议接口.图像算法实现完成后,通过HLS工具进行仿真和综合,最终生成RTL IP.

图2 HLS实现图像算法框图

1.2 板间互联LVDS接口

为了验证大型图像处理算法IP,设计了板间互联LVDS接口,从而实现图像数据流板间传输,避免了资源的限制.LVDS板间互联接口单向传输过程,如图3所示.图像数据流先通过AXI4-Stream to Video Out IP转换成video DVP接口,然后采用Xilinx官方High Speed SelectIO IP实现并串转换LVDS传输,包括发送端TX和接收端RX,此IP在native mode下使用BITSLICE逻辑组件,内部增加了很多专用路由,可以支持单通道最高1600 Mbps的数据传输.对于RGB24bit数据,串化因子4,采用7对LVDS接口即可完成LVDS板间传输,可以支持4K30fps的图像.

图3 LVDS板间传输接口结构

2 系统测试和结果分析

本文用包含Arm Cortex©-A53 64-bit 四核处理器和Cortex-R5双核实时处理器的Zynq UltraScale+ XCZU9EG MPSoC开发板作为测试平台,以三星的S5K4AC作为图像传感器,该图像传感器为大小双Pixel阵列,支持有效分辨率1280×960三帧输出,支持4lane MIPI输出.在此基础上,分别对算法效果、算法硬件加速效果和LVDS板间互联接口进行测试.

2.1 HLS算法效果测试

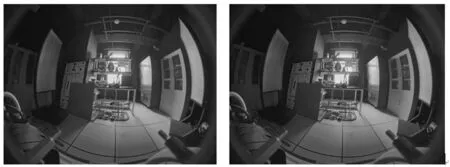

本文中图像处理以HDR算法为例,验证该算法IP的效果.HDR(High-Dynamic Range)算法通过多帧不同亮度图像融合,使图像拥有更高的动态范围和更多的图像细节.本次测试分别用HLS工具实现HDR算法和用软件实现HDR算法2种方法,测试算法效果,如图4所示,测试表明,HLS工具实现的HDR算法与软件实现的HDR算法处理效果相同,图像处理算法的HLS硬件实现方法可以完全复现软件算法的效果.该验证系统对图像处理算法有良好的验证效果.

(a)HLS实现HDR算法 (b)软件实现HDR算法

2.2 算法硬件加速测试

为了测试IP验证系统的硬件加速效果,分别在验证系统中用HLS工具实现HDR模块、TM模块、GAMMA模块、DN模块等不同子模块和用软件独立实现上述模块,测试其各自完成一帧图像处理过程所消耗的时间并进行对比,测试结果,如表1所示.验证系统的输入图像帧率为30 帧/秒,在验证系统中用HLS实现算法每帧处理时间均在33 ms以内,与原始帧率相同,具有很好的实时性,而软件独立实现算法每帧耗时较长,且随着算法复杂度增加,算法处理耗时也迅速增加.通过对比发现,HLS算法硬件加速效果明显.

表1 图像处理算法每帧耗时测试

2.3 LVDS板间互联接口测试

为了测试LVDS板间互联接口速率,利用图像传感器输出1280x960@30fps图像数据,在验证系统中增加scaler模块,用于对图像进行缩放.Scaler模块使用Xilinx官方IP Video Processor Subsystem中的scaler功能实现,将输入图像画幅放大为4K@30fps.采用14对差分LVDS接口完成双向RGB24bit图像数据传输,根据帧率计算得到LVDS单通道速率配置为1200 M即可满足要求.采用VU440开发板作为级联FPGA,分别测试不级联FPGA和级联FPGA时的图像显示效果,测试结果,如图5所示.测试结果表明,LVDS板间互联接口传输4K@30fps图像,其图像显示效果正常,与未级联FPGA时效果相同,同时快速移动画面时图像并无撕裂或卡顿,可以证明LVDS板间互联接口可以支持4K@30fps图像传输.

3 结语

本文设计了一种针对各种图像算法IP的验证系统,通过HLS技术高效完成图像处理算法的硬件加速,并实时动态完成图像处理算法的验证.同时,设计了基于LVDS的板间图像传输接口,为后续实现大型复杂图像处理算法的验证提供了充足的扩展空间.测试结果表明,该系统对图像处理算法加速效果明显,具有很好的实时性,可以较好支持图像处理算法的动态实时验证;同时验证了LVDS板间传输接口可以支持4K30fps图像的传输,满足后续验证系统扩展的带宽要求.