基于CPLD 的交换机电源时序研究

2024-03-11徐健吴海青包佳立谈广旭

徐健,吴海青,包佳立,谈广旭

(南京林业大学信息科学技术学院,江苏南京 210037)

交换机的发展从二层交换机到三层交换机再到多层多业务交换机,交换机逐渐成为当下重要的网络设备之一[1-2]。以太网交换机的运用场景非常广泛,可以运用于轨道交通、工厂自动化以及物联网通信等[3-4]。随着软件定义网络(即SDN)的出现[5-6],将网络智能集中到控制器来提高灵活性,促进网络自动化[7],交换机的硬件设计也更加复杂。

交换机设计中采用国产安路CPLD 来控制FPGA 芯片、主控CPU 和高性能的可编程交换芯片的上电时序。电源模块关系到交换机能否正常工作,复杂的集成电路芯片为降低功耗和提高运行速度,对供电电源的电压精度要求高。大多数芯片还采用低电压多电平分散供电,且对各电源的上电顺序和各电源间上电间隔时间也有明确的要求[8]。传统的上电时序由时序控制延迟电路来实现,容易受外界环境的影响(如温度等),并且一旦硬件设计完成后不能进行时序的修改,缺少灵活性。采用CPLD 设计的上电时序控制更便于集成,在上电启动速度、功耗和抗干扰方面都更具有优势[9]。

在CPLD 的逻辑软件设计中,使用Verilog HDL语言的状态机编程[10-11],实现多模块多电源的时序控制。上电时序控制的逻辑设计采用安路EL3F15 芯片,并使用安路TD4.6.5 进行编译综合,Modelsim 10.5b 软件进行仿真[12],最终进行板上验证。

1 电源芯片工作原理

电源芯片采用DC-DC 电源控制器,如图1 所示,顶部反馈电阻(RFB1)和底部反馈电阻(RFB2)通过分压来调节输出电压(Vo),反馈电容(Cff)与RFB1并联,以提供额外的相位升压并改善瞬态负载响应。使能引脚(EN)用来打开和关闭IC。电源良好状态输出引脚(PG)为漏极开路。将上拉电阻器从该引脚连接到VCC/LDO 或外部偏置电压。EN 引脚连接到CPLD 的output,由CPLD 来引导芯片工作;PG 引脚连接到CPLD 的input,CPLD 接收到电源正常工作后进行下一步操作。

图1 电源芯片原理图

功率级的输入电压(PVin)在4.3~17 V 之间,外部提供的输入电压为12 V,精确参考电压为0.6 V(±0.5%),通过将外部电阻从TON/MODE 引脚接地的方法,提供了从600 kHz 到2 MHz 的八个可编程开关频率(fsw)。根据选定的fsw,为给定的输入电压(PVin)和输出电压(Vo)生成相应的控制FET 的导通时间,如式(1)所示:

其中,fsw是所需的开关频率。在操作过程中,电源芯片监测PVin和Vo,并且自动调整开启时间,来保持预先选择的fsw。随着负载电流的增加,开关频率可以增加以补偿功率损耗。默认fsw为800 kHz。

输出电压(Vo)的大小可以通过外部分压器设定。将FB 电压与0.6 V 的内部参考电压进行比较。当输出处于其期望值时,FB 引脚处进行分压提供0.6 V。反馈电阻分压的计算如式(2)所示:

如式(3)所示,可用于帮助选择Cff和RFB1。Cff的值为100 pF 或更高,以最小化电路寄生电容的影响,其中Lo和Co组成降压调节器的输出LC 滤波器。

表1 列出了一些常见输出建议的反馈系数(m)。Cff和RFB1可以在瞬态负载测试的基础上进一步优化。

表1 反馈系数选项

2 上电时序硬件设计

在整板的设计中,系统分为多个模块,分别为主控CPU 模块、交换芯片模块和FPGA 模块。不同模块的供电电压和上电时序不同,同一模块中也有严格的上电时序要求,混乱的上电时序会使得器件损坏。电路板内部存在着多电源的供电,如3.3 V、1.8 V、1.2 V、0.9 V 等,从开机上电、内核上电(CPU、FPGA、交换芯片)、IO 上电,整个上电的过程都有严格的时序控制,这个控制上电的先后顺序就是上电时序。

整板的设计通过两个PSU 电源直接连上主板,采用均流电路接法产生的输入电压12 V,DC-DC 电源芯片同时将12 V 转5 V 和12 V 转3.3 V 作为一级电。二级电通过DC-DC、LDO 电源芯片将12 V 转为各模块所需的电压。为避免混乱的上电时序对器件造成不可挽回的损坏,要对各模块上电时序进行评估设计。

2.1 CPU模块时序设计

首先评估主控CPU 的上电时序。如图2 所示,CPU 模块采用ATX 时 序,通过PWR_BTN 按键来启动二级电,按键低电平信号不低于16 ms。二级电VDD12V 供电后产生PSON 低信号传送给CPLD。CPU12V 的硬件设计将VDD12V 接到MOSFET 的漏极,栅极接CPLD 的IO 端来控制供电。等待FPGA、交换芯片的电源全部供电后,CPLD 传送PWR_OK上电完成信号给CPU 模块,供电时间需要大于100 ms,用于其他模块电源的上电准备。在所有电源供电前,各模块处于复位状态,CPU 接收到PWR_OK 信号后通过CB_RESET 信号结束复位。

图2 主控CPU的上电时序

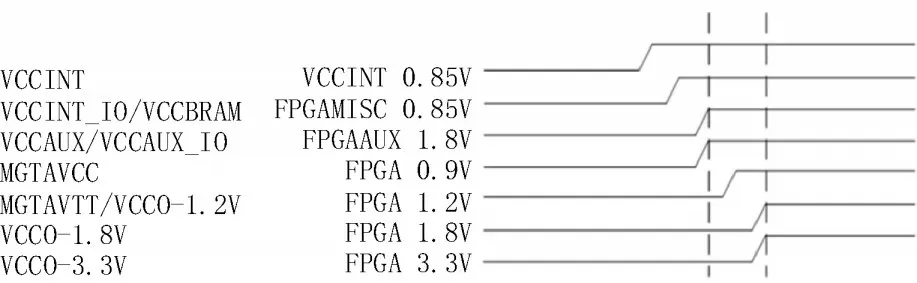

2.2 FPGA模块时序设计

FPGA 芯片采用Xilinx Zynq UltraScale+系列,分为PS 和PL 两部分,每部分都有单独的上电时序要求。根据Xilinx 官方文档,PS 部分的低功耗域(LPD)供电要早于或者与全功耗域(FPD)同时上电。通过CPLD 实现对FPGA 的多重电源配置[13],如图3 所示,将电压相同并且可以同时上电的供电端使用一块电源芯片,可以节约成本并且简化CPLD 的逻辑代码设计,例如VCCINT_IO,VCCBRAM 都是0.85 V 供电且可以同时供电。在FPGA 的启动过程中首先给逻辑内核(VCCINT)供电[14],其次再给高速收发器部分(MGT)供电,最后给IO 端(VCCO)供电。

图3 FPGA的上电时序

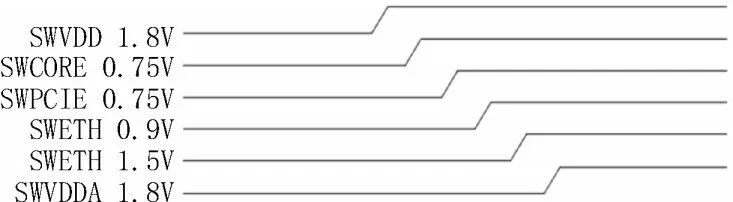

2.3 交换芯片模块时序设计

可编程交换芯片使用到PCIe、以太网高速接口收发数据包,并使用P4 语言对数据包处理系统进行编程,旨在对数据包转发设备的数据平面进行编程[15]。交换芯片的上电时序如图4 所示,交换芯片上电顺序为SWVDD 1.8 V、SWCORE 0.75 V、SWPCIE 0.75 V、SWETH0.9V、SWETH 1.5 V、SWVDDA 1.8 V。交换芯片启动前需要给VDD、内核供电;PCIe 接口的使用 由SWPCIE 0.75 V 供 电;SWETH 0.75 V 和SWETH 0.9 V 供以太网接口的使用;最后SWVDD 1.8 V 为PCIe、以太网、PLL 和片上传感器提供1.8 V的模拟电源。

图4 可编程交换芯片的上电时序

3 上电时序逻辑设计

CPLD 采用安路ELF3 系列EF3L15 芯片,EF3L15的输入输出缓冲器(I/O Buffer)划分为六个组,支持单端和双端的多种电平标准LVTTL,LVCMOS(3.3/2.5/1.8/1.2 V)[16]。上电快速启动,可控制系统的上电、复位时序,很好地实现了多电源时序控制。

3.1 电源工作流程图设计

交换机的电源分为一级电和二级电,插上PSU电源后,由电源将220 V 转为12 V。VSB3.3 V 和VSB5 V 用于交换机的待机状态,上述为交换机的一级电。二级电通过短按PWR_BTN 按钮进行上电,二级电的电源由第2 节模块中的多电源组成,通过编写状态机(FSM)完成上电时序的控制,电源工作流程如图5 所示。

当检测到所有电源芯片正常工作后由CPU 的CB_RESET 信号去结束所有复位;若有电源芯片未正常工作将重新执行状态机,到此完成交换机的上电。

3.2 上电时序设计

使用Verilog 语言编程实现交换机中多电源的时序控制。DC-DC 和LDO 电源芯片通过EN 引脚来使能电源芯片的输出,PG 引脚作为供电电路正常工作信号输出。CPLD 发送EN 信号来驱动电源芯片,接收PG 信号确保电源芯片正常工作,从而达到精确的上电控制。CPLD 接收到所有电源芯片的PG 信号后结束外部复位。状态机模块的状态设计如图6所示。

图6 上电时序状态图

状态机一共分为12 个状态,如表2 所示,Sby、SbyEnd 分别代表待机状态和复位结束等待开机状态,RST 是低电平有效的复位信号,RST 在一级电上电前保持低电平,在硬件中设计看门狗延迟电路,一级电上电200 ms 后拉高RST 信号结束复位,此时状态机Sby 接收到RST 复位结束信号后跳转到SbyEnd;PWR_ON 通过电源按键得到一个有效的高电平信号,状态机接收到该信号后跳转到PSOn,该状态下产生用于开机的CPU12V,CPU12V供电完成后通过PSU_OK 的有效高电平信号进入ATX 状态代表PSU 电源ATX 时序的结束。S1-S5五个状态用于二级电的上电,在这五个状态下,一旦接收到复位信号(!RST)或者关机信号(PWR_OFF),状态都将跳转到Sby,关机信号通过长按PWR_BTN按钮4 s 实现。当所有电源芯片的PG 信号相与后为高,状态机跳转到ALLPWR 状态,此状态代表所有电源芯片有效输出且工作正常,并将ALLPG 信号去点亮一个LED 灯,可以通过LED 灯的点亮或熄灭判别电源是否正常工作。CB_RESET 作为状态机的最后一个状态,输出Peripheral_Reset_n 信号,通过顶层调用该信号来结束其他模块的复位。状态机的设计使得电源芯片在对应的状态下完成上电,某个状态上电完成后就会自动跳转到下一个状态,这种状态机的设计灵活性高且修改方便,只需要在顶层中修改调用代码即可实现上电时序的调整。

表2 上电时序状态表

4 逻辑设计仿真

按照上述逻辑设计上电时序,在上板调试之前,采用了Modelsim10.5b 仿真软件对延迟模块、FSM 状态机模块进行了仿真,确保逻辑正确来避免上电风险。

4.1 延迟模块仿真

延迟模块的仿真图如图7 所示,该模块可以被状态机模块调用实现延迟功能。i_clk 采用32k 时钟频率进行仿真;i_rst_n 为低电平有效的复位信号;i_cnt_en 为计数器计数的使能信号;i_data 为设置延迟的时间,单位为ms;o_delay_time 为延迟信号标志,初始为低电平信号,在满足延迟时间后变为高电平;cs_dly_cnt 和ns_dly_cnt 为倒数计数器,用于计时。测试仿 真将延 时设为5 ms,即i_data=12′d5,cs_dly_cnt 和ns_dly_cnt 从17’d160 在时钟上升沿递减到17’d0。根据仿真结果,在i_rst_n 和i_cnt_en 上升为高电平后,经过5 ms 延迟o_delay_time 信号由低到高,实现了毫秒级延迟,仿真结果正确。

图7 延迟模块仿真图

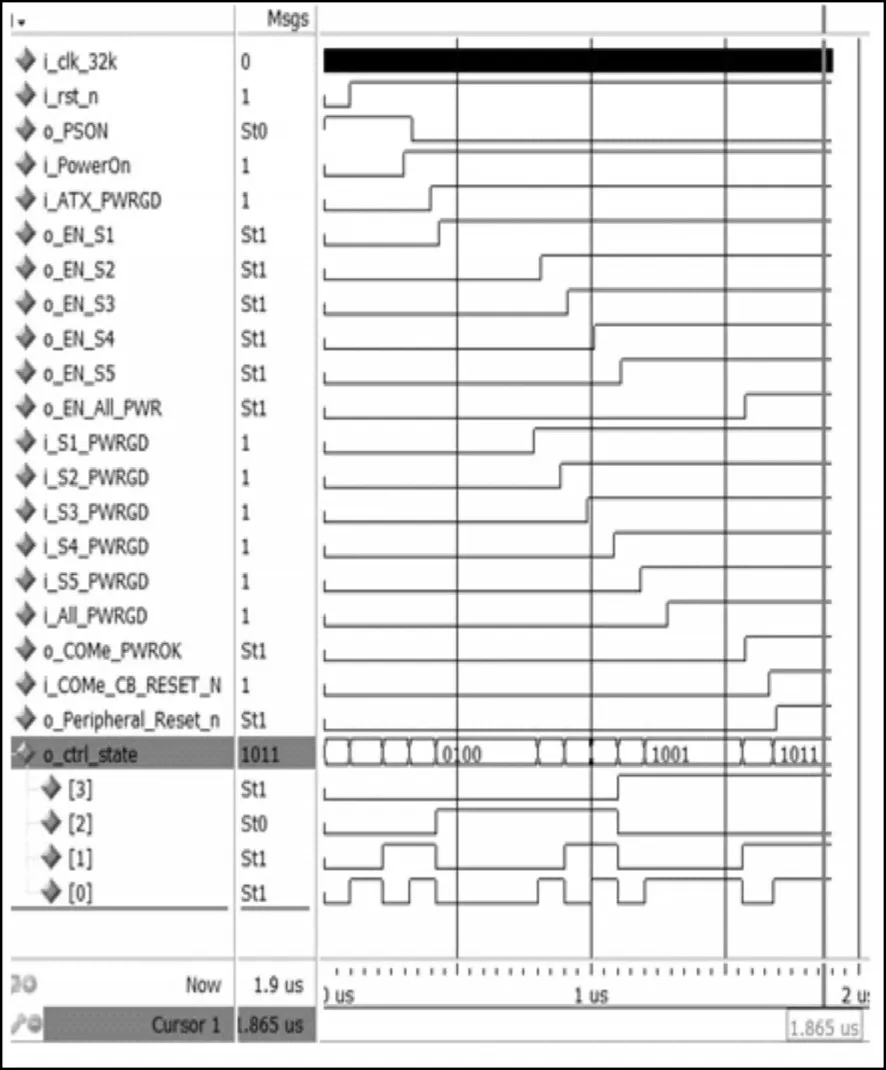

4.2 上电时序仿真

上电时序仿真如图8 所示,在接收到PSON 低信号和ATXPG 高信号后进入到S1-S5 状态的上电。接收到ATXPG 后产生EN_S1 使能信号来引导电源芯片工作,等待S1 状态下的电源芯片正常工作产生的PG 信号后,状态跳转到S2 状态并产生EN_S2 使能信号。随着状态机的状态从S1 到S5 的逐步跳转,S1_PWRGD~S5_PWRGD 依次被S1_EN~S5_EN 信号拉高,代表二级电的上电完成。最后所有电源供电后通过ALL_PWRGD 信号到主控CPU,CPU 发送CB_RESET 信号结束复位,同时Peripheral_Reset_n信号也被拉高。通过观察仿真图o_ctrl_state 信号对应的状态跳转,状态机的状态从0000-1011 依次跳转,验证了逻辑代码设计的正确,确保了上板调试的安全性。

图8 上电时序仿真图

5 结束语

基于国产安路EL3F15 芯片,对交换机进行了上电时序控制设计,用Verilog 语言编程,对延迟模块和上电时序的状态机模块进行设计,通过Modelsim进行仿真,验证了所设计的代码满足各模块的时序要求,同时也保证了上电的安全性。这种基于CPLD的上电时序控制相对传统的硬件延迟电路,不仅外围电路结构简单、抗干扰能力强,而且可以通过代码调整上电时序,灵活性高。