基于时间敏感网络的PTP 交换机技术研究

2024-03-11董昆阳武建锋

董昆阳,王 康,武建锋,3

(1.中国科学院国家授时中心,陕西 西安 710600;2.中国科学院大学,北京 100049;3.中国科学院大学电子电气与通信工程学院,北京 100049)

随着物联网、工业互联网等新兴产业的不断发展,迫切需要高精度、高稳定性的确定性网络时间服务[1]。时间敏感网络(Time Scalar Network,TSN)综合了多领域对时间敏感通信的需求,建立了时钟同步、数据调度和网络配置等核心机制,旨在构建一套高稳定性、低抖动的确定性网络时间服务系统。TSN核心协议之一精确时间同步协议(Precision Time Protocol,PTP),该协议通过硬件标记PTP 时间戳来降低系统不确定度[2],从而提供分组网络纳秒级别的同步精度。但目前国内基于TSN 的PTP 交换机系统的相关设计成果较少。因此,为进一步降低时间同步延迟和抖动,设计了基于TSN 的PTP 交换机的时间同步系统。

1 时间同步模型设计

精确时间同步的核心原理是主从时钟之间的报文传输分析与本地时钟校正,主时钟生成PTP 报文并传递至从时钟,从时钟提取报文时戳信息进而进行本地时钟校正,主从时钟同步交互模型如图1所示。

主从时钟之间的主要延时误差来自于不确定的链路延迟和交换机、时钟漂移等设备内部的不确定性所引起的延迟[3]。其中网络栈内部延迟误差可通过硬件辅助标记时间戳来减小。

主从时钟之间通过报文传递来实现两者时间同步,主从时钟同步算法分析如下:

1)主端发送SYNC message,同时记录T1时刻。

2)从端收到该报文并标记T2时刻。

3)主端延迟发送Follow_up 报文,该报文携带T1时戳信息。

4)从端接收Follow_up 报文并发送延迟信号报文Delay_req,同时记录发送时间T3时刻。

5)主端接收Delay_req 报文并记录到达时刻,同时向从端发送Pdelay_resp message 消息报文。

同步过程假设主端与从端的双向链路延迟对等,因此可通过以下方法计算链路延迟的平均值:

式中,D为平均时延。

2 系统整体设计

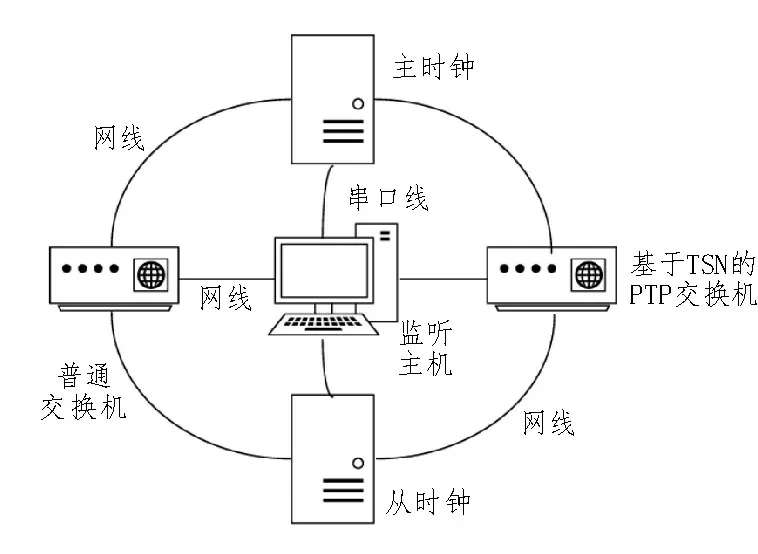

系统总体设计为时钟同步信息分别通过基于TSN 的PTP 交换机和普通交换机,OK335xS 控制PTP交换机处于目标工作状态,系统对比主从时钟接入不同交换机模式下同步误差。系统整体设计如图2所示。

图2 系统整体设计图

该设计共分为三大模块,分别为主动控制模块、交换机处理模块和GNSS 处理模块。主动控制模块使用OK335xS 开发板控制,控制交换机的工作状态。GNSS 处理模块负责以太网时间同步帧的收发,进行主从时钟之间时钟抖动和延迟分析处理。在工作模式下,从端根据与主端之间的时钟差信息来进行本地时钟修正。交换机处理模块分别采用普通交换机和PTP 交换机。普通交换机为常见的网络交换机,该交换机作为对照试验组。PTP 交换机为MICROCHIP 公司生产的EVB-KSZ9477S 系列交换机,该交换机作为网络通信PHY 芯片为系统提供硬件级时间戳标记服务。

由于EVB-KSZ9477S 开发板自身限制不利于工程的具体设计,因此该设计使用OK335xS 开发板来辅助控制KSZ9477 芯片,来提供更高的可拓展性。OK335xS 开发板通过SPI 总线进行控制和数据交换。OK335xS 主控模块通过控制KSZ9477 芯片的寄存器读写,实现对整个时钟同步系统设计模式的控制。

3 系统软件设计

在网络协议栈和PTP 初始化之后,系统根据BMI 算法判别最佳主时钟。主时钟定时发送时间同步报文到从时钟进行本地时钟修正。时钟修正模型如图3 所示。

图3 时钟修正模型图

在接入普通交换机模式下,主时钟在应用层产生PTP 报文,通过网络协议栈逐层封装后与从时钟进行通信。该模式下PTP 报文时间戳在数据链路层由系统进行软件级时间戳标记,从时钟捕获该报文并由报头协议解析出该报文所携带的时间信息。此后,从时钟根据时钟校验信息进行本地时钟校正。该传输方式会受到网络协议栈的影响,因而导致同步精度较低。

在主从时钟之间接入PTP 交换机模式下,在物理层由KSZ9477 芯片将时戳信息标记于该报文之上,该模式下交换机在物理层自动进行硬件级报文打戳,由于无需考虑网络栈内部的延迟与不确定性,故该模式下交换机具有极高的稳定性和较低的时间同步误差。

4 系统硬件设计

系统硬件设计为系统三个主要模块的硬件设计分析。分别为基于OK335xS 的主动控制模块设计、基于KSZ9477 的PTP 交换机模块设计、基于自研模块的GNSS 处理器设计。

4.1 主动控制模块

主动控制模块采用OK335xS 开发板,该设计使用该开发板的SPI 串行数据总线。SPI 是同步数据总线,通过时钟信号来保证数据收发双方实现数据的同步。此外,还用到包括串口、LED、复位电路、时钟晶振等外围电路来进行辅助控制。SPI 接口电路如图4 所示。

图4 SPI接口电路图

该设计SPI 传输采用SPI MODE0 模式,设置CPOL 和CPHA 均为0,该模式下时钟空闲时为低电平,在时钟第一个跳变沿进行数据采样。设置波特率为115 200 bit/s,停止位为1,数据位为8 bit,无奇偶校验位。

在该传输过程中,OK335xS 作为SPI 主机,EVBKSZ9477S 作为SPI 从机之一。首先,主机将连接从机对应SPI 接口片选信号CS 拉低,使得从机处于可接收状态;从机检测到时钟边缘信号时,读取MOSI线上大小为1 bit 的数据;MOSI 线根据时钟信号将数据分位发送至从机;主机传送完毕之后,继续发送时钟信号,以便从机可以将数据通过MISO 线发送至主机。此后,主机拉高从机对应的片选信号CS,从机进入停止态。至此,主机与从机完成一次数据通信。

4.2 交换机模块

交换机芯片分别为PTP 交换机EVB-KSZ9477S和普通交换机HELL-TEK 交换机,支持自动时差修正,支持对本地时钟粗调或细调。同时该处理芯片具有以下特性:

1)提供IEEE 1588v2 参考时间,支持寄存器读写操作。

2)自动硬件标记PTP 时间戳。

3)支持对时钟进行相位和频率同步。

5 实验测试与结果分析

实验测试结果分为两种,即主从时钟之间接入普通交换机模式和接入PTP 交换机模式,两种模式下控制变量时钟源、温度、湿度、线路接头数量和线路长短等影响因子不变,观察两种模式下主从时钟同步相对误差大小。测试主机通过串口、网线等与交换机模块和主从时钟之间相连,并通过串口助手Mobaxterm 进行数据截留和通过WIRESHARK 进行数据抓包分析,之后采用MATLAB 进行数据处理分析。测试架构图如图5 所示。

图5 实验测试架构图

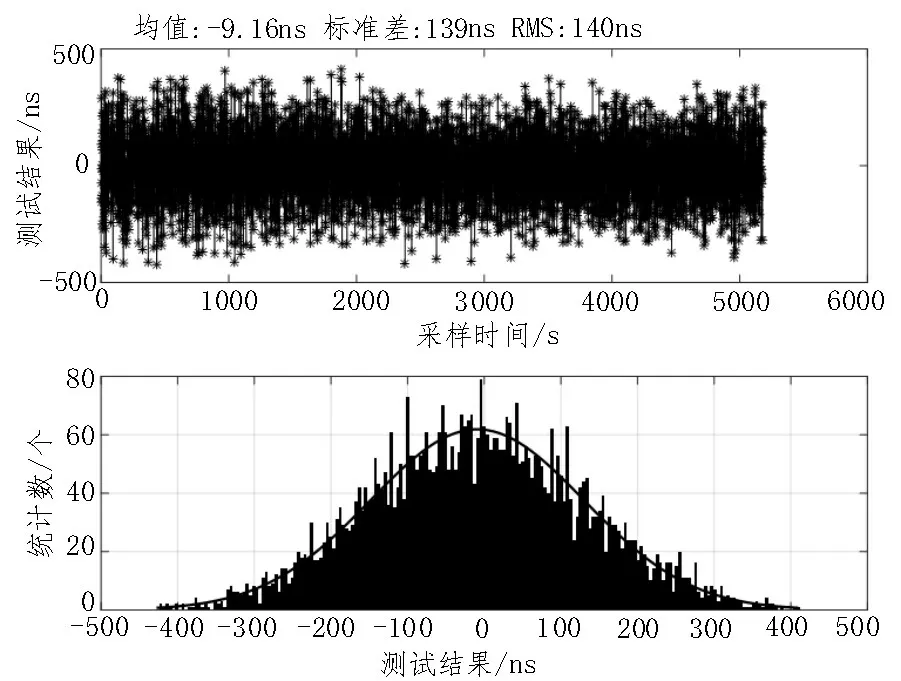

5.1 主从时钟接入普通交换机模式

在该模式下,时钟同步周期设置为1 s,主时钟定时(1 s/次)发送同步报文至从时钟。测试结果如图6 所示。

图6 普通交换机抖动数据图

如图6 所示,在主从时钟之间接入普通交换机时,同步抖动均值为-9.16 ns,标准差为139 ns,RMS为140 ns。

5.2 主从时钟接入PTP交换机模式

在该模式下,主从时钟之间接入PTP 交换机,时间同步周期设置为1 s,实验结果如图7 所示。

图7 基于TSN的PTP交换机抖动数据图

如图7 所示,在主从时钟之间接入基于TSN 的PTP 交换机,主从时钟同步偏差均值为-0.081 4 ns,标准差为3.33 ns,RMS 为3.33 ns。

5.3 实验结果分析

实验数据表明,在主从时钟之间接入基于TSN的PTP 交换机相较于接入普通交换机,同步偏差大幅减小,抖动大幅降低。

6 结束语

该文设计了时间同步测试平台,分为两种模式测试,分别为主从时钟之间接入普通交换机模式和接入基于TSN 的PTP 交换机模式。实验结果表明,相对于接入普通交换机,在主从时钟之间接入基于TSN 的PTP 交换机,在经过一定量级测试之后,时间同步抖动有较大提升,为提高系统时间同步精度提供了一种解决方案,为交换机主动控制提供了一种较为便捷的方案。