基于ZYNQ 芯片的基板管理控制器设计与实现

2024-02-28马柯帆李宝峰周悦锦武园园余永兰多瑞华

马柯帆,李宝峰,周悦锦,武园园,余永兰,多瑞华

(国防科技大学计算机学院,湖南 长沙 410073)

1 引言

基板管理控制器BMC(Board Management Controller)通常用于管理含有多个大型处理器的服务器主板。主流的BMC可以运行嵌入式Linux系统,其Linux后台运行有ipmi、redfish、web、sol等BMC常用软件,能与远程管理计算机进行网络通信,以便远程管理计算机控制和管理服务器的硬件。各主流服务器的BMC软件栈均是闭源的,彼此兼容性差,影响了数据中心设备的统一管理[1]。OpenBMC是BMC的Linux发行版,该项目是由Microsoft、Intel、IBM、Google和Facebook等数据中心公司组织创立并开源的,且已转入Linux基金会。OpenBMC使用Yocto Project作为设计编译工具,并集成OpenEmbedded、systemd、D-Bus等技术来定制管理平台。OpenBMC可以自由地添加ipmi、sol、web等BMC常用软件包,且已自动集成了RedFish,支持主板状态查看和控制,以及主板固件更新等功能。RedFish是下一代数据中心管理标准,由DMTF(Distributed Management Task Force)标准组织制定,用于替代当前的ipmi。ipmi的缺点是功能较少、可扩展性差,只适用于中小规模的数据中心管理。RedFish可扩展性好、功能丰富,针对不同供应商的种类多样的基础设施能够提供规范化易集成的管理接口,除了服务器外,RedFish也在逐渐扩展对存储、网络交换机方面的支持,可以满足超大规模数据中心的复杂管理需求。

主流的BMC芯片一般是采用Nuvoton的NPCM7xxR系列、Aspeed的ASPxxx系列服务器。主板除了BMC之外,还有一块FPGA芯片用于控制CPU的电源、复位时序。本文实现了将OpenBMC移植到Zynq-7000 All Programmable SoC芯片上,并通过扩展UART(Universal Asynchronous Receiver/Transmitter)、IIC(Inter- Integrated Circuit)等常用接口,使得芯片既可以实现BMC的功能,又可以实现FPGA的相应功能。

2 总体设计

2.1 基本架构设计

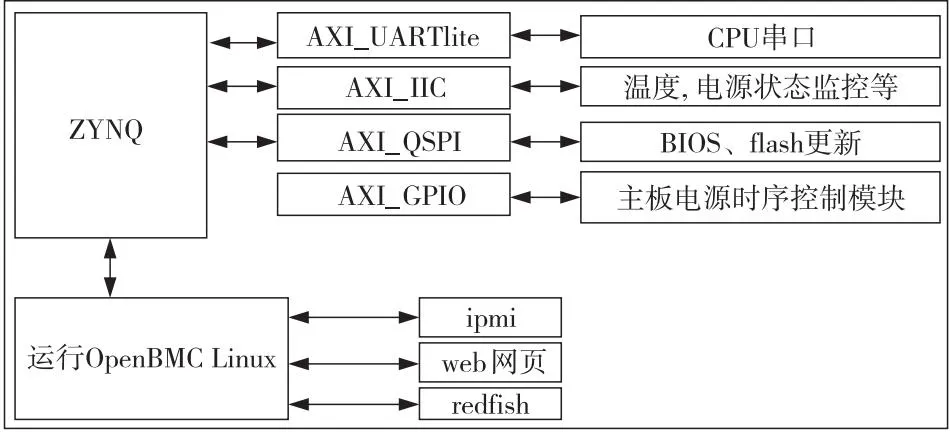

基本架构设计如图1所示,ZYNQ芯片通过AXI总线与AXI Uartlite、AXI IIC、AXI Quad SPI、AXI GPIO(General-Purpose Input/Output)等IP核相连。AXI Uartlite用于SOL(Serial Over LAN),AXI IIC用于监控主板温度以及电源芯片状态,AXI Quad SPI用于主板固件(BIOS、flash)更新,AXI GPIO用于控制主板加切电。ZYNQ芯片的ARM部分运行OpenBMC Linux,添加ipmi、web、redfish等软件,FPGA部分仍执行相应逻辑功能。

Figure 1 Basic architecture design图1 基本架构设计

2.2 核心芯片简介

ZYNQ系列异构应用处理器是XILINX在2010年发布的,该处理器将ARM Cortex-A9硬核IP与FPGA的可编程逻辑资源集成在一起,并通过ARM处理器的配置方式来启动FPGA。利用嵌入式资源同时完成图形界面、DDR3控制、用户输入等任务,可以通过FPGA资源实现并行处理,可以同时执行多个计算单元,提供高性能的解决方案。ZYNQ芯片的体系结构主要分为2部分:处理系统PS(Processing System)和可编程逻辑PL(Progarmmable Logic)。PS部分与ARM芯片架构类似,主要包括一个双核的ARM Cortex-A9处理器、片上存储器、外部存储器接口和大量的外围接口。PL部分是可编程逻辑资源,它基于XILINX 7系列FPGA,由28 mm高k金属栅极半导体技术制成。PS是系统中的主要部分,可以只使用PS,但是不可只用PL,因为PL的配置下载需要PS进行辅助。ZYNQ芯片的ARM处理器内部带有MMU(Memory Management Unit),可以运行Linux。PL和PS之间的通信主要利用AXI片上总线,XILINX提供了很多带AXI接口的IP核,可以灵活地应用于各种应用[2,3]。

2.3 开发软件介绍与选择

Vivado是XILINX公司推出的一套FPGA开发工具,集成了FPGA设计和嵌入式设计等功能,它是一个基于AMBA AXI4 互联规范、IP-XACT IP封装元数据、工具命令语言TCL(Tool Command Language)、Synopsys 系统约束SDC(Synopsys Design Constraints)的开放式开发环境[4]。

一般来说,OpenBMC Linux的UBOOT、内核、文件系统的生成以及设备树的构建有2种常规方法,即使用Petalinux或Yocto Project工具,这2种方法都可以一键得到所需文件。

Petalinux是XILINX公司推出的嵌入式Linux开发套件,包括了Linux内核、UBOOT、设备树、根文件系统、源码、库和Yocto recipes等[5],也可以让客户很方便地生成各种配置、编译及自定义Linux发行版。PetaLinux工具支持的芯片系列有Zynq UltraScale+、MPSOC(Multi-Processor System On Chip)、Zynq 7000和MicroBlaze,可与Vivado协同工作,简化了Linux系统的开发工作。

Yocto Project是一个开源协作项目,能帮助开发者为不同硬件架构的嵌入式产品制作基于Linux的定制系统。它提供了灵活的工具集和开发环境,使嵌入式设备开发人员能通过开源的软件堆栈、配置文件来定制 Linux 映像,并在多个开发者一起协作上具有优势。Yocto Project 在系统和应用程序开发、存档和管理以及系统占用和内存利用等方面都具有优势。Yocto使用BitBake工具来执行Linux构建任务。Yocto的优点有:应用广泛、支持架构多、灵活性高、软件可裁减、更新稳定以及生态系统丰富。但是,缺点是初始构建时间长、项目工作流程繁锁、技术入门难、且各版本之间存在兼容性问题等。ZYNQ芯片支持使用Yocto Project构建Linux系统,XILINX官方已经把相关代码开源到github,并且OpenBMC官方推荐的开发工具也是Yocto Project。

3 ZYNQ相关设计

3.1 ZYNQ芯片逻辑设计

ZYNQ芯片的逻辑设计主要是在Vivado开发工具上完成的。系统顶层设计如图2所示,主要包括Processor System Reset、AXI Interconnect、AXI Interrupt Controller、AXI IIC、AXI Uartlite、AXI Quad SPI、AXI GPIO、Concat等模块。

Processor System Reset是一种软IP,它提供了一种用来处理其他IP核复位信号的机制,该IP核输入端信号处理大量的复位需求,并在输出端生成适当的复位信号送给处理器,本文设计中用它来处理ZYNQ7 Processing System和带AXI接口IP核的复位信号。

AXI Interconnect用其将AXI内存映射主设备连接到AXI内存映射从设备,可配置为多个主设备接口和多个从设备接口,这些AXI设备在数据宽度、时钟域和AXI子协议(AXI4、AXI3或AXI4-Lite)方面可以不同,Vivado会执行自动推断并转换。在本文设计中,AXI Interconnect负责将ZYNQ7 Processing System主设备与各个AXI IP从设备互连起来,只需连好时钟、复位、AXI信号即可,Vivado已经将AXI信号并成一组,连接时会自动识别。

AXI Interrupt Controller用于接收来自外围设备的多个中断输入,并通过AXI总线将中断信息送入到ZYNQ7 Processing System中进行处理,可通过AXI接口访问该IP核的各个寄存器(如使能中断,应答、校验等)。当ARM端的中断资源不够用时,可用它来扩展中断。

Concat IP核可以实现位拼接功能,本文设计中用其将各个外设IP的中断信号拼接起来送到AXI Interrupt Controller。

3.2 电源时序控制模块设计

电源时序控制模块用于控制高性能服务器CPU的上电时序,此类CPU的供电需要多路电源芯片转换得到,每路电源输出都要按CPU厂商的要求进行延时。其电源时序控制模块设计及各信号定义如图3所示,POWER_ON由AXI GPIO输出的高低电平控制,当POWER_ON由高电平控制时,服务器电源使能信号CRPS_EN置为1’b1,CRPS电源就绪后会将CRPS_OK置为1’b1供FPGA判断,其余各路电源按上电时序要求进行使能和延时。

3.3 BOOT.bin文件设计

ZYNQ启动流程如图4所示。ARM加载BootROM内部程序,这个程序固化在ZYNQ内部ROM,BootROM用于将第一阶段启动程序FSBL(First Stage Boot Loader)加载到OCM(On Chip Memory),并启动FSBL。

Figure 4 Start process of ZYNQ图4 ZYNQ启动流程

顶层设计完成后可导出一个硬件描述文件。Vivado SDK工具通过解析该硬件描述文件生成FSBL代码和可执行文件。UBOOT用于加载PL bitstream和启动Linux。PL bitstream的作用是配置FPGA。编译完整个OpenBMC工程可生成u-boot.elf文件,通过Vivado SDK将u-boot.elf和FSBL,合并生成BOOT.bin文件[6],如图5所示。

Figure 5 Merging and producing BOOT.bin file图5 合并生成BOOT.bin文件

3.4 设备树源码设计及编译

设备树源码的设计需要借助Vivado SDK,编译设备树则要用到OpenBMC配套的设备树编译程序。Vivado SDK根据XILINX提供的设备树仓库来生成本文设计需要用到的设备树源码,仓库已经在XILINX的Github上开源。创建设备树版本的板级支持包后,Vivado SDK将自动构建生成pcw.dtsi、pl.dtsi、skeleton.dtsi、system-top.dts、zynq-7000.dtsi这几个设备树源码文件。其中,在system-top.dts末尾添加温度传感器lm75节点并挂在axi_iic_0下。OpenBMC整个工程构建完成后会生成设备树编译器可执行文件dtc,利用dtc可以将设备树源码编译为二进制可加载dtb格式文件。

4 OpenBMC Linux部分设计

首先是开发环境的准备。OpenBMC Linux部分设计要在Ubuntu环境下进行,并要安装好编译用到的基本工具,例如:Ubuntu 20.04、GCC version 9.4.0、Python 3.8.10。涉及到ARM的交叉编译工具不需要手动安装,Yocto Project工具会自动根据配置文件执行安装程序。

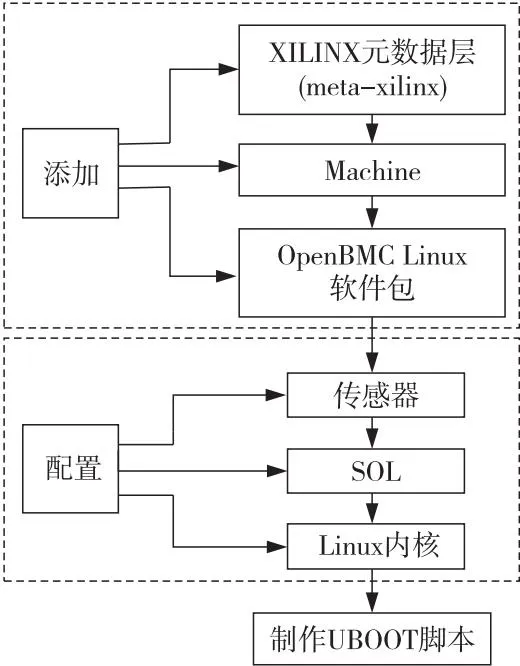

OpenBMC Linux的设计是基于官方提供的开源仓库进行修改的,其大概流程如图6所示。

Figure 6 Design flow of OpenBMC Linux图6 OpenBMC Linux设计流程

meta-xilinx里面包含了很多与硬件相关的内容,需要手动从XILINX的github仓库拉取下来,放到openbmc目录里,并确保与meta-phosphor在同一个目录。元数据包含了recipe、配置文件、构建指令的信息以及自动控制构建的方法、也包含软件版本信息及其来源、一系列补丁文件等。

添加machine之前要建立一个自己专用的层,文件名称如图7所示。其中的evb-zynq-zhou.conf就是machine配置,配置里面指定了使用的芯片的相关参数,如:机器特征、UBOOT、串行控制台、内核设备树、固件引导文件,除此之外的配置文件写法可以参考meta-evb。

本文设计需要添加ipmitool、webui-vue这2个软件包。ipmitool是一种命令行方式的 IPMI平台管理工具,通过它可以实现获取传感器的信息、显示系统日志内容、网络远程开关机等功能[7]。webui是网站用户界面(Website User Interface),可以在网页上显示服务器的各种物理特征,如温度、电压、风扇工作状态及报警信息等。

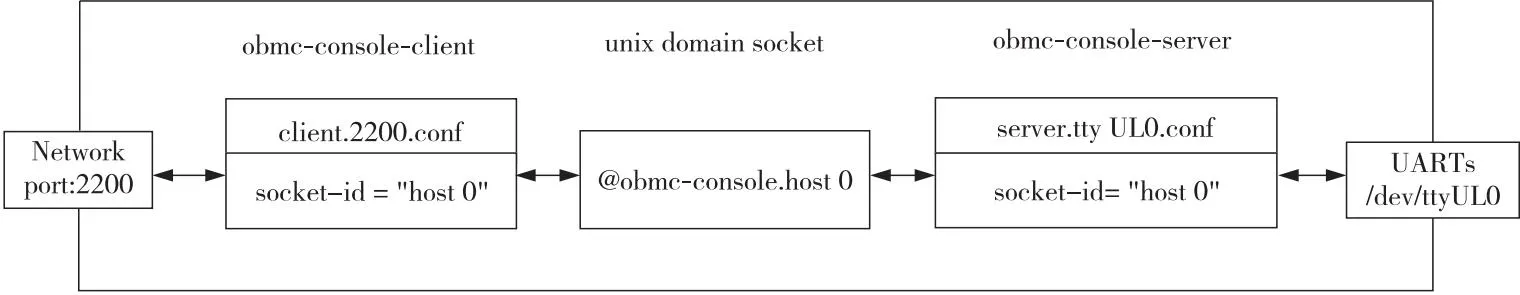

SOL是指通过网络会话来重新定向服务器CPU串口I/O的一种机制。SOL可以很好地帮助运维人员找出服务器CPU启动失败的原因,是BMC必不可少的一个功能[8]。OpenBMC中的SOL可以支持多个独立CPU串口同时工作,其主要实现原理如图8所示。配置传感器建立的文件夹、文件、文件名及结构如图9所示。

Figure 8 Implementation principle of SOL图8 SOL实现原理

Figure 9 Schematic diagram of sensor configuration files图9 传感器配置文件示意图

配置内核的目的是打开一些功能选项和增加Linux驱动,如增加ZNYQ顶层设计连接的AXI相关IP核驱动,需在内核配置片段文件(.cfg)添加以下指令:

CONFIG_XILINX_INTC=y

CONFIG_IRQCHIP_XILINX_INTC_MODULE_ SUPPORT_EXPERIMENTAL=y

CONFIG_I2C_XILINX=y

CONFIG_SERIAL_UARTLITE=y

CONFIG_SERIAL_UARTLITE_CONSOLE=y

CONFIG_SENSORS_LM75=y

为了使引导加载Linux的过程变得更灵活,需设计UBOOT可运行的scr脚本文件。新建文本文件boot_zhou.script,往文件中添加以下代码:

fatload mmc 0 0x100000 bmc_zhou.bit

fpga loadb 0 0x100000 MYMfilesize

fatload mmc 0 0x00200000 uImage

fatload mmc 0 0x00900000 zynq-zybo-z7.dtb

fatload mmc 0 0x04000000 rootfs.cpio.gz.u-boot

bootm 0x00200000 0x04000000 0x00900000

命令表示从FAT格式的SD卡的0分区加载对应的文件到相应的内存地址,再转到相应的地址启动系统。fpga loadb命令用于配置FPGA。

5 构建及运行测试

使用以下命令构建OpenBMC工程:

.setup evb-zynq-zhou

bitbake -v -DDD obmc-phosphor-image

构建完成后可在工程路径下看到生成的各个固件文件。将BOOT.bin、rootfs.cpio.gz.u-boot、uImage、zynq-zybo-z7.dtb、boot.scr复制到FAT格式的SD卡。

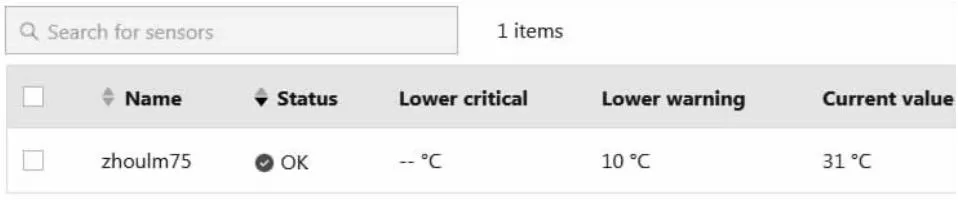

硬件测试平台如图10所示。加电并连接串口后的显示如图11所示,出现登录命令行表明OpenBMC Linux系统已经启动完毕,输入ipmitool sdr可以看到lm75温度传感器在正常工作。

Figure 10 Hardware test platform图10 硬件测试平台

将ZYNQ主板网线连至电脑,在电脑端的浏览器输入网址https://BMC IP。可以发现,Web网页能正常显示,挂在AXI IIC下的lm75温度传感器状态正常,如图12所示。

Figure 12 Web page function test图12 Web网页功能测试

为了验证SOL功能,将ZYNQ板子上已经绑定AXI Uartlite IP核的RX 引脚连到TX,保证电脑网络与ZYNQ板子相通。串口回环测试如图13所示,终端每发送一个字符都会接收到一个相同的字符。

为方便测试加电信号,将POWOR_ON信号赋值给测试点POWOR_ON_TP,ZYNQ上执行ipmi加电命令,测量POWOR_ON_TP信号引脚发现电平为高,说明电源控制正常,FPGA功能测试示意图如图14所示。

Figure 14 Schematic diagram of FPGA function test图14 FPGA功能测试示意图

6 结束语

本文提出了一种在ZYNQ芯片上实现OpenBMC的方法,介绍了从FPGA设计到OpenBMC Linux设计的整个流程。设计的OpenBMC Linux能成功编译并运行在ZYNQ芯片上,实现了温度监控、Web网页显示和 SOL等功能,可以根据不同的逻辑设计方案灵活地添加多路IIC、UART等接口,具有较高的可扩展性。本文提出的设计方案,不仅实现了传统的BMC监控管理功能,同时也具有FPGA的高并行性和可扩展性,可以一芯两用,能够极大地节省主板面积和物料成本,为高性能服务器、超算、交换机等日益严苛的设计环境提供一个理想的设计方案。