一种低回踢噪声低失调高频CMOS 比较器∗

2024-01-29王阁藩王金婵

王阁藩,刘 博,李 恺,王金婵

(河南科技大学电气工程学院,河南 洛阳 471000)

比较器是各类模数转换器及数据收发系统的关键模块,其噪声、失调和速度直接影响信号链系统的整体性能。常见的比较器可分为静态和动态比较器[1],静态比较器在复位、再生阶段都存在静态电流,导致功耗较大且速度慢;而动态比较器采用一对背靠背交叉耦合的反相器构成正反馈,具有响应速度快、静态功耗极低等优势[2-3],广泛应用于各类高速模数转换器(Analog To Digital Converter,ADC)[4-5]。

比较器的失调电压、回踢噪声等特性都对系统产生重要影响[6-7]:比较器失调电压影响数据转换精度[8];回踢噪声[9]影响动态比较器的跳变点从而降低了ADC 的线性度以及有效位数。传统的高精度比较器采用开环运放,速度较慢;而传统的高速比较器采用锁存器结构,速度快但失调电压高、回踢噪声大。在Flash ADC 这类[10]采用大量的比较器模块并高速切换的电路中,比较器的结构设计以及指标要求尤为关键。

本文提出了一种可有效抑制回踢噪声的低失调电压高频动态比较器,通过交叉电容中和技术、钟控开关箝位技术,对预放大器和锁存器两部分进行改进,有效削减了回踢噪声和失调电压。

1 双尾动态比较器

1.1 传统双尾动态比较器

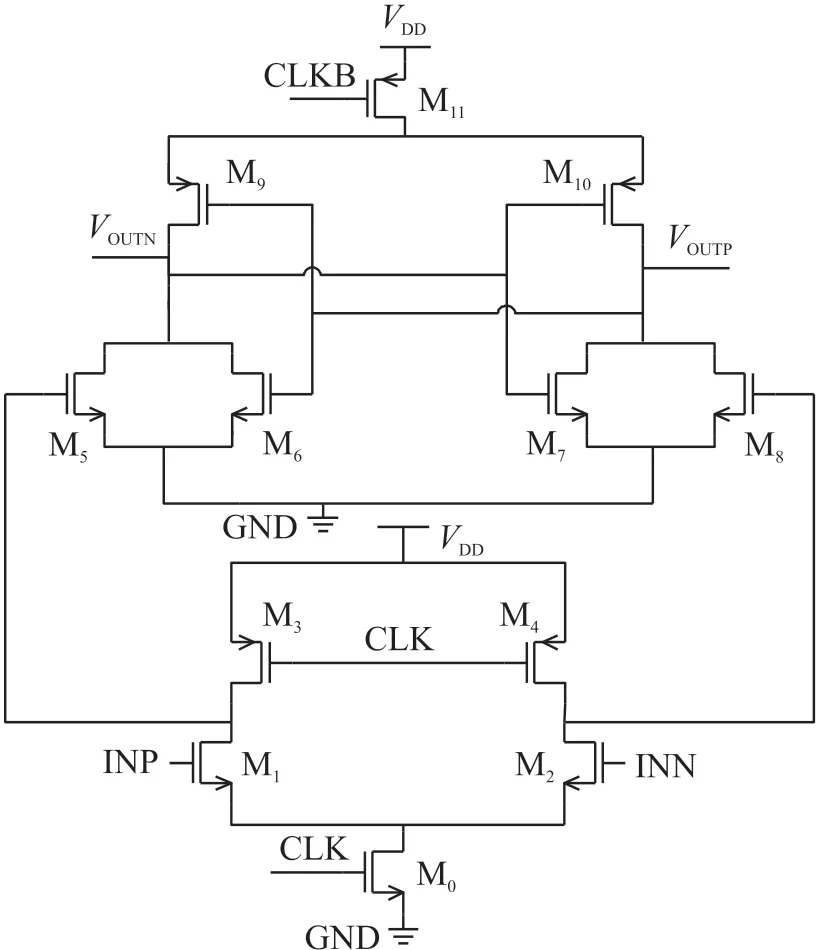

传统双尾动态比较器电路如图1 所示。复位阶段,CLK 为低电平,M3、M4导通,M5、M8将比较器的输出电压拉到零电位。

图1 传统双尾动态比较器

再生阶段,CLK 为高电平,锁存器小信号模型如图2 所示,C1、C2分别是锁存器输入端的寄生电容,gm是交叉耦合反相器MOS 管的跨导。

图2 再生阶段锁存器小信号模型

由Kirchhoff 定律对节点A、B分析可知:

电路采用对称式结构设计方法,故而对称管的gm和ro是相同的,求解式(2)可得输出节点电压VOUTN、VOUTP达到VDD/2 的用时:

式中:gm=考虑M6、M7管及各开关管器件失配问题,锁存器的输入失调电压为:

式中:ΔVTH是阈值电压的标准偏差,ΔW/W和ΔL/L分别是管子的沟道宽度、长度失配。

失调及延迟极大影响电路性能,差分双尾动态比较器可以较好地处理失调及延迟问题。

1.2 差分双尾动态比较器

差分双尾动态比较器[8]如图3 所示,在比较阶段,锁存器必须在很短的时间内检测预放大器输出,这就使得传统比较器需要高精度的CLKB 信号。

图3 差分双尾动态比较器

用PMOS 管M11、M12代替传统比较器的锁存器部分的M11,作为预充电的开关。而通过采用差分双尾结构,将CLK 和CLKB 时钟变为CLK 时钟,简化了时钟设计,可减少电源纹波等扰动,改善了延迟问题。

此外,通过添加MOS 管M13、M14,将节点Ai+和Ai-重置为零电位,两个节点电位相等,以避免Ai 节点之间电压失配导致比较器失调增大,从而消除了关于这两个节点的电压失配问题。

然而上述两种比较器分别有一定的缺点:

①传统双尾动态比较器反相时钟的设计使得时序实现和延迟问题十分影响电路性能。

②差分双尾动态比较器虽然降低了失调电压但加入了2 个新的NMOS 管M13、M14,略微增大功耗和面积。

③传统比较器和差分双尾比较器输入对管的栅极、预放大器差分输出端之间存在寄生电容,导致在输入端引入噪声影响电路性能。

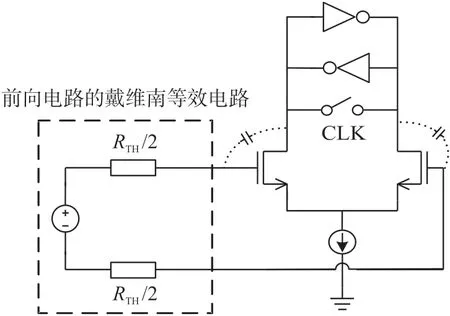

图4 为传统比较器及前项电路的简化结构。在复位阶段,输入电压决定差分对晶体管中的电流,而MOS 开关由于非零电阻将引入一个小的输出电压,使电路成为一个放大器。而再生节点上的大电压变化必然通过寄生电容耦合到输入端,引起输入对管漏极电压变化,干扰输入信号,这称为回踢噪声(Kickback Noise)。

图4 等效回踢噪声原理图

为削减回踢噪声、解决上述三个问题,本文提出了一种高频低失调低回踢噪声电路。

2 提出的双尾动态比较器

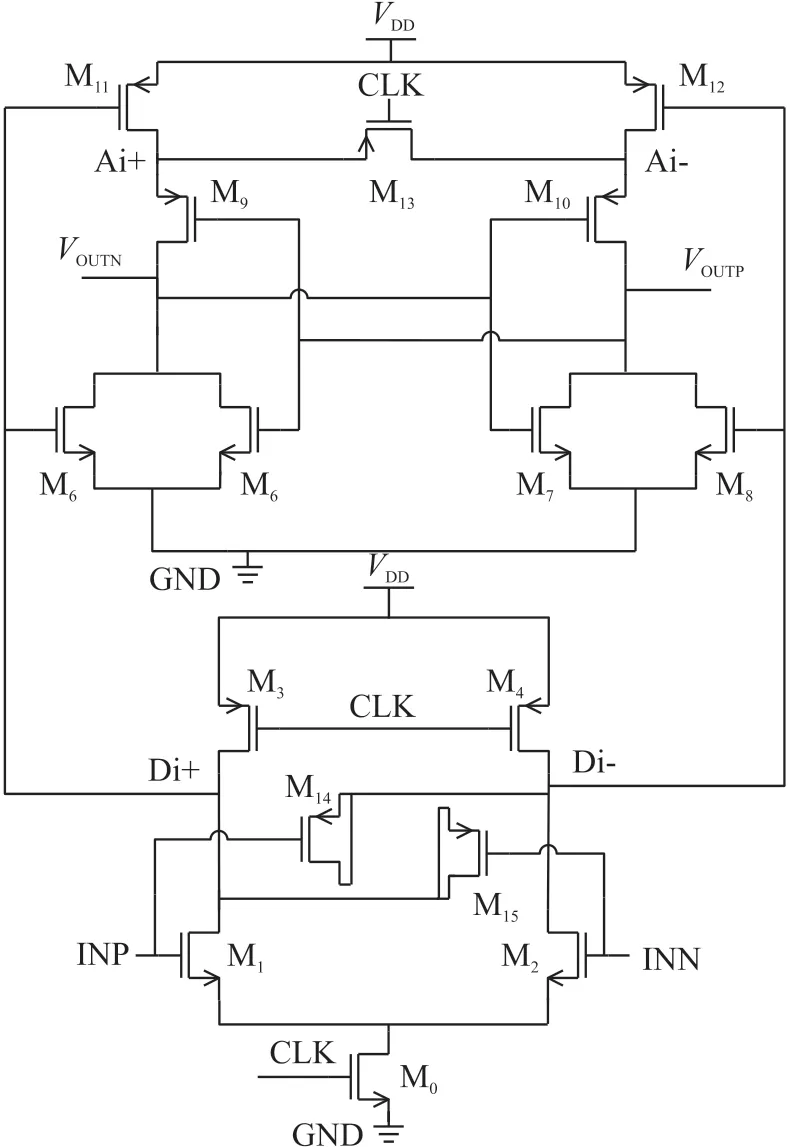

在传统双尾动态比较器和差分双尾动态比较器的基础上,提出了一种高频低失调低回踢噪声的动态比较器,整体电路如图5 所示。

图5 本文提出的低失调低回踢噪声动态比较器

比较器中M0~M4及MOS 型电容M14、M15构成预放大器,M5~M12及钟控MOS 开关M13构成锁存器。电路可工作在1 GHz 时钟下,实现高频低失调低回踢的动态比较器,下面分别对预放大器和锁存器进行分析。

2.1 电容补偿预放大器设计

为了降低电路的回踢噪声,提高比较器精度,应削减输入对管M1、M2的漏端电压变化幅度,减少寄生电容放电。图6 是本文采用的电容补偿预放大器结构,在输入端增加M14、M15源、漏短接构成的MOS电容,用来降低输入阻抗、提供差分对电流,使得M1、M2的漏极电压保持在复位时建立的电平上下。

图6 电容补偿预放大器

输入差分对管M1、M2的宽长比等参数完全一致,则M1和M2的栅极和漏极之间的寄生电容为

MOS 管M14、M15的源极和漏极各自短接,工作在强反型状态,作为等效电容。由于输入差分对的漏端电压变化此消彼长,而M14、M15交叉结构使得MOS 等效电容与寄生电容相等时充电电流效果抵消,从而大幅削减回踢噪声,抑制电路非理想特性,提升鲁棒性。

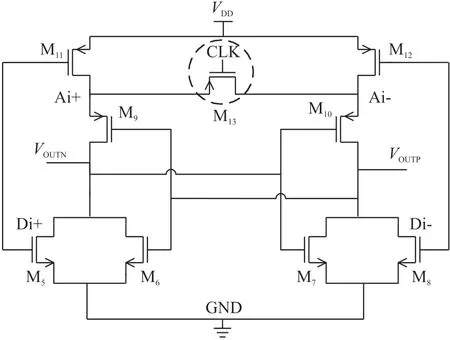

2.2 低延迟低失调锁存器

锁存器用于对预放大器的输出信号进行处理,主要在再生阶段发挥作用,锁存器部分电路如图7所示。

图7 低延迟低失调锁存器

图7 中,Di+、Di-是预放大器的输出,M11和M12不仅是预充电的开关管,还是第二级锁存器的输入管,相较于传统双尾动态比较器,仅需一个时钟信号,简化了时序设计;相较于差分双尾动态比较器,添加了钟控晶体管M13代替图3 中的M13、M14晶体管,连接M9、M10的源端,以避免Ai 节点电压失配产生失调电压。

首先,在复位阶段,CLK 为低电平,预放大器将输出Di 充电为高电平,控制晶体管M5、M8导通,使得比较器输出端VOUTN、VOUTP被下拉至零电位;M11、M12关断,钟控晶体管开关M13闭合,构成交叉耦合反相器的M6、M7和M9、M10晶体管均截止。其次,在再生阶段,CLK 为高电平,预放大器的尾电流源管导通,其输出节点Di 的共模电压以IM0/CDi的速率下降,其中CDi为第一级的负载电容,输入差模电压ΔVDi将在短时间快速建立。Di 节点电位由VDD降至VDD-|VTHP|时,M11、M12导通并处于饱和区,此时M11、M12流过的电流为:

M11、M12的电流对Ai 节点充电,直至VAi达到|VTHP|电位,M9、M10导通。则VAi从零电位到|VTHP|电位所用的时间为:

式中:CAi+,Ai-是节点Ai 的寄生电容。

相较于差分双尾动态比较器直接将Ai 节点拉至零电位,本文的低延迟低失调锁存器通过添加M13管,直接将Ai 节点等电位,拉低并箝位至|VTHP|,实现了电荷再利用。故而在比较器再生阶段无需再将电压从零电位拉升至|VTHP|,节省了从0拉至|VTHP|的时间TAi,实现了减小延迟的效果。

2.3 高频低失调低Kickback 噪声比较器性能分析

本文提出的高频低失调低Kickback 噪声动态比较器电路具有如下优点:

①在比较器的预放大级,采用电容补偿预放大器设计,采用MOS 管源漏短接实现电容,面积小,功耗低,降低了输入管的漏端电压变化幅度,大幅削弱了回踢噪声。

②在比较器的锁存器部分,采用差分双尾电流源代替传统双尾比较器的尾电流源,时钟信号从2个减为1 个,简化了时序设计,时钟要求更宽松。

③采用低延迟、低失调锁存器设计,通过加入PMOS 开关管,控制M9、M10的源端,避免了节点电压失配。相对于差分双尾动态比较器,跨接了M13开关管实现Ai+和Ai-等电位,减少了电路面积、失调和功耗。

综上所述,本文提出的比较器结构有效削减了回踢噪声、简化了时序设计、降低了失调电压,在电压、延迟、失调、回踢噪声等关键指标方面具有明显的优势,有一定的价值。

3 电路仿真及讨论

仿真环境:基于TSMC 40nm CMOS 工艺,温度为27 ℃,时钟频率Fclk=1 GHz,VDD=0.9 V,共模输入电压为0.45 V,输入端VINP是频率100 MHz、幅度50 mV的正弦波信号,另一输入端VINN是0.45 V 的恒定电压。二者输入比较器进行比较,仿真结果如图8 所示,可以看出本论文的比较器结构可以对差分输入信号的电压大小进行比较,并完成判定,并输出高低电平。

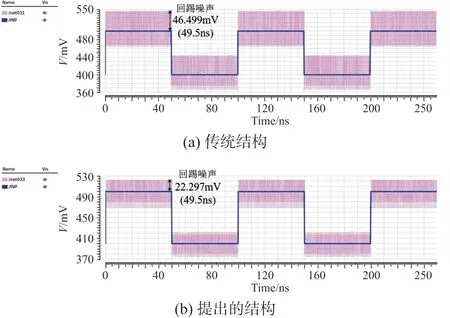

关于Kickback 噪声的仿真波形如图9 所示。

图9 基于瞬态仿真的回踢噪声

由仿真结果可知,传统比较器的峰值Kickback噪声为46.499 mV(49.5 ns 处),本文结构的峰值Kickback 噪声为22.297 mV(49.5 ns 处),仿真结果表明,改进后的比较器Kickback 噪声减少了23.39 mV,约52.05%,极大地削减了回踢噪声。

关于延迟的仿真波形如图10 所示。

图10 基于瞬态仿真的延迟

由仿真结果可知,输入端VINP是幅度50 mV 的直流信号,低延迟低失调锁存器结构比较器的延迟时间为71.26 ps,本文结构的延迟时间为60.91 ps,仿真结果表明,改进后的比较器延迟时间减少了10.35 ps,约14.52%。

关于失调的仿真波形如图11 所示。

图11 基于瞬态仿真的失调

由仿真结果可知,传统比较器的失调电压为17 μV,本文结构的失调电压为11 μV,仿真结果表明,改进后的比较器失调电压减少了6 μV,约35.29%。

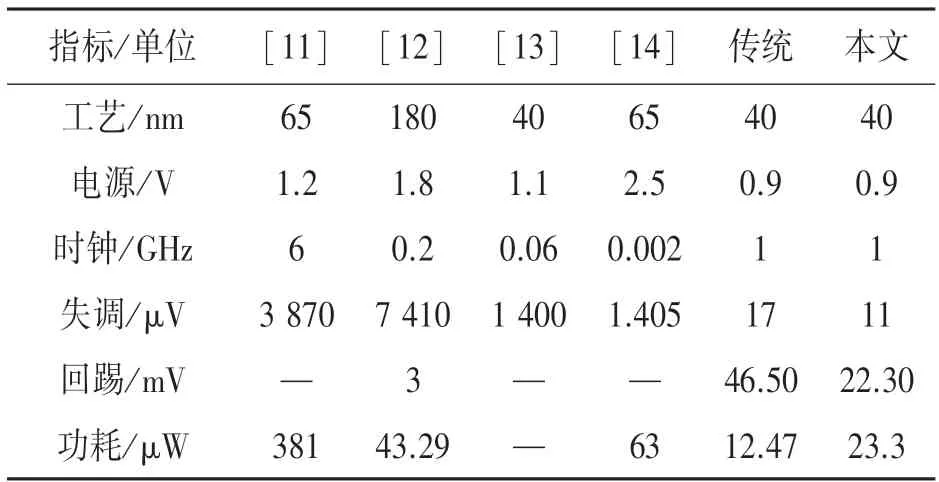

本文仿真结果与近期其他比较器案例的性能对比如表1 所示,对比表明本文提出的高频低失调低Kickback 噪声动态比较器的失调和回踢噪声性能具有明显优势。相较于文献[11],本文失调性能上降低了2 个数量级,功耗也大大降低;相较于文献[12],其采用0.2 GHz 采样频率,远远小于本文采样频率,故其在回踢噪声性能方面有优势,但文献[12]失调远远大于本文结构;文献[13]与本文都采用40 nm 工艺,但其采用较低的时钟频率,且失调较大。相较于文献[14],虽其失调较小,但其在时钟频率极低的情况下,功耗仍然较大。本文与传统结构在工艺、器件尺寸等相同的情况下,失调电压减少约35.29%,Kickback 噪声减少了约52.05%。在各项关键指标方面展现出明显的优越性,适用于高频、低压电路。

表1 本文与其他比较器案例的指标对比

4 结论

本文介绍了动态比较器的基本原理,并重点分析了回踢噪声和失调、延迟等对电路性能的影响。通过添加交叉耦合电容以降低回踢噪声,跨接钟控开关以降低失调和延迟,提出了一种新型的低回踢噪声低失调高频CMOS 比较器。

电路采用TSMC 40 nm/0.9 V 标准CMOS 工艺进行设计与仿真。Cadence Spectre 仿真结果表明,在良好的延迟和功耗表现下,所提出的比较器失调电压为11 μV(降低了约35.29%),回踢噪声为22.297 mV(削减了约52.05%)。比较器性能优越,适用于对回踢噪声和失调电压较为敏感的电路,如高频高速Flash ADC、并行ADC 等信号转换器。