一种低成本的四节点翻转自恢复锁存器设计

2022-09-28徐辉宁亚飞朱瑞刘璇周静

徐辉,宁亚飞,朱瑞,刘璇,周静

(安徽理工大学 计算机科学与工程学院,安徽 淮南 232001)

随着CMOS技术的快速发展,现代集成电路越来越容易受到由软错误引起的可靠性问题的影响。软错误是瞬态错误,主要是由中子、质子、重离子、α粒子、电子等撞击引起的[1-2]。软错误包括单节点翻转(Single Node Upset,SNU)、双节点翻转(Double Node Upsets,DNUs)、三节点翻转(Triple Node Upsets,TNUs)和四节点翻转(Quadruple Node Upsets,QNUs)等。由于近年来先进工艺的特征尺寸显著减小,以及电荷共享机制,单个粒子撞击的影响也会导致包括DNUs和TNUs在内的多节点翻转(Multiple Node Upsets,MNUs)[3]。很明显,仅针对SNU的加固锁存器[4-6]对于要求高可靠性的安全关键航空航天应用已不再足够。

为了解决加固锁存器可靠性不高的问题,本文基于32nm CMOS工艺提出了一种低成本的QNUs自恢复锁存器(Low-Cost Quadruple-Node-Upset Self-Recoverable Latch,LCQNUSRL)。该锁存器由24个C单元构成,形成6×4的阵列结构,构建了四级过滤的容错机制。当锁存器内部任意四个节点发生翻转,经过C单元的阻塞后,该锁存器可自行恢复到正确值。由于高速传输路径和时钟门控技术的使用,本文提出的LCQNUSRL锁存器有着较小的延迟和功耗。HSPICE仿真结果表明,与三个锁存器(LCTNURL[7]、TNURL[8]、LC-TSL[9])平均值相比功耗降低了32.94%,延迟降低了30.2%,PDP降低了53.35%,晶体管数量增加了25%,使用较多的晶体管实现了QNUs自恢复,有着更高的可靠性。此外,所提出的锁存器对电压和温度的变化不敏感。

1 本文提出的锁存器设计

1.1 电路结构和工作原理

为了解决现有锁存器的缺点,提高锁存器的可靠性,本文提出了一种低成本的QNUs自恢复锁存器LCQNUSRL,锁存器结构如图1所示。该锁存器由24个C单元(CE1~CE24)和6个传输门(TG1~TG6)组成,其中CE19~CE24是钟控C单元,可以减少锁存器的功耗。D和Q分别是输入和输出,N2~N24是内部节点,CLK和NCLK分别为系统时钟信号和负系统时钟信号。该锁存器24个C单元平均分成4列,构建了四级过滤的容错机制,每列由6个C单元构成,每个C单元第一个输入连接到下一个紧挨着的C单元的第二个输入,最后一列C单元的输出作为第一列C单元的输入,形成一个反馈回路。

当CLK=1,NCLK=0时,锁存器处于透明期,6个传输门打开,6个钟控C单元关断,输入数据传入到节点Q、N2、N3、N4、N5和N6。假设输入D=1,则Q=N2=N3=N4=N5=N6=1,经过第一列C单元后,N7=N8=N9=N10=N11=N12=0,经过第二列C单元后,N13=N14=N15=N16=N17=N18=1,同理可得,N19=N20=N21=N22=N23=N24=0。

当CLK=0,NCLK=1时,锁存器处于锁存期,6个传输门关断,6个钟控C单元打开,形成一个反馈回路,锁存器保持逻辑值。

图1 本文提出的LCQNUSRL锁存器

1.2 容错原理和仿真分析

本文提出的LCQNUSRL锁存器是一个QNUs自恢复锁存器,下面来分析其容错原理,所有的容错原理都是在锁存器锁存期内分析的。

SNU自恢复:由于锁存器由C单元组成,C单元可以容忍其中一个输入的变化,而输出不会受到影响,因此当其中一列C单元的某个输入节点发生翻转,将不会影响到下一列C单元的输入节点。而锁存器阵列的反馈将恢复发生翻转的节点,因此Q将保持正确的逻辑值,锁存器可以实现SNU的自恢复。

DNUs自恢复:锁存器发生DNUs时,有以下两种情况。

情况1:发生翻转的两个节点是同一列C单元的输入节点。例如,节点Q和N2发生翻转,此时会引起节点N8翻转,错误不会再继续传播下去。因为节点N19~N24是正确的,通过CE19和CE24将节点N2和Q恢复到正确的逻辑值,N2和Q又通过CE2将N8恢复过来。

情况2:发生翻转的两个节点不是同一列C单元的输入节点。例如,节点Q和N7发生翻转,此时不会引起其它节点翻转,经锁存器阵列的反馈将这两个翻转的节点恢复过来。综上所述,锁存器可以实现DNUs的自恢复。

TNUs自恢复:锁存器发生TNUs时,有以下三种情况。

情况1:发生翻转的三个节点是同一列C单元的输入节点。例如,节点Q、N2和N3发生翻转,会引起第二列N8和N9以及第三列N15翻转,错误至此不会再传播下去。因为节点N19~N24是正确的,通过CE19、CE20和CE24将节点N2、N3和Q恢复到正确的逻辑值,然后依次把N8、N9和N15恢复过来。

情况2:发生翻转的三个节点是两列C单元的输入节点。例如,节点Q、N2和N7发生翻转,会引起N8和N14翻转,至此不会再引起其它节点翻转。通过最后一列钟控C单元首先把Q和N2恢复过来,然后依次把N7、N8和N14恢复过来。

情况3:发生翻转的三个节点是三列C单元的输入节点。例如,节点Q、N7和N13发生翻转,不会引起其它节点翻转,经锁存器阵列的反馈将这三个翻转的节点恢复过来。综上所述,锁存器可以实现TNUs的自恢复。

QNUs自恢复:锁存器发生QNUs时,有以下四种情况。

情况1:发生翻转的四个节点是同一列C单元的输入节点。例如,节点Q、N2、N3和N4发生翻转,会引起第二列C单元N8、N9和N10,第三列C单元N15和N16以及第四列C单元N22总计6个节点翻转。因为N19、N20、N21、N23和N24是正确的,通过CE19、CE20、CE21和CE24分别将N2、N3、N4和Q恢复过来,此时第一列C单元的输入节点N2~N6和Q都是正确的,通过第一列C单元将N8、N9和N10恢复过来,同理,通过第二列C单元将N15和N16恢复过来,通过第三列C单元将N22恢复过来,发生翻转的节点都恢复到了正确的逻辑值。

情况2:发生翻转的四个节点是两列C单元的输入节点。例如,节点Q、N2、N3和N7发生翻转,会引起N8、N9、N14、N15和N21翻转。因为N19、N20、N23和N24是正确的,通过CE19、CE20和CE24分别将N2、N3和Q恢复过来,此时第一列C单元的输入节点N2~N6和Q都是正确的,通过第一列C单元将N7、N8和N9恢复过来,同理,N14、N15和N21可依次恢复到正确的逻辑值。

情况3:发生翻转的四个节点是三列C单元的输入节点。例如,节点Q、N7、N13和N14发生翻转,会引起N20翻转。因为N23和N24是正确的,Q通过CE24恢复过来,N7通过CE1恢复过来,N13和N14分别通过CE7和CE8恢复过来,N20通过CE14恢复过来。

情况4:发生翻转的四个节点是四列C单元的输入节点。例如,节点Q、N7、N13和N19发生翻转,此时不会引起其它节点翻转。因为N23和N24是正确的,Q通过CE24恢复过来,而后N7、N13和N19经锁存器阵列的反馈恢复过来。综上所述,本文提出的锁存器可以实现QNUs的自恢复。

为了验证所提出的锁存器对软错误的容忍能力,使用HSPICE仿真工具进行粒子故障注入实验,仿真条件如下:采用PTM(Predictive Technology Model)32nm工艺,温度设置为室温25℃,供电电压设置为0.9V,时钟周期为2ns。锁存器设计中的晶体管尺寸如下:PMOS晶体管尺寸均设为W/L=2,NMOS晶体管尺寸均设为W/L=1。

图2显示了所提出的锁存器的故障注入仿真结果。仿真波形图中闪电符号表示在该位置模拟故障注入。

图2 LCQNUSRL故障注入

图2(a)是模拟SNU和DNUs故障注入的仿真波形图。如图所示,对于SNU分别对Q和N9进行故障注入;对于DNUs分别对(Q、N2)节点对和(Q、N7)节点对进行故障注入。从波形图中可以看出,所有翻转的节点都可以自恢复到初始状态。

图2(b)是模拟TNUs故障注入的仿真波形图。如图所示,分别对{Q N2,N3},{Q,N2,N7}和{Q,N7,N13}3个节点组进行故障注入,这3个节点组分别属于情况1、情况2和情况3。从波形图中可以看出,所有翻转的节点都可以自恢复到初始状态。

图2(c)是模拟QNUs故障注入的仿真波形图。如图所示,分别对{Q,N2,N3,N4},{Q,N2,N3,N7},{Q,N7,N13,N14}和{Q,N7,N13,N19}4个节点组进行故障注入。从波形图可以看出,{Q,N2,N3,N4}节点组故障注入后产生的其它节点翻转数量最多,但所有翻转的节点都可以自恢复到初始状态。对于另外三种情况,所有翻转的节点也都可以自恢复到初始状态。综上所述,本文提出的锁存器实现了QNUs自恢复。

2 评估与对比

本节将提出的锁存器与DNCS锁存器[10]、DONUT锁存器[11]、HRCE锁存器[12]、TNU-Latch锁存器[3]、LCTNURL锁存器[7]、TNURL锁存器[8]和LC-TSL锁存器[9]在相同的仿真条件(32nm CMOS工艺,温度设置为室温25℃,供电电压设置为0.9V,时钟周期为2 ns)下进行对比,包括可靠性、面积、延迟和功耗等方面的比较。

2.1 可靠性比较

各锁存器可靠性比较结果如表1所示。从表1中可以看出,所提出的锁存器具有QNUs自恢复能力,和另外7个锁存器相比有着最高的可靠性。

表1 各锁存器可靠性对比

2.2 开销比较

表2给出了所提出的锁存器和7个加固锁存器的开销对比。其中,功耗表示平均功耗(动态和静态),延迟表示D到Q的传输延迟,即从D到Q上升和下降延迟的平均值。

从表2的第3列数据可以看出,所提出的锁存器的延迟仅次于DNUs自恢复锁存器HRCE[12],且仅增加了2.66%。从表2的第4列数据可以看出,本文所提出的锁存器晶体管数量较多。为了实现更高的可靠性,本文结构使用了较多的晶体管,但仍少于TNUs自恢复锁存器TNURL[8]。

PDP能够综合衡量电路的功耗延迟特性,PDP越小,电路结构的工作性能就越优良[13]。从表2的第5列数据可以看出,与7个加固锁存器相比,本文所提出的锁存器的PDP仅次于DNUs自恢复锁存器HRCE[12]。

表2 开销对比

为了使对比结果更加直观,使用公式(1)和公式(2)来计算开销的相对变化。表3中给出了所提出的锁存器和3个TNUs自恢复锁存器的相对开销比较。从中可以看出,与三个锁存器平均值相比功耗降低了32.94%,延迟降低了30.2%,PDP降低了53.35%,晶体管数量增加了25%,使用较多的晶体管实现了QNUs自恢复,有着更高的可靠性。

表3 开销的相对变化(%)

Δ=(本文提出结构-对比结构)/对比结构×100%

(1)

Δ平均值=(本文提出结构-对比结构平均值)/对比结构平均值×100%

(2)

2.3 电压和温度的波动分析

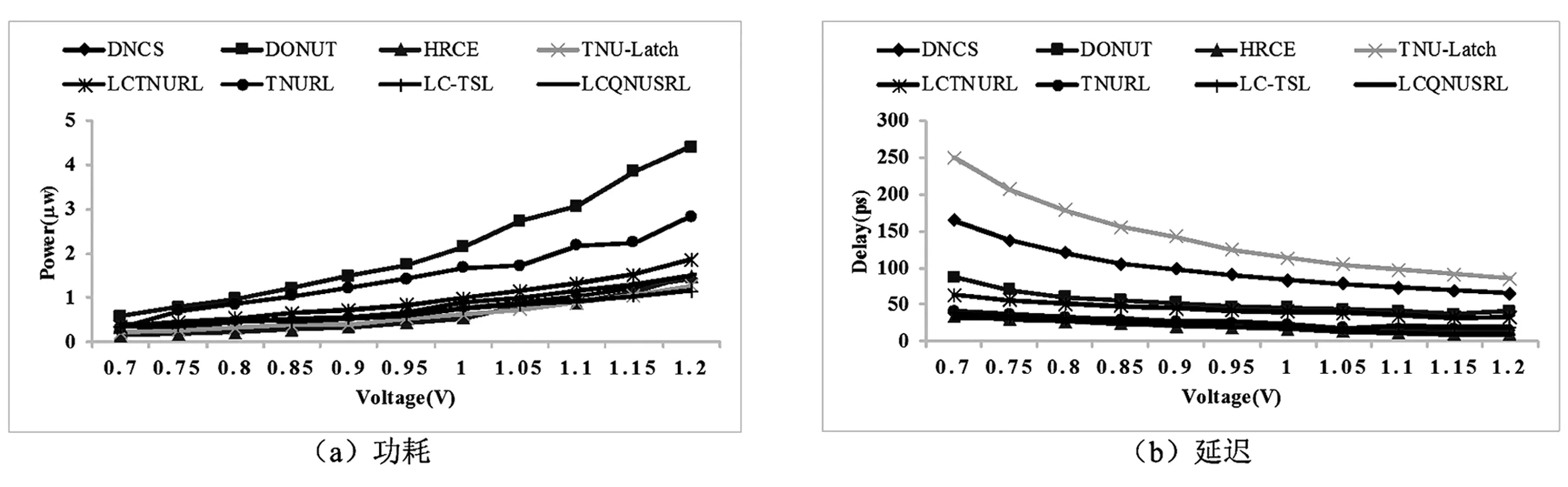

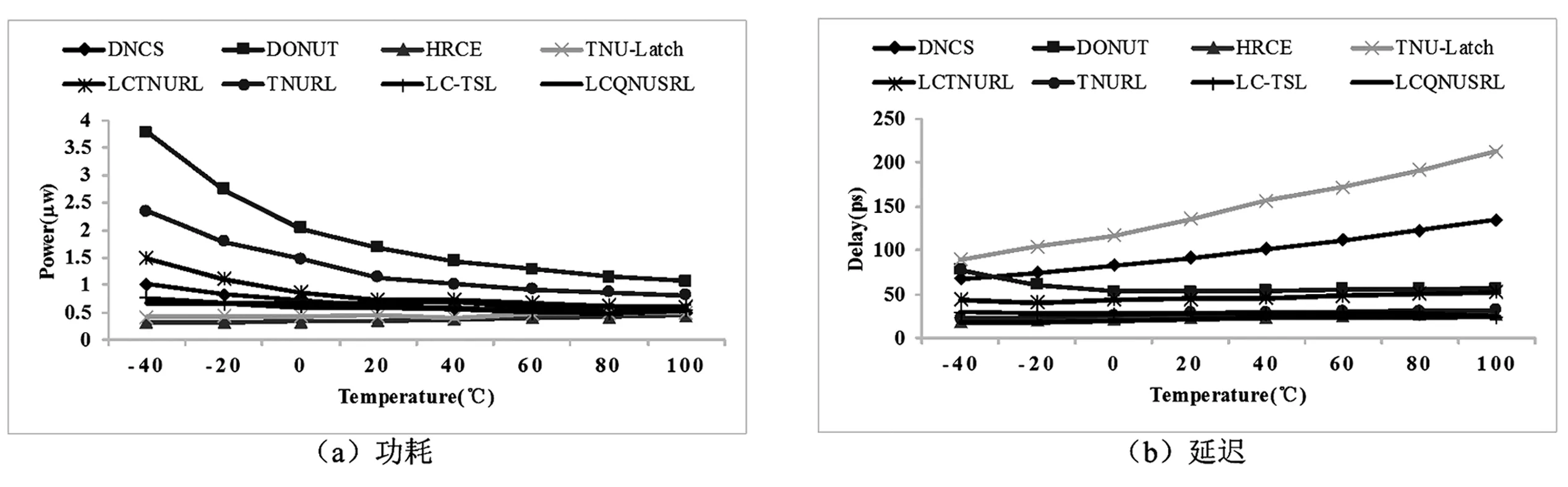

现代锁存器对纳米级技术中的电压和温度变化越来越敏感[14],这里比较了8个锁存器的功耗和延迟对电源电压以及温度变化的敏感性。图3(a)和图3(b)分别为电源电压变化对锁存器功耗和延迟的影响;图4(a)和图4(b)分别为温度变化对锁存器功耗和延迟的影响。电源电压变化范围为0.7~1.2V,温度变化范围为-40~100℃。

图3(a)显示了电源电压变化对锁存器功耗的影响。从图中可以看出,功耗随着电源电压的增大而增大。这8个锁存器中,DONUT[11]和TNURL[8]对电源电压的变化更为敏感,所提出的锁存器对电源电压的变化并不敏感。图3(b)显示了电源电压变化对锁存器延迟的影响。从图中可以看出,锁存器的延迟随着电源电压的增大而减小。这8个锁存器中,TNU-Latch[3]和DNCS[10]对电源电压的变化更为敏感,所提出的锁存器曲线波动较小,对电源电压变化的敏感性较小。

图3 电源电压变化对锁存器功耗和延迟的影响

图4(a)显示了温度变化对锁存器功耗的影响。从图中可以看出,8个锁存器中,DONUT[11]和TNURL[8]对温度的变化最为敏感,所提出的锁存器对温度的变化不敏感。图4(b)显示了温度变化对锁存器延迟的影响。从图中可以看出,所提出的锁存器的延迟对温度变化相对稳定。综上所述,所提出的锁存器对电压和温度的变化不敏感。

图4 温度变化对锁存器功耗和延迟的影响

3 结论

本文基于32nm CMOS工艺提出了一种低成本的QNUs自恢复锁存器(LCQNUSRL)。该锁存器由24个C单元构成,形成6×4的阵列结构,构建了四级过滤的容错机制。当锁存器内部任意四个节点发生翻转,经过C单元的阻塞后,该锁存器可自行恢复到正确值。HSPICE实验表明,所提出的锁存器在功耗、延迟和PDP方面都有着一定的优势,并且对电压和温度的变化不敏感。