低功耗SM4-CCM 算法硬件架构设计∗

2024-01-29夏吉安胡光永

陈 锐,李 冰,夏吉安,胡光永

(1.南京工业职业技术大学计算机与软件学院,江苏 南京 210023;2.东南大学微电子学院,江苏 南京 210096)

近年来,物联网技术被广泛应用于各行各业,如智慧医疗[1]、智慧养殖[2]、智慧电力[3]、智慧城市[4]等。物联网技术之所以被广泛应用,主要是因为其采集数据的隐含价值。通过GPRS[5]、NB-IoT[6]、LoRa[3]等无线通信协议将采集数据传递至云端,借助于大数据、人工智能等技术,可实现数据挖掘、预测分析、智能决策等先进应用。在许多应用领域,物联网终端设备采集的数据与用户隐私、生命财产安全密切相关,使得物联网攻击事件频发,如2010 年的“震网病毒”攻击多国核电站[7]、2016 年Mirai 恶意代码控制物联网终端发起DDoS 攻击导致大半个美国网络瘫痪[8]。为了避免数据在传输过程中遭受篡改、泄露而引起安全事故,应在数据源即物联网终端侧对采集数据进行安全保护。数据的保护可以通过在物联网终端设备上部署密码学算法来实现。认证加密算法作为一类应用广泛的密码学算法,不仅可以保障数据的机密性,还可以保障数据的完整性。2021 年IETF 公布了RFC 8998 标准[9],提出基于国产分组密码算法SM4 的两种认证加密算法,SM4-CCM 就是其中一种。本文面向物联网数据安全,以SM4-CCM 为对象,研究适合于物联网资源受限场景下的数据安全保障方法。

由于物联网终端资源受限,有些甚至采用电池供电,因而对算法实现的成本、功耗要求较高。相比于软件实现计算密集的密码学算法,硬件实现具有更高的性能、更低的功耗、更好的安全性、更少的ROM/RAM 资源占用等优势。硬件实现的这些优势促使我们研究和设计SM4-CCM 的专用硬件电路架构。

与本文相关的文献主要集中针对SM4 算法的某一种工作模式的硬件实现(如CBC 模式[10-11],CTR 模式[12])、针对SM4 算法的指令集扩展[13-14]、针对SM4 算法本身的低开销设计[15-17]等。本文也是针对SM4 算法的一种工作模式,但是与上述文献不同的是:①采用资源复用技术,仅用一个轮函数就实现了CCM 模式所包含的CBC-MAC 模式和CTR模式,不仅实现了加解密功能,还实现了完整性校验功能;②为了降低SM4-CCM 算法的功耗,引入基于Decoder-Switch-Encoder(DSE)[18]架构的Sbox,与其他设计相比,功耗降低明显。

1 SM4 与SM4-CCM 算法简介

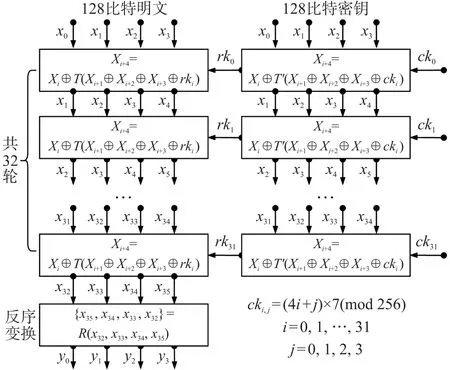

SM4 算法是国家密码局2010 年公布的分组密码算法行业标准,2016 年成为国家标准,2021 年成为国际标准。该算法由加解密算法和密钥扩展算法组成。加密算法和解密算法结构相同,均由32 轮迭代和1 个反序变换组成,二者不同之处在于输入到迭代轮函数的轮密钥顺序相反。如图1 所示,加解密算法迭代所需的轮密钥由密钥扩展算法依据输入的128 比特主密钥经过32 轮迭代生成,共32 个,每个轮密钥32 比特。密钥扩展算法与加密算法结构相似,但是不需要反序变换。关于SM4 算法的详细介绍可以查看文献[19]。

图1 SM4 加解密算法和密钥扩展算法示意图

CCM 算法是美国NIST 提出的分组密钥算法认证加密工作模式,由两种工作模式组成:用于产生128 比特消息认证码的CBC-MAC 模式和用于加解密的CTR 模式。因而,CCM 算法既能对输入数据进行加解密,又能保障数据的完整性。关于CCM 模式的详细介绍可以查看文献[20]。CCM 算法对数据的处理可分为四个阶段:Nonce 数据的处理、AAD 数据的处理、明文数据的处理以及认证码的生成。图2 为按照这四个阶段绘制的CCM 算法简化流程图,其中,AAD 为认证附加数据,用于提升算法的安全性,不需要对其进行加解密。从图2 中可以看,输入的明文需同时送入工作于CBC-MAC 模式的SM4模块和工作于CTR 模式的SM4 模块。这两个SM4模块完全相同,只不过输入的数据不同。

图2 简化之后的CCM 算法示意图

由上述分析可知,SM4-CCM 算法可从两个层面实现资源复用以降低资源开销,即SM4 算法本身的实现层面和CCM 算法的实现层面。

2 硬件架构设计

基于前文分析,借助于资源复用技术,本节提出一种低开销、低功耗的SM4-CCM 硬件架构设计。

2.1 整体架构

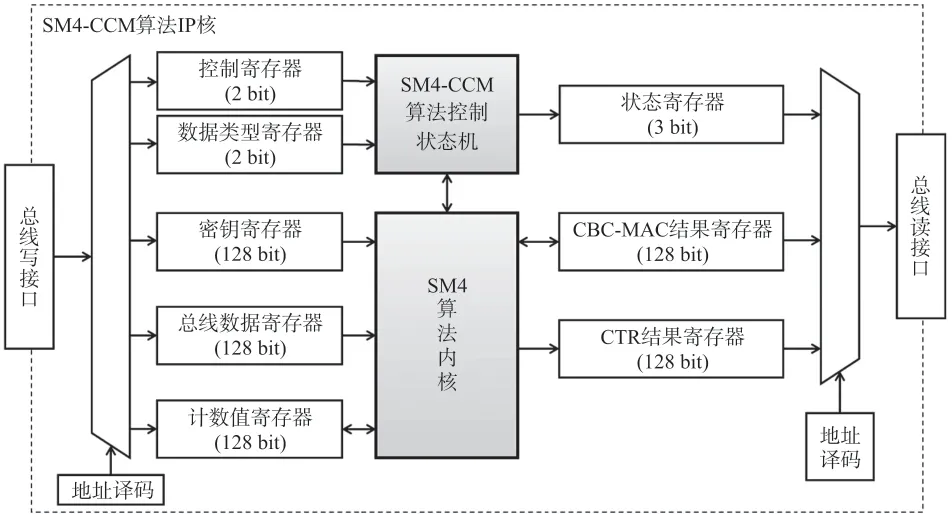

图3 给出了本文提出的SM4-CCM 硬件架构。如图3 所示,采用状态机控制单个SM4 算法内核,以分时复用的方式实现SM4-CCM 正向加密和反向验证算法。整体架构主要包括:SM4 算法内核、SM4-CCM 算法控制状态机、总线读/写接口、3 个控制类寄存器和5 个128 比特的数据寄存器。其中,控制寄存器控制算法开关和工作模式,数据类型寄存器指示总线写入数据的类型,状态寄存器存放SM4-CCM 算法状态或者验证结果。为了降低设计难度,SM4-CCM IP 处理完一个128 比特的数据块即返回空闲状态。因此需要为每次输入的数据块指明数据类型,依据数据块类型是计数器初值、AAD 还是明文数据块触发状态机进入不同的模式,待计算完毕之后将SM4 算法内核的计算结果存入对应的结果寄存器中。当所有数据传递完毕之后,将数据类型寄存器中的“FINISH”标志位置高,那么状态机将控制SM4 算法内核完成最后一次计算,生成MAC值写入CBC-MAC 结果寄存器中,上位机通过总线读接口读取该值。

图3 本文提出的SM4-CCM 硬件架构框图

2.2 控制状态机

本文提出的设计支持SM4-CCM 正向加密和反向验证,图4 给出状态机状态跳转示意图。当SM4-CCM IP 使能时,一旦检测到总线写接口向总线数据寄存器写入数据即启动状态机。

图4 本文提出的SM4-CCM 控制状态机状态跳转示意图

对于SM4-CCM 正向加密采用以下执行流程:①将密钥存入SM4 算法内核中的密钥状态寄存器;②将总线数据寄存器中的数据存入SM4 算法内核中的加解密状态寄存器;③依据数据类型,执行状态跳转,如果是计数器初值或者AAD 数据,则进行CBC-MAC 模式后返回空闲状态(状态跳转路径①→②→③→⑧);如果是明文数据则进入CBCMAC 模式之后再进入CTR 模式最后返回空闲状态(状态跳转路径①→②→③→⑤→⑥);如果数据传递完毕,在收到数据传递完毕信号(数据类型寄存器中“FINISH”标志置高)则直接进入CTR 模式,对计数器初值加密之后与CBC-MAC 结果异或得到所有数据的MAC(状态跳转路径①→②→④→⑥)。

对于SM4-CCM 反向验证采用以下流程:步骤①、②与SM4-CCM 正向加密流程完全一致;③依据数据类型,执行状态跳转,如果是计数器初值或者AAD 数据,则进行CBC-MAC 模式后返回空闲状态(状态跳转路径①→②→③→⑧);如果是密文数据则进入CTR 模式之后再进入CBC-MAC 模式最后返回空闲状态(状态跳转路径①→②→④→⑦→⑧);如果数据传递完毕,在收到数据传递完毕信号(数据类型寄存器中“FINISH”标志置高)则直接进入CTR 模式,对计数器初值加密之后与CBC-MAC 结果异或得到所有数据的MAC(状态跳转路径①→②→④→⑥),最后将其与原始MAC 比较确认数据是否完整。

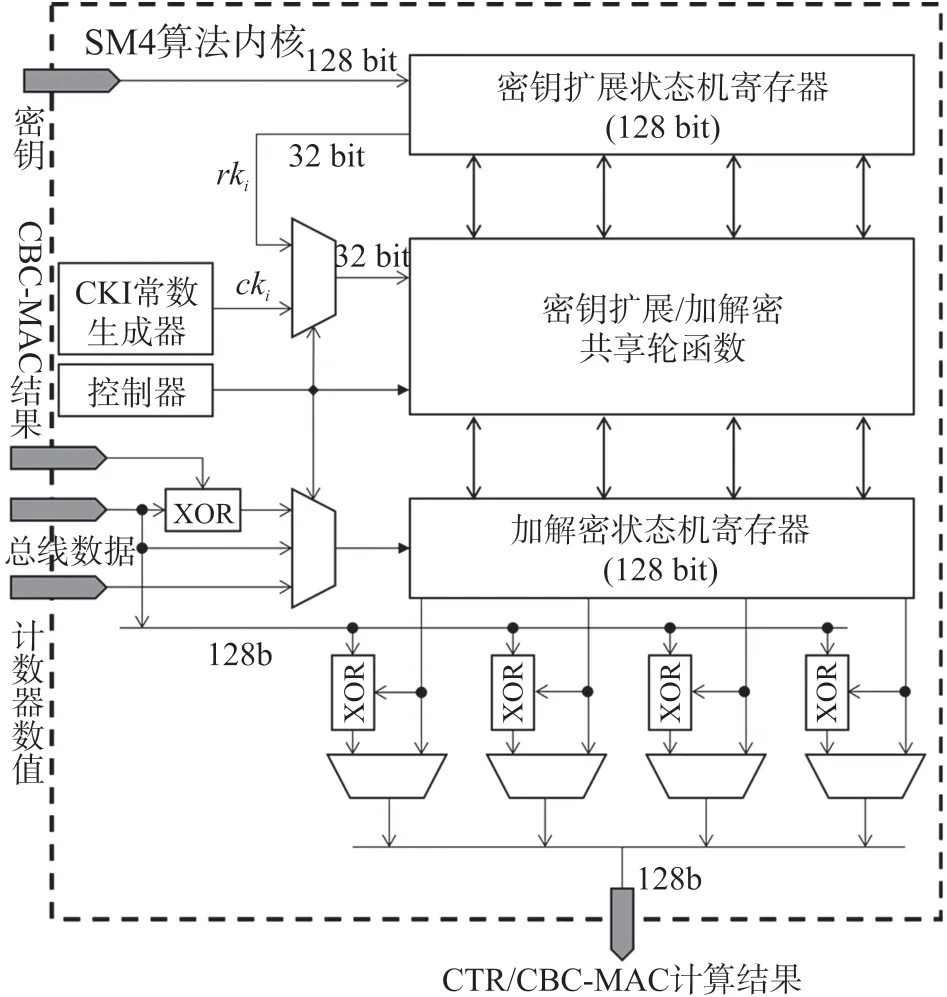

2.3 SM4 硬件架构

图5 给出了SM4 算法内核的架构设计,该模块负责完成SM4 算法的加解密算法和密钥扩展算法。其中,密钥扩展算法采用的是在线生成方法,因而无需存放32 个32 bit 的扩展密钥。SM4 算法内核中包含一个密钥扩展/加解密共享轮函数,其架构如图6 所示。共享轮函数交替工作于密钥扩展模式和加解密模式。密钥扩展模式在前,加解密模式在后。密钥扩展模式下产生的状态数据存放于密钥扩展状态寄存器中,其低32 bit 输出作为加解密模式下的轮密钥。两种模式交替执行32 次之后一个128 bit 的数据块处理完毕。另外,由于SM4-CCM在CBC-MAC 和CTR 模式下输入到SM4 算法内核进行加密的数据是不一样的,需要特殊处理。在CBC-MAC 模式下,总线数据与上一个CBC-MAC 结果异或之后送入加解密状态寄存器,在轮函数32 轮的迭代之后,直接将加解密状态寄存器中的数据输出写入到CBC 结果寄存器。在CTR 模式下,输入到加解密状态寄存器的数据是计数器的值,在轮函数32 轮迭代之后,输出结果与总线数据寄存器异或之后写入到CTR 结果寄存器。

图5 SM4 算法内核硬件架构框图

图6 密钥扩展/加解密共享轮函数硬件架构框图

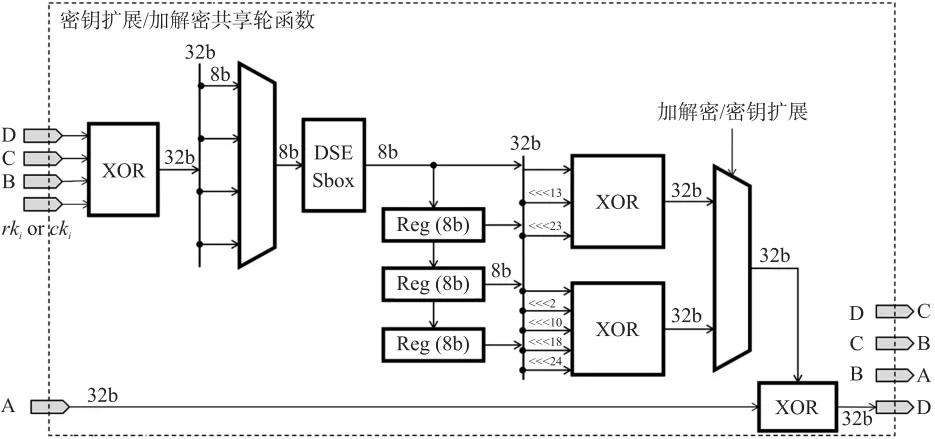

密钥扩展/加解密共享轮函数架构较为简单,如图6 所示,输入是4 个32 bit 数据,经过异或之后生成一个32 bit 数据。该数据将分4 个时钟周期轮流将其各个字节送入到Sbox 中进行字节替换。替换之后的32 bit 数据依当前模式是密钥扩展还是加解密模式,采用不同的移位和异或方式输出并更新状态寄存器。

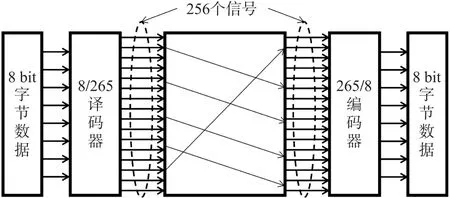

2.3.1 基于DSE 架构的Sbox

为了降低功耗,本文采用了基于Decoder-Switch-Encoder 架构的Sbox[18]。这种Sbox 被认为是功耗最低的一种Sbox[21],但是面积较基于查找表的Sbox 或者基于复合域的Sbox 面积大。然而,由于本文只采用单个Sbox,因而对整个SM4-CCM IP的面积影响较小。其架构如图7 所示,输入为1 个字节8 个信号,经过译码器之后转换成为256 个信号组成的独热信号。连线模块将256 位的独热信号按照SM4 标准中定义的替换表固定连接输入和输出。经过连线模块输出依然是256 位的独热信号,再经过编码器识别出256 位的独热信号1 的位置,将其转换成8 比特的位置索引值。独热信号的引入使得Sbox 内部信号翻转率降低,而功耗与信号翻转率成正比,因而可以降低功耗。

图7 基于Decoder-Switch-Encoder 架构的Sbox

3 实验结果与分析

为了评估本文提出的SM4-CCM 算法硬件架构的性能、面积和功耗,本文采用Verilog HDL 对其进行了描述,采用Synopsys EDA 工具链对其进行功能验证和仿真以获得吞吐率报告、综合以获得面积报告、门级功耗分析以获得功耗报告。

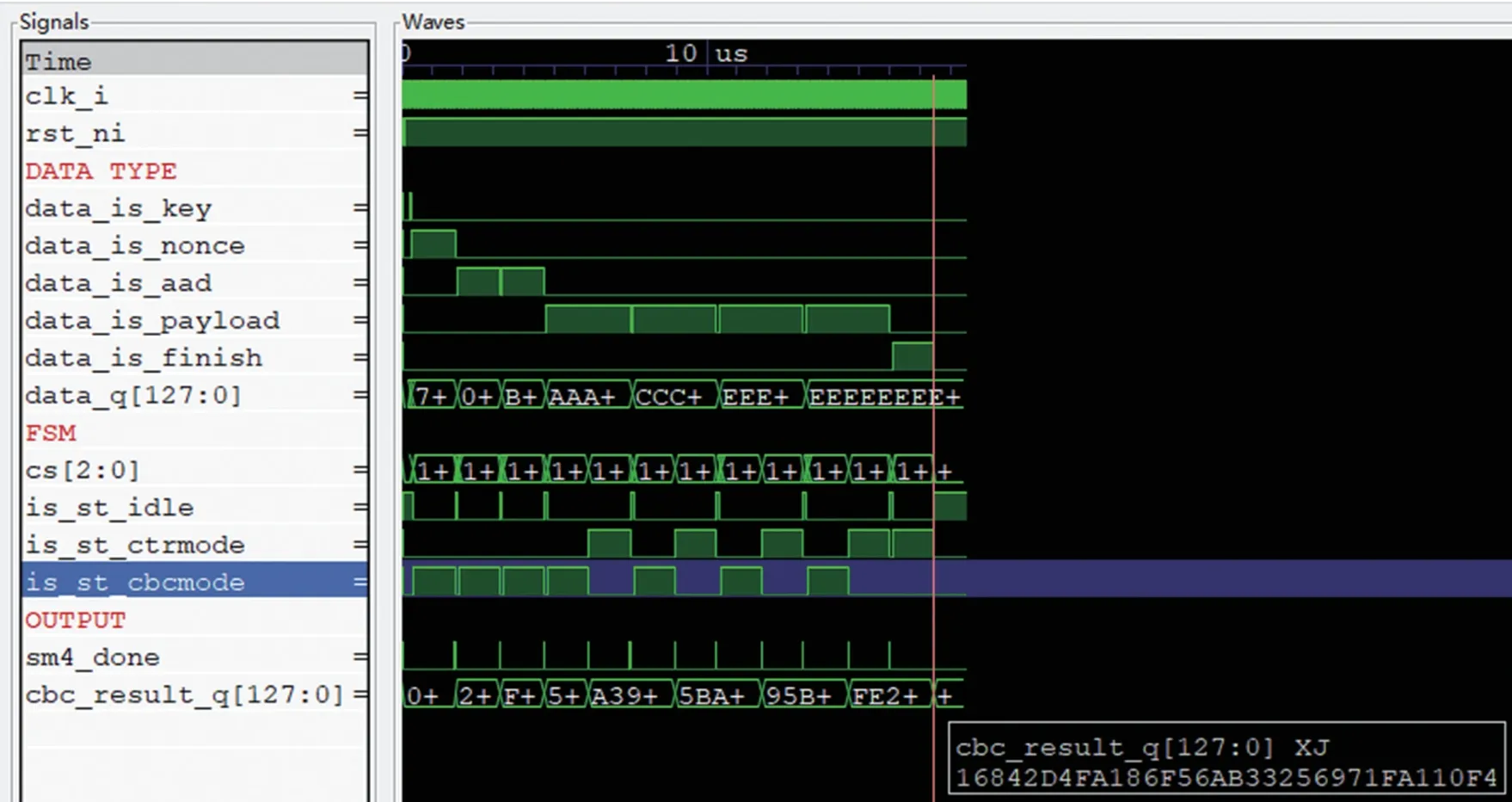

图8 给出了SM4 模块的仿真结果,当输入数据块和密钥均为0123456789ABCDEFFEDCBA98765 43210 时,加密结果应为681EDF34D206965E86 B3E94F536E4246,仿真截图证明SM4 模块功能的正确性。

图8 SM4 模块的仿真结果

图9 给出了SM4-CCM 仿真结果,实验数据来源于文献[9],Nonce 数值为00001234567800000000 ABCD,密钥为 0123456789ABCDEFFEDCBA9876 543210,明文为AAAAAAAAAAAAAAAABBBBBB BBBBBBBBBBCCCCCCCCCCCCCCCCDDDDDDDDD DDDDDDDEEEEEEEEEEEEEEEEFFFFFFFFFFFFF FFFEEEEEEEEEEEEEEEEAAAAAAAAAAAAAAAA,AAD 数据为FEEDFACEDEADBEEFFEEDFACEDEADBEEFABADDAD2,最终的认证码应该为16842D4FA186F56AB33256971FA110F4,图9 仿真截图证明本文设计的SM4-CCM 硬件电路的功能正确性。

图9 SM4-CCM 的仿真结果

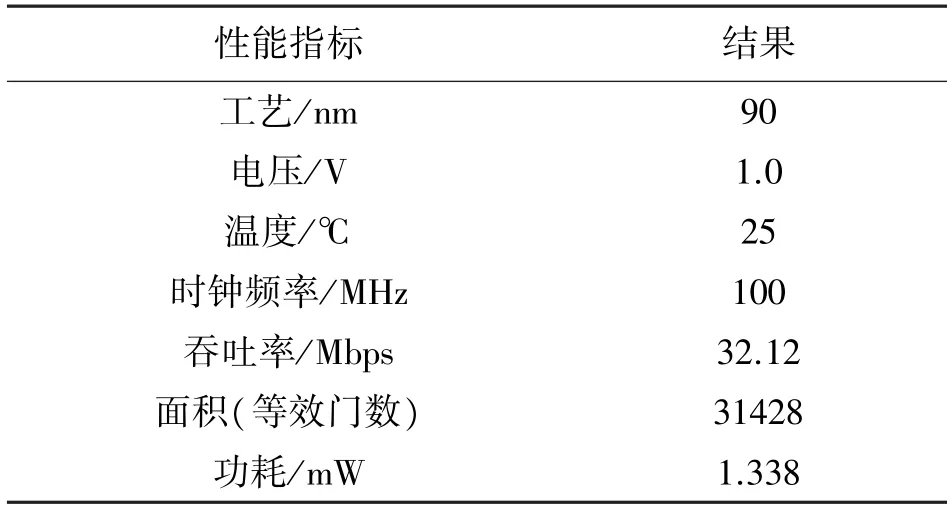

表1 给出了本文设计的性能评估结果。在90 nm工艺100 MHz 时钟频率下,本文设计的硬件电路吞吐率达到32.12 Mbps,面积为31 428 门,而功耗只有1.338 mW。

表1 本文设计的性能评估结果

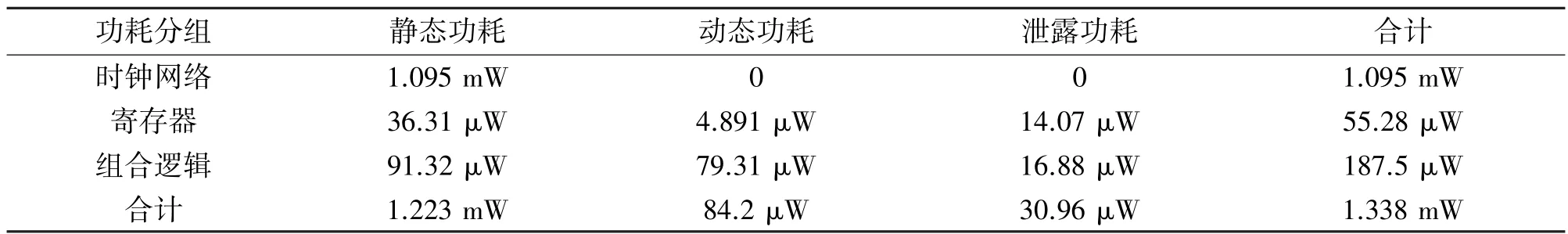

为了获得较为精确的功耗分析结果,本文首先采用门级后仿真的方式获得SAIF 文件,然后将其载入到功耗分析工具PrimeTime-PX 进行分析,由此获得了较为精确的功耗分析报告,具体结果如表2 所示。从表2 可以看出,本文架构的动态功耗、静态功耗和泄露功耗分别为84.2 μW、1.223 mW 和30.96 μW,三者分别占了总功耗的6.29%、91.4%和2.31%。

表2 本文设计的门级功耗分析结果

表3 罗列本文架构与参考文献的比较结果。从表中可以看出,仅有本文设计实现了SM4-CCM 算法,并且本文设计的功能涵盖列表中所有文献的功能。与文献[15,22]相比,本文设计功耗最低,但是由于SM4-CCM 算法复杂度相较于SM4 算法高很多,使得本文设计的面积开销较二者高。虽然本文架构的吞吐率较其他文献低,但是考虑到本文面向的是物联网领域,而该领域的无线通信协议对数据速率要求较低(比如LoRa 的数据速率仅为250 kbps),因而可得出以下结论:本文提出的SM4-CCM 硬件架构是一种具有低开销、低功耗、吞吐率适中、完全满足物联网应用需求的设计。

表3 本文设计与参考文献的性能比较

最后,为了证明本文提出的硬件架构功能的正确性,我们将其实现并下载到DE10-Standard FPGA开发板,然后通过Signal Tap 逻辑分析仪抓取FPGA芯片运行结果,原型验证环境如图10(a)所示。我们将RFC 8998 提供的SM4-CCM 测试向量以MIF文件的方式载入到FPGA 中,然后通过逻辑分析仪抓取波形。图10(b)所示的波形抓取结果与RFC 8998 中的结果完全一直,证明本文提出的硬件架构的功能正确性。

图10 本文设计的FPGA 原型验证环境和抓取波形

4 总结

面向物联网终端数据安全保护需求,本文以SM4-CCM 认证加密算法为对象,借助于资源复用技术,研究和设计了一款SM4-CCM 算法专用硬件架构。在TSMC 90 nm 工艺下的实验结果显示,本文提出的硬件架构设计的面积开销、功耗、吞吐率分别为31428 门、1.338 mW、32.12 Mbps@ 100MHz。实验结果表明,本文提出的架构设计具有低开销、低功耗、吞吐率适中的特点,能够满足物联网终端对数据保护的应用需求。后续研究将面向物联网数据安全,研究和设计更多的满足物联网应用需求的密码算法IP。