Flash 型FPGA 内嵌BRAM 测试技术研究

2023-12-31雷星辰季伟伟陈龙韩森

雷星辰,季伟伟,陈龙,韩森

(1.电子科技大学(深圳)高等研究院,广东深圳 518110;2.中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

Flash 型FPGA 以其非易失性[1]、低功耗[2]、高安全性和上电即可运行[3]的特性在航空航天及军事领域得到广泛应用[4],因此对Flash 型FPGA 内部资源测试方法的研究尤为重要。FPGA 内嵌的块随机存储器(BRAM)能够快速且稳定地存取数据,因此对BRAM的测试是至关重要的[5]。在存储器测试中,存储器内建自测试(MBIST)已经成为主流测试方法,此方法不仅能减少测试步骤和提高故障覆盖率,还能减少测试成本[6-7]。March C+算法是存储器测试中最为有效的测试算法之一,因其具有较高的故障覆盖率和较短的测试时间等优点,被广泛应用于存储器测试中,但其仍然存在故障覆盖不全的问题,如不能覆盖写干扰耦合、干扰耦合、写破坏耦合、字内反向耦合、字内等幂耦合、字内状态耦合等故障[8]。本文基于March C+算法对其进行改进,提高其故障覆盖率,并设计内建自测试(BIST)电路对优化后的算法进行验证,结果表明,该算法可以达到提高故障覆盖率的目的。

2 故障模型

故障模型不但可以将存储器内部的物理缺陷反映出来,同时也有助于完善测试算法。根据敏化Flash型FPGA 内嵌BRAM 故障需要进行的操作行为,将故障分为单单元故障、双单元耦合故障以及多单元故障[9]。因多单元故障很少出现,因此本文暂不对其进行研究。

2.1 单单元故障

单单元故障是指在一个单独的存储单元上发生的故障,不受其他存储单元的影响。单单元故障主要包括固定故障(SAF)、转换故障(TF)、写干扰故障(WDF)、读破坏故障(RDF)、伪读破坏故障(DRDF)、错误读取故障(IRF)、地址译码故障(ADF)和字内故障[10]。

SAF 是指对存储单元进行任何读写操作都不影响它的故障状态值。存储单元的固定值为0 或1(记为SAF0 或SAF1)且不发生改变。

TF 是指存储单元的状态值无法从0 跳变到1,或无法从1 跳变到0。

WDF 是指对某个单元进行写操作,当写入值与存储单元自身的存储值相同时,这个写操作会引起自身的存储值发生改变。

RDF 是指对存储单元进行读操作时,读操作引起存储单元内原有值发生变化,并将发生变化后的错误值读出。

DRDF 是指对存储单元进行读操作时,读操作会引起存储单元内原有值发生变化,但读出的数据却是未发生变化之前的正确值。

IRF 是指对存储单元进行读操作时,存储单元内原有值不发生变化,但读出的数据却是错误值。

ADF 是指给出的逻辑地址不能与对应的存储单元匹配,导致存储单元储存的数据错误。

字内故障是指存储单元中一个字节内的单个比特发生改变,导致另一个比特发生变化。单个单元的字内耦合故障分为以下三类:字内反向耦合故障(Intra-word CFin)、字内幂等耦合故障(Intra-word CFid)、字内状态耦合故障(Intra-word CFst)。

2.2 双单元耦合故障

双单元耦合故障是指对一个存储单元进行操作时,导致与其相邻或耦合的单元存储的值发生改变。双单元耦合故障可分为以下几类:状态耦合故障(CFst)、干扰耦合故障(CFds)、转换耦合故障(CFtr)、写破坏耦合故障(CFwd)、读破坏耦合故障(CFrd)、伪读破坏耦合故障(CFdrd)和错误读取耦合故障(CFir)。

CFst 是指某个存储单元的某个特定状态引起相邻或耦合单元跳变为某一状态。

CFds 是指对某个存储单元进行读写操作,引起相邻或耦合单元的数据发生改变。CFds 可以进一步细分为读干扰耦合故障(CFdsrx)和写干扰耦合故障(CFdsxwx)等类型。

CFtr 是指当某个存储单元为特定状态时,引起相邻或耦合单元的数据发生转换故障。

CFwd 是指对某个存储单元进行写操作,引起相邻或耦合单元的数据发生写破坏故障。

CFrd 是指当某个存储单元为特定状态时,引起相邻或耦合单元的数据发生读破坏故障。

CFdrd 是指当某个存储单元为特定状态时,引起相邻或耦合单元的数据发生伪读破坏故障。

CFir 指当某个存储单元为特定状态时,引起相邻或耦合单元的数据发生错误读取故障。

3 测试算法

3.1 March 算法

BIST 的准确性是由所采用的测试算法来保证的。在存储器测试算法中,March 系列算法是最常用的[11]。最早的March 算法相对简单,并且测试元素的设计也不够成熟。March C+算法由于具有测试步骤少、故障覆盖率高和易实现的特点,被广泛应用于存储器测试中。March C+算法的基本流程如下:

1)对存储器中的所有存储单元进行初始化,将它们的值设置为特定的初始状态值(通常为0 或1);

2)按照升序或降序的顺序,依次将数据写入每个存储单元;

3)在写入数据之后,以相同的顺序逐个读取每个存储单元的数据,并将读取的数据与预期值进行比较,预期值是根据写入数据的规律和地址顺序确定的;

4)根据不同的写入和读取顺序组合,可以检测出存储器中可能存在的各种故障,例如SAF、TF 和耦合故障等,如果读取的数据与预期值不一致,则表明存储器存在故障;

5)为了提高故障检测的覆盖率,需要多次执行步骤2~4,每次执行时,可以选择不同的写入模式和读取顺序,以覆盖更多的测试情况;

6)在执行完上述写入和读取操作后,进行最后一次写入和读取的操作。最后一次写入操作是为了检测存储单元是否存在保持故障,而最后一次读取操作则是为了验证存储器是否达到期望状态。

March C+算法的具体步骤为{↑W0;↑(R0,W1,R1);↑(R1,W0,R0);↓(R0,W1,R1);↓(R1,W0,R0);↓R0}。

3.2 改进后的测试算法

用March C+算法检测BRAM 时仍有部分故障检测不到,其中包括WDF、CFds、CFwd、字内耦合故障等。WDF、CFds、CFwd 不能被检测出来的原因是在0或1 状态下没有进行写0 或写1 操作,从而不能将存储单元敏化为0w0 或1w1 状态。字内耦合故障不能被检测出来的原因是在存储单元状态为0000 或1111时,没有进行写0101 或写1010 操作,只是对一个字节内全部写0 或全部写1。

改进后的算法增加了连续写0 或写1 的测试数据背景,即增加0w0 或1w1 的测试数据背景来覆盖WDF、CFds 和CFwd。针对字内耦合故障的检测,由于都是在同一个地址进行写操作,且是由高位到低位写入,因此,字内耦合故障与地址的升降无关,可在原有算法基础上增加0101 及1010 的测试数据背景来检测字内耦合故障。对于1 个位宽为4 的存储器,其具体的测试算法步骤如下:{↑Wd0;↑(Rd0,Wd1,Rd1);↑(Rd1,Wd2,Rd2);↑(Rd2,Wd3,Rd3);↑(Rd3,Wd0,Wd0,Rd0);↓(Rd0,Wd3,Wd3,Rd3);↓(Rd3,Wd0,Rd0);↓Rd3}(其中d0 为4'b0000,d1 为4'b0101,d2 为4'b1010,d3 为4'b1111)。采用优化后算法控制电路状态转换的流程如图1 所示。

图1 采用优化后算法控制电路状态转换的流程

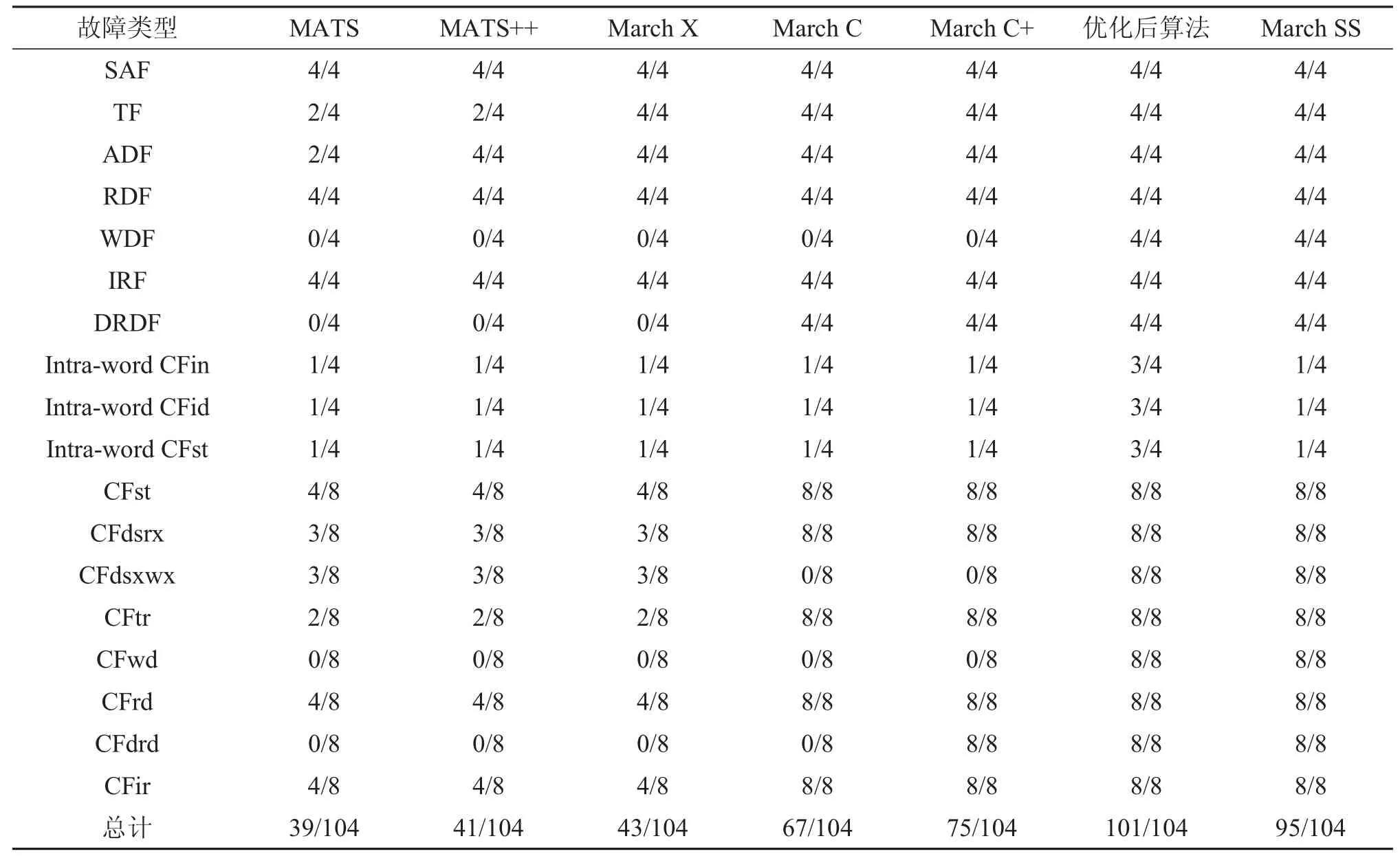

优化后算法改进了故障模型及故障原语,如表1所示。

表1 优化后算法的故障模型和故障原语

将常见的March 系列算法检测出的故障类型[8]与优化后算法检测出的故障类型进行对比,各种算法的故障覆盖率如表2 所示。可以看出,优化后算法对各类故障的覆盖更全面,故障覆盖率更高。相较于March C+算法的故障覆盖率(72.1%),优化后算法的故障覆盖率(97.1%)提高了25 个百分点;与时间复杂度相同的March SS 算法相比,优化后算法的故障覆盖率提高了5.8 个百分点。

表2 各种算法的故障覆盖率

4 BIST 基本原理

BIST 是一种在设计时在集成电路或芯片中嵌入相关功能电路,以提供自我测试功能的测试技术,可在集成电路或芯片内部进行故障检测。该技术通过在芯片内部引入专门的测试电路,对各个功能模块或组件的输入/输出数据进行控制和验证,以判断芯片是否可以正常工作。相较于传统的外部测试方法,BIST具有更高的灵活性和效率,因此,本文选择BIST 来验证算法的有效性。BIST 电路通常包括控制器、地址生成器、向量生成器和比较器等关键组件。控制器负责管理整个测试流程,包括启动和停止测试、控制测试模式和参数等。地址生成器负责生成访问存储单元的地址序列,以确保覆盖全部存储单元的测试。向量生成器则产生具有特定模式或随机性的测试数据,用于驱动和验证芯片功能。比较器则用于将实际输出值与预期输出值进行比较,以检测存储器是否存在故障。本文利用Flash 型FPGA 自身的硬件资源构建BIST电路架构,完成对内嵌BRAM 的测试。采用Verilog 硬件描述语言设计BIST 电路架构,BIST 电路的基本结构如图2 所示。在完成BIST 电路的设计后,将BIST电路配置到FPGA 内嵌BRAM 周围,并对其进行测试。当BIST 电路的DONE 信号处于高电平时,表明测试已经完成;当BIST 电路的FAIL 信号处于高电平时,表明FPGA 内嵌BRAM 存在故障;当BIST 电路的PASS 信号处于高电平时,表明FPGA 内嵌BRAM无故障。

图2 BIST 电路的基本结构

5 算法功能验证与仿真结果

对March C+算法和优化后的算法进行功能验证,采用Microsemi 公司的Libero SoC 设计工具,并使用其搭建Modelsim 仿真平台,待测存储器为1 024×4的BRAM,图3 为采用March C+算法检测无故障的BRAM 的仿真波形图,可以看出,BIST 电路的PASS信号和DONE 信号分别从低电平变为高电平,这表明测试结束且没有测出故障。图4 为采用优化后算法检测无故障的BRAM 的仿真波形图,同样未检测出故障。

图3 采用March C+算法检测无故障的BRAM 的仿真波形图

图4 采用优化后算法检测无故障的BRAM 的仿真波形图

通过对BRAM 注入WDF、CFds 和字内耦合故障,分别采用两种算法对注入WDF 的BRAM 进行测试。图5 为采用March C+算法检测注入WDF 的BRAM 的仿真波形图,可以看出未检测到故障。图6为采用优化后算法检测注入WDF 的BRAM 的仿真波形图,可以看到,在对BRAM 进行连续的写操作后对BRAM 进行读操作,读出数据与写入数据不同,FAIL 信号由低电平变高电平,这表明在地址为3'h379处发生了WDF。

图6 采用优化后算法检测注入WDF 的BRAM 的仿真波形图

图7 为采用优化后算法检测注入CFds 的BRAM的仿真波形图,可以看出,在对地址3'h14e 进行连续的写操作后,3'h14d 处的数据发生变化,产生了CFds,FAIL 信号由低电平变为高电平,这表明故障被测出。因为无法使用March C+算法进行连续的写操作,所以无法检测出CFds。

图7 采用优化后算法检测注入CFds 的BRAM 的仿真波形图

图8 为采用优化后算法检测注入字内耦合故障的BRAM 的仿真波形图。在对原有数据为0000 的存储单元进行写1010 操作时,FAIL 信号从低电平变为高电平,这说明发生了字内耦合故障,导致数据发生变化,此时读出数据为0011,与正确数据不符。采用March C+算法进行测试时,其没有0101 及1010 等测试数据背景,因此无法检测出字内耦合故障。

6 结论

本文在March C+算法的基础上进行改进,得到的优化后算法能够覆盖WDF、CFds、CFwd 和字内耦合故障等原来不能被检测到的故障。对Flash 型FPGA内嵌BRAM 进行BIST 仿真验证,结果表明,优化后的算法可以有效提高故障覆盖率,相较于March C+算法,其故障覆盖率提高了25 个百分点,相较于时间复杂度相同的March SS 算法,其故障覆盖率提高了5.8 个百分点。