自适应阵列天线接收信号模拟器设计

2023-12-11郭成林陈立刚唐羽浓

曾 浩, 郭成林, 陈立刚, 唐羽浓

(1.重庆大学微电子与通信工程学院,重庆 400044;2.西南电子技术研究所,成都 610036)

0 引 言

自适应阵列天线成为抗干扰的重要技术手段,在通信、雷达、测控中应用越来越广[1-3]。自适应阵列天线的研究既包含了无源阵面设计[4],射频前端设计[5],也包括了数字信号处理。随着自适应阵列天线性能提升,信号处理的复杂度不断增加,功能包含了阵列校正[6],空时二维滤波[7],稳健波束合成[8]等等。为了能够对数字信号处理模块进行独立性能测试,需要设计一个阵列天线接收信号的模拟器。现有一些设计采用模拟电路实现,通道数量少,生成信号灵活性较差[9-10]。

本文设计的模拟器利用现场可编程门阵列(Field Programmable Gate Array,FPGA)的灵活性[11],可实现同时多信号产生,适用阵列包括均匀线性阵或平面阵,不仅可以设置入射信号的频率、俯仰角、方位角、功率参数,亦可更改信号类型为点频、二进制相移键控(Binary Phase Shift Keying,BPSK)信号、高斯白噪声。

1 系统硬件设计

系统硬件设计框图如图1 所示,系统主要分为FPGA系统、电源系统、时钟系统和发射系统4 个部分。其中FPGA 系统为FPGA 最小系统,由FPGA、系统配置时钟晶振、闪存、联合行动测试小组(Joint Test Action Group,JTAG)接口和串口组成。时钟系统由时钟晶振和时钟分路器组成。发射系统由5 路DAC 和滤波电路组成。

图1 系统硬件设计框图

1.1 FPGA系统设计方案

1.1.1 FPGA芯片选型

根据系统的资源评估,采用的FPGA 芯片型号为XC7K325T-2FFG900I,其具有丰富的逻辑资源、计算单元以及大量的高速接口资源。该FPGA 主要资源[12]为:逻辑单元326 080 个、逻辑片50 950 个、RAM4 MB、DSP840 个、I/O500 根。

1.1.2 FPGA配置电路

FPGA芯片提供了下载器连接的专用管脚,在UG474 配置手册中给出了多种配置模式的电路设计,本设计采用主SPI配置模式。对于用于存储配置文件的FLASH芯片,采用MT25QL128 闪存芯片,其供电为3.3 V,可采用FPGA芯片的3.3 V BANK电源系统供电。在调试过程中,本设计使用的是额外的下载器,只需要引出JTAG专用下载引脚到牛角连接器即可。

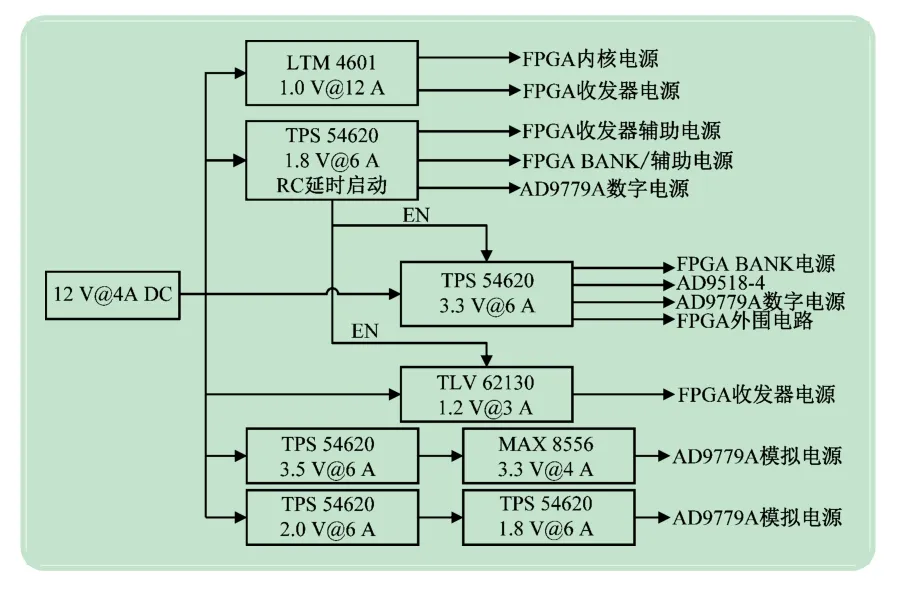

1.2 电源系统设计方案

综合分析系统硬件电路中选用的芯片器件对电源性能的要求以确定电源系统设计方案。FPGA核心系统所需要的电源为1.0、1.2、1.8 和3.3 V。DA 转换芯片需要的数字和模拟电源均为1.8、3.3 V,在电源系统设计中,DA转换芯片的数字电源与FPGA系统电源采用统一供电,模拟电源由TPS54620 芯片将12 V电源稳压到3.5 和2.0 V,再由线性稳压芯片MAX8556 稳压到3.3 和1.8 V 提供给DA 转换芯片。先用TPS54620 稳压到3.5 和2.0 V 的原因是因为线性稳压芯片在大压降的情况下发热严重,转换效率会急剧下降。最终电源设计方案如图2 所示,在保证供电要求的情况,各模块供电给予一部分冗余量。

图2 电源系统设计方案

1.3 时钟系统设计方案

时钟系统采用外部晶振提供时钟信号,而AD9518-4 时钟芯片用于时钟分路,分别提供时钟给FPGA和5 路DAC芯片,并在FPGA和DAC内部通过各自的锁相环倍频到100 MHz 用作运行时钟和采样时钟。设计中,时钟晶振采用SiT9121,频率为50 MHz。AD9518-4 是6 路时钟发生器,内部集成了1.6 GHz压控振荡器和锁相环。本设计中AD9518-4 只充当时钟分路器使用,即将SiT9121 时钟晶振输出通过0.1 uF电容交流耦合至AD9518-4 的CLK/CLK输入端口。

1.4 发射系统设计方案

1.4.1 AD9779A配置端口

在FPGA内部处理的波形数据都是数字信号,所以需要将其转换为模拟信号。本设计选择了AD9779A数模转换芯片,具有性能高、功耗低、转换速率高等优点。AD9779A 为16-bit DAC,在8 倍内插下最高转换速率为1 GSPS,满足本设计需要。AD9779A的配置接口为常见的SPI三线/四线接口,配置较为简单,芯片内部寄存器主要有通用控制、数字控制、PLL控制、模拟控制等。

AD9779A还存在其他的功能端口,如TXENABLE端口,用于发送使能控制;PLL_LOCK端口用于锁相环锁定指示;IRQ端口用于数据时序错误指示。设计中将PLL_LOCK和IRQ管脚连接了LED 便于调试时检查状态;将TXENABLE 管脚连接了FPGA 用于发送控制。

1.4.2 AD9779A数据端口

由于AD9779A的采样率可以达到1 GSPS,数据吞吐量较大,因此数据端口采用的16 bits 并口的设计。每片AD9779A有独立的IQ两个通道,共32 个用来接收转换数据的数据端口。本设计中有5 路DAC芯片,也就是数据端口总共有160 个。根据数据手册,数据管脚支持3.3 V CMOS 电平标准,故均可直接连接到FPGA芯片的3.3 V供电管脚。

1.4.3 参考时钟和同步时钟电路

AD9779A可以通过两种方式获得采样时钟:①采用片内时钟倍频器,外部输入一个较低频率的参考时钟,片内的锁相环将该参考时钟倍频至较高的频率,以用来产生DAC所需的全部内部时钟;②采用外部参考时钟,用户将外部输入的高速参考时钟给DAC 内核。无论使用何种方式,均要求采样时钟信号具有较低的抖动,以尽可能地提高DAC的噪声性能。

AD9779A对采样时钟的要求较高,因此参考时钟输入必须是一个低抖动的差分信号。该差分信号必须在一个以400 mV 为中心的共模电压范围内,使REFCLK +与REFCLK-电压均在200 ~800 mV 范围内,通过电阻分压实现。时钟分路器AD9518-4 提供的时钟信号为LVPECL 时钟,与REFCLK 管脚的电平协议要求一致,时钟电路设计采用数据手册中提供的参考电路设计。

由于本设计是阵列模拟信号源,要求5 路DAC的输出尽可能同步,需要使用DAC芯片提供的同步脉冲管脚进行数据同步,同步管脚电平协议为1.8 V LVDS电平标准,根据此标准,连接同步管脚至FPGA的高速IO BANK以提供1.8 V 的LVDS 同步脉冲信号,耦合方式为交流耦合。

1.4.4 差分电流与电压转换电路

AD9779A的输出以差分电流的形式输出,本设计采用ADT2-1T-1P +巴伦转换器进行转换,将差分电流信号转换为单端电压信号。在输出转换为单端信号后需要滤波,采用LFCN-80 +低通滤波器进行滤波,该滤波器的3 dB带宽为145 MHz,带内衰减最大1 dB,性能较好。

2 系统软件设计

软件系统可分为时钟产生模块、配置程序模块、串口控制模块、DSP 处理模块、数据输出模块。其中,DSP处理模块主要包括:点频信号的产生、BPSK 信号的产生、高斯白噪声的产生、信号合成、权值的产生。

2.1 点频信号的产生

点频信号设计为一个1 ~30 MHz频率可调,步进为1 MHz的正弦信号,假设该信号为

式中,fc为点频信号的频率,fc=1 ~30 MHz。该信号经过正交变换,得到其解析信号

阵列权值用列向量表示为

式中,wm,n为每个阵元对应的权值,其中m,n为单元数,一般取m,n=0,1,-1。此处以五阵元带心圆阵为例,则加权后的信号为5 路解析信号,分别对应5 个阵元接收信号

在FPGA中用DDS IP 核实现点频信号的实部与虚部。该IP核可以产生任意正交的2 个三角函数,即给定所需信号频率f=1 ~30 MHz与采样频率fs=100 MHz时,输出2 个函数值sin(2πft)和cos(2πft),其中t由fs确定。

2.2 BPSK信号的产生

对于BPSK信号,设定其中心频率fc=15 MHz,带宽为10 MHz。其信号为

式中,a(t)为基带信号。则对应解析信号[14]为

同样考虑信号的权值用列向量表示为

则BSPK信号加权后的对应每个阵元输出信号为

用Matlab 产生带宽为10 MHz,中心频率为15 MHz的BPSK信号,并将信号的采样值建表,在FPGA中使用ROM IP 核并导入该参数文件。考虑到FPGA资源分配,分别取33 330 个采样点以二进制补码的数据格式建表。

2.3 高斯白噪声的产生

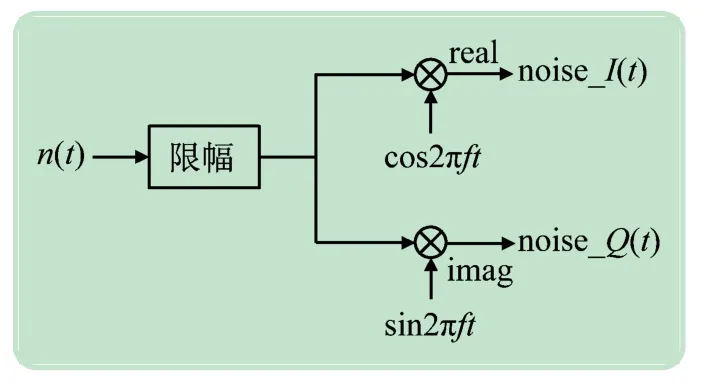

每个阵元的噪声信号是独立的高斯白噪声带通信号,产生带通信号的方法有两种[15]:①先产生一个实的低通高斯白噪声信号,信号带宽为10 MHz,然后通过正交上变频,得到15 MHz 中心频率的带限高斯白噪声解析信号n^mn(t);②先用希尔伯特变换,得到一个复的全频段白噪声信号,然后通过一个10 MHz 带通滤波器,得到中心频率为15 MHz 的带限高斯白噪声解析信号n^mn(t)。

噪声信号为带限高斯白噪声,使用MATLAB 产生,产生过程使用前述的第1 种方法,过程如图3所示。

图3 噪声信号产生过程

5 个天线阵元间的噪声互相独立,所以需产生5个独立的噪声,每个阵元需要实虚2 路噪声,所以一共需建5 ×2 个表。考虑FPGA资源分配,每张表容量为33 330 个数据。

2.4 信号合成

最终得到的每个阵元的输出信号就是上述3 个信号的叠加。在进行叠加之前,可通过相应的功率控制信号,实现输出信号的功率控制。则输出信号

式中:xmn(t)为点频信号;ymn(t)为BPSK信号;n^mn(t)为高斯白噪声。

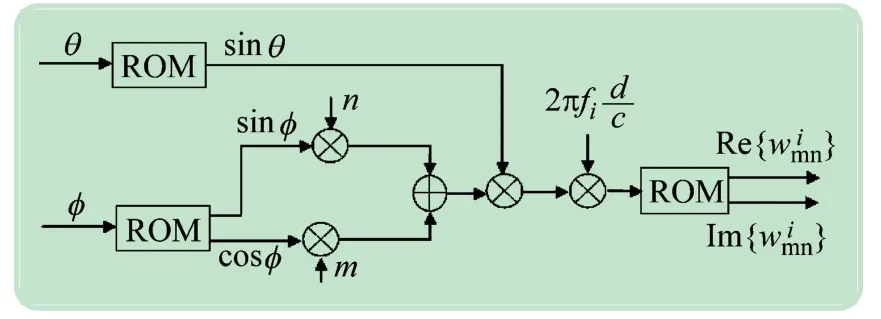

2.5 权值的产生

根据相控阵天线基本理论[16],阵列权值的实部和虚部表达式如下:

式中:d为阵元间距;c为光速;fi、θi、φi分别为第i个信号的频率、俯仰角和方位角。加权时需乘以权值的共轭,故在建表时通过虚部取反来实现。即加权的计算式为

权值计算根据式(12),按照图4 所示流程计算最终输出。该计算过程所需要用到的三角函数sinx和cosx,均可通过查找表的方式计算。

图4 阵列权值产生过程

权值的生成通过建表来实现。在上述情况下,需要建立二级表格,第一级ROM 中存sin θ、sin φ 和cos φ,输出是16 bit补码。由于俯仰角和方位角的范围分别是[0,π/2]和[0,2π],建表时以0.1°为步进,所以sin θ 的容量为901,sin φ 和cos φ 的容量为3 601。第二级ROM容量考虑资源分配取4 096,所以输入为12 bit地址,该地址是通过计算下式得到的12 bit补码值:

输出其三角函数值为16 bit 补码,但虚部取了负号。

根据图4 的计算结构,该部分FPGA 程序框图如图5 所示。

3 实物与测试

根据前面所述设计方案,制作完成的信号模拟器实物如图6 所示。

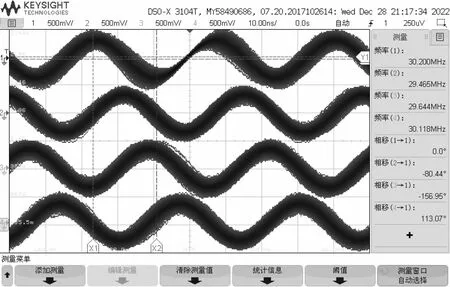

为验证设计方案的正确性,将信号模拟器的4 个信号输出端口,依次连接到四通道示波器的测试输入端口,并测量4 个信号的频率和相位。设置信号源输出频率为30 MHz,入射俯仰角为30°,入射方位角为0°,功率等级为60。4 个输出信号波形分别如图7 所示,观测图中的信号波形、频率测量结果和相位测量结果,其与理论频率30 MHz、理论相位0°、90°、180°、270°基本一致。

图7 信号模拟源点频输出测试屏显结果

除了将点频输出功率等级改为54 之外,信号模拟源的其他设置信息不变,然后设置高斯白噪声输出功率等级为50。此时,4 个输出信号波形如图8 所示。图中可以明显观察到正弦波上叠加了高斯白噪声,测试结果与理论一致。

图8 点频加高斯白噪声输出测试屏显结果

4 结 语

本文设计了一个五阵元自适应阵列天线接收信号模拟器,通过输出不同相移、不同信号类型、不同频率的信号进行测试。测试结果表明:本阵列模拟信号源能够正确地模拟5 个阵列天线接收的信号;信号源输出信号间的相移符合理论计算值。本模拟器在多款机载抗干扰天线测试中得到了有效应用。