P型阱接触布局对于单粒子瞬态脉冲宽度的影响

2023-10-20陈南心丁李利张凤祁徐静妍罗尹虹

陈南心,丁李利,陈 伟,王 坦,张凤祁,徐静妍,罗尹虹

(1. 湘潭大学 材料科学与工程学院,湖南湘潭 411105;2. 强脉冲辐射环境与模拟全国重点实验室,西安 710024)

随着电路工艺集成度越来越高,空间环境中自带的天然辐射环境会给航天器的电子器件带来严重的空间辐射效应[1],其中,单粒子效应(single event effect, SEE)引发的故障已成为影响航天器运行的重要原因[2],因此,研究单粒子效应及抗辐射加固设计对提升集成电路抗辐照性能具有重要意义[3]。SEE是指在天然或人为的辐射环境中,高能粒子穿过半导体器件的结区和耗尽层时,沿电离径迹产生大量电子-空穴对,被器件的敏感区吸收,导致器件损伤的辐射效应。SEE根据是否对器件产生不可逆的损伤分为软错误和硬错误2种。其中,单粒子瞬态敏感效应(single event transient,SET)是软错误的一种,即指瞬态电流在混合逻辑电路中传播,导致输出错误[4]。SET脉冲宽度表征了器件轰击节点上收集的电荷量集合、电荷聚集的速度及电荷从轰击点中移除的速率。反相器作为典型的标准单元之一,通过建立TCAD(technology computer aided design)仿真模型来观察SET发生时器件具体发生的物理过程可准确反映电荷收集的过程,节省大量实验机时与资源,加快研究的进度[5-6]。

刘必慰等[7]通过TCAD 3维模拟,研究n+深阱的三阱工艺反相器中P阱接触对NPN双极放大的影响,结果表明,增大P阱接触面积及减小P阱接触距离可抑制NPN双极放大效应。Amusan等[8]发现NMOS管与PMOS管电荷收集机制的差异会导致SET脉宽不同,且会因N阱电势变化而引发双极放大效应,轰击PMOS管(Phit)会比轰击NMOS管(Nhit)引发更严重的SET。Ahlbin等[9]验证了SET瞬态脉冲与N阱接触面积之间呈指数关系,表明MOS管中的寄生两极连接晶体管(bipolar junction transistor,BJT)传导会同时影响器件截面与SET脉冲宽度。Olson等[10]发现随着阱接触面积的增大,代表双极放大效应程度的放大因子随之减小,这是因较大的阱接触面积会减小轰击位置到阱接触之间电阻通路上的分压。另外一些学者探究了N阱接触面积变化Phit和Nhit[11]、不同形状的阱接触[12]、三阱结构中P阱接触面积的作用[13]、不同形状保护带[14-15]和不同阱深[16]对SET的影响。

目前,针对SET的研究主要集中在N阱,以PMOS管作为载体进行的研究[7-12],但随着器件尺寸的减小,P阱接触布局也会对器件的抗辐射性能产生显著影响。目前研究载体的特征尺寸较大,但半导体工艺技术的进步迅速,缺少先进器件的仿真研究。同时,针对不同偏置下,阱接触布局对反相器SET脉宽的研究没有系统的总结,无法评判阱接触布局对器件整体抗辐射加固性能的影响。对P阱接触的研究停留在现象层面的分析总结[17-21]。现阶段关于P阱接触面积对CMOS反相器的影响情况、机制探索及物理过程的研究报道较少,相关工作需补充和完善。因此,本文开展了P型阱接触面积对CMOS反相器SET脉冲宽度影响的研究,可为CMOS反相器抗辐射性能研究提供参考。

1 TCAD建模与模型设置

1.1 模型构建与验证

基于Sentaurus 2018构建了40 nm体硅双阱工艺CMOS反相器TCAD 仿真模型,如图1所示。

图1 40 nm体硅双阱工艺CMOS反相器TCAD 仿真模型Fig.1 TCAD simulation model of 40 nm bulk silicon double-well process CMOS inverter

NMOS晶体管和PMOS晶体管位于器件中心,尺寸分别为Wn∶Ln=160 nm∶500 nm,Wp∶Lp=100 nm∶500 nm,PMOS管与NMOS管共用栅极,晶体管之间的间距为940 nm,P阱接触和N阱接触分别位于晶体管两侧,间距为200 nm。P阱和N阱的阱深均为1 000 nm,掺杂峰值浓度均为3×1017cm-3。通过调整倒角、轻掺杂浓度及源漏掺杂浓度等工艺参数,对CMOS反相器器件模型进行了校准,模型校准的基准与Ding等[22]建立的阱接触对SEE影响的器件模型一致。

1.2 模拟条件

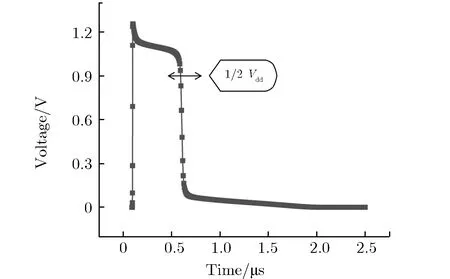

器件的工作电压设置为1.1 V和0 V,重离子轰击的LET值为30 MeV·cm2·mg-1,并假设在整个轨迹上保持不变。粒子垂直入射,分别轰击在PMOS和NMOS的漏极中心,入射粒子具有高斯分布特性,径向特征距离为0.1 μm,粒子入射至器件时间为0.1 ns。在后续仿真的研究过程中,通过观察反相器输出电压纵坐标的1/2Vdd(工作电压)处,脉冲持续的时间长度来表征SET脉宽宽度,图2为SET脉宽示意图。仿真模拟过程中使用的物理模型包括掺杂相关的非平衡载流子(Shockley-read-hall,SRH)复合和俄歇(auger)复合、雪崩击穿模型(avalanche)、迁移率模型(包括迁移率和掺杂浓度的关系(doping dep)、迁移率和高电场关系(high field saturation))和禁带变窄模型(band gap narrowing)。

图2 SET脉宽示意图Fig.2 Schematic diagram of SET pulse width

2 P阱接触面积对瞬态脉宽的影响

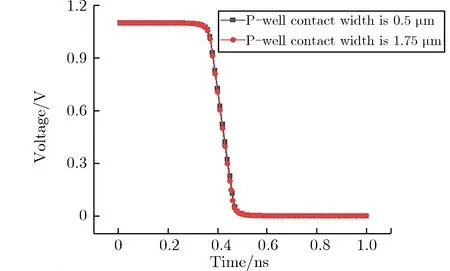

为研究P阱接触面积变化对SET瞬态脉冲宽度的影响,保持N阱接触面积不变,宽为300 nm,长为500 nm,P阱接触宽为300 nm不变,长度从0.5 μm到1.750 μm递增。P阱接触面积对反相器电学参数的影响如图3所示。由图3可见,P阱接触面积增大后对器件电学特性没有明显影响。本文基于该结果开展了后续研究。

图3 P阱接触面积对反相器电学参数的影响Fig.3 Influence of P-well contact area on electrical parameters of inverter

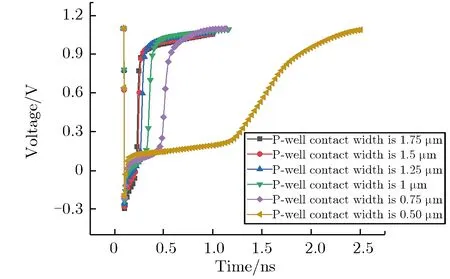

2.1 Nhit情况

Nhit P阱接触面积对SET脉冲宽度的影响如图4所示。由图4可见,反相器输入电压为1.1 V时,重离子轰击P阱有源区漏极中心,反相器产生的SET脉冲宽度随P阱接触面积增大而减小。这一现象与现有阱接触面积的研究结论相仿,增大阱接触面积可有效减小双极放大因子[10],在双阱工艺中的双极放大效应会随N阱接触面积的增大而被抑制,从而加强器件的抗SEE能力[7]。P阱接触面积增大对SET脉冲宽度有明显的减小作用。

图4 Nhit P阱接触面积对SET脉冲宽度的影响 Fig.4 Influence of P-well contact area on Nhit SET pulse width

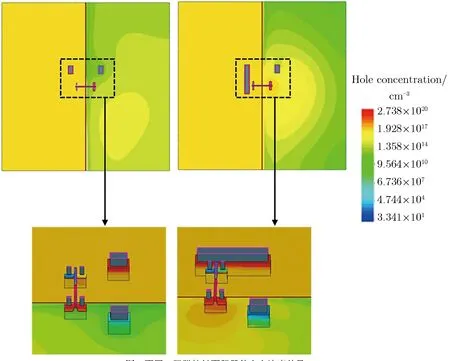

P阱接触面积增大后,Nhit轰击产生的空穴载流子大部分被阱接触所吸收,P阱接触面积越大,吸收的载流子数量越多,使轰击位置因重离子轰击而产生的空穴数量减少。当P阱接触面积增大到整个P阱面积占比的19.2%时,轰击产生的空穴载流子大部分被阱接触吸收,且阱接触的吸收能力达到饱和,因此阱接触面积对SET脉宽减小的趋势在阱接触面积增大的过程中逐渐变缓。图5为不同P阱阱接触面积器件空穴浓度差异。由图5可见,P阱接触面积增大后,N型有源区空穴载流子浓度下降。

图5 不同P阱接触面积器件空穴浓度差异Fig.5 Difference in hole concentration of devices with different P-well contact areas

Nhit的情况下,轰击点在NMOS管漏极中心的位置,NMOS管的主要电荷收集机制是扩散和漂移,P阱接触会快速收集轰击点产生的空穴。在重离子轰击到器件后,PN结周围的载流子在内建电场的作用下被收集,通过源极-体区-阱接触之间的通路形成电流,增大阱接触面积可减小这个回路上的电阻,增大通过通路的电流,因此最终SET脉冲宽度得到了有效减小[23]。

2.2 Phit情况

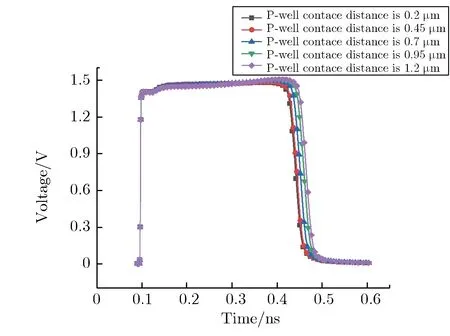

Phit P阱接触面积对SET脉冲宽度的影响如图6所示。

图6 Phit P阱接触面积对SET脉冲宽度的影响Fig.6 Influence of P-well contact area on Phit SET pulse width

由图6可见,反相器输入为0时,重离子轰击N阱中有源区漏极中心,Phit情况下反相器产生的SET脉冲宽度随P阱接触面积增大而增大。这个现象不仅与传统加固手段相反,甚至与第2.1节Nhit的轰击情况相反,增大P阱接触面积在Nhit情况下有显著减小SET脉冲宽度的效果,但在Phit情况下起反作用,这使增大P阱接触面积成为一种双向性手段。

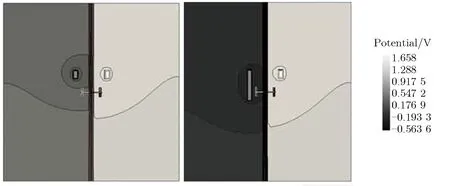

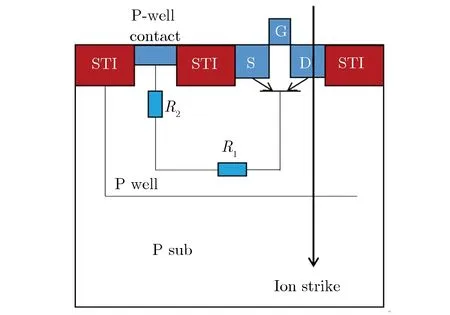

PMOS的主要电荷收集机制是双极放大效应,不同P阱接触面积器件电势差异如图7所示。由图7可见,整个器件的体电势趋于稳定,增大P阱接触面积加速了轰击位置体区内重离子沉积电荷的收集,同时第2.1节中证明增大P阱接触面积可减小双极放大效应,这说明此时影响器件SET脉宽的原因并不唯一。

图7 不同P阱接触面积器件电势差异Fig.7 Potential difference of devices with different P-well contact areas

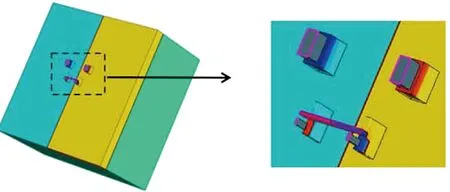

为探究Phit情况下SET脉宽变化的具体物理过程,重新建立了一个CMOS反相器模型用于分离初级收集电流与双极放大电流作为对比。无源结构器件如图8所示,在原先的器件结构上物理上去除源极结构。在进行单独施加电压的条件下,因没有源极结构器件不能形成PNP型寄生晶体管结构,漏极的输出电流是初级收集电流(包括扩散和漂移收集的电流)。

图8 无源结构器件Fig.8 No source structure device

将初级收集电流与先前器件的漏极输出电流相减可得到器件的双极放大电流。Phit情况下P阱接触对电流的影响如图9所示。

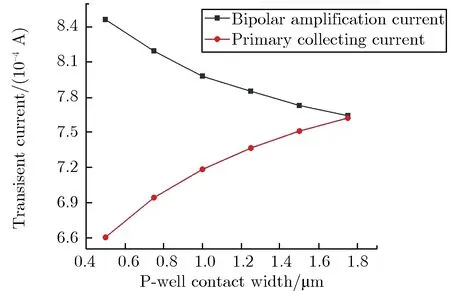

图9 Phit情况下P阱接触宽度对电流的影响Fig.9 Influence of P-well contact width on current under Phit condition

由图9可见,轰击N阱漏极中心后,双极放大电流在P阱接触面积增大的过程中减小,同时初级电流随之增大。说明双极放大效应在这个过程中得到了抑制,但加剧了初级收集的过程。原因是P阱接触、P阱、N阱、N阱接触之间形成的电流通路会受P阱接触面积的影响,Phit情况下,P阱接触面积对电流的影响如图10所示。

图10 电阻通路Fig.10 Resistance path

由图10可见,当P阱接触面积增大时,R2电阻减小,电阻通路上的分压减小利于体电势的稳定,从而减小了轰击PMOS漏极中心产生的双极放大效应[9]。

P阱接触快速吸收了N阱轰击位置的空穴,阱电势被维持在一个高电平的状态,稳定高电位的电势可减小双极放大效应的影响,但体电势处于高电平会在阱内形成一个更强劲的内建电场,从而加剧漂移收集。轰击位置处大量空穴载流子被增大后的阱接触吸收,至此N阱中产生的强烈内建电场会加剧N阱漏极对电荷的吸收,吸收能力随内建电场强度的增强而增强。所以Phit的情况下,P阱接触虽抑制了双极放大效应,但加剧了漂移收集。在更严重的漂移收集及削弱后的双极放大效应的叠加影响下,SET脉冲宽度整体随P阱接触面积增大后产生的强内建电场强度增加而增加。

PMOS的主要电荷收集过程是双极放大,但在大面积的P阱接触吸收轰击处的空穴后产生的强内建电场使漂移收集加强。根据图9所示的收集电流,当阱接触面积达19.2%时,初级收集电流增大至与双极放大电流几乎一样,说明在此时漂移收集已成为比双极放大效应更严重的电荷收集环节了,所以在Phit轰击之后SET脉宽不减反增。

3 P型阱接触位置对瞬态脉宽的影响

为研究P阱接触与晶体管间的距离对SET脉宽的影响,使除阱接触与晶体管之间距离外的条件恒定不变,调整分布距离从0.2 μm至1.2 μm。P阱接触位置对反相器电学参数影响如图11所示。由图11可见,P阱接触位置的变化对反相器的特征电参数没有明显影响,后续研究将基于这个前提展开。

图11 P阱接触位置对反相器电学参数影响Fig.11 Influence of P-well contact position on electrical parameters of inverter

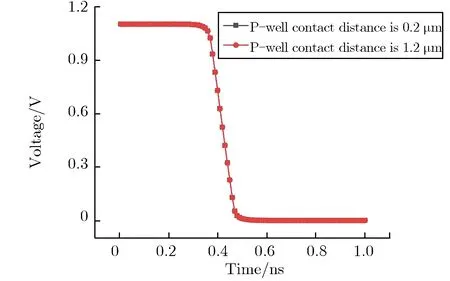

Nhit情况下P阱接触位置对SET脉宽的影响如图12所示.由图12可见,Nhit情况下随着P阱接触与晶体管之间的距离变大,SET脉冲宽度随之增大。阱接触与晶体管之间的距离越近,高能粒子轰击后产生的空穴可更快地被阱接触吸收。

图12 Nhit情况下P阱接触位置对SET脉宽的影响Fig.12 Influence of P-well contact position on SET pulse width under Nhit condition

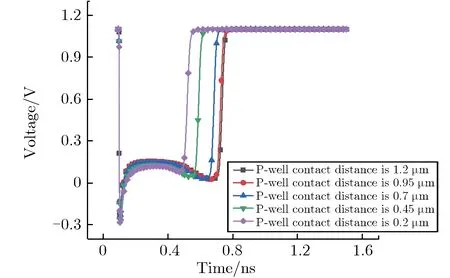

Phit情况下P阱接触位置对SET脉冲宽度的影响如图13所示。

图13 Phit情况下P阱接触位置对SET脉宽的影响Fig.13 Influence of P-well contact position on SET pulse width under Phit condition

由图13可见,在Phit情况下,减小晶体管与阱接触之间的距离对SET脉冲的抑制起到了反作用,两者之间得电阻通路较短时,阱接触吸收空穴的速度较快。比较图13和图12还可见,Phit情况下阱接触距离对SET脉宽的增大幅度小于Nhit情况下的减小幅度。这与第2节对P阱接触面积增大后在Nhit情况下SET脉冲宽度增大的结论具有一致性,P阱接触对空穴载流子的吸收是导致SET脉宽变化的原因。P阱接触面积的增大对Nhit轰击减缓了双极放大效应的同时又加剧了漂移作用,两者作用的叠加下,阱接触位置的距离对SET脉冲宽度的影响并不是很大。

4 结论

本文研究了40 nm体硅双阱CMOS反相器中P阱接触对单粒子瞬态效应的影响,通过TCAD 3维模拟发现,重离子辐照下,P阱接触的面积及分布在不同偏置下会对SET有全然不同的效果。当器件输入高电压时,轰击P阱中漏极中心敏感区域,缩减P阱接触与晶体管之间的距离或加大P阱接触面积可有效减小Nhit的单粒子瞬态脉冲宽度。当器件输入低电压时,轰击N阱中漏极中心敏感区域,增大P阱接触面积及缩短P阱接触与晶体管之间的距离反而会使SET脉宽随之增大。阱接触可吸收载流子,减小轰击产生的电子-空穴对产生的影响,同时也会因电势的高低形成不同强度的内建电场而影响漂移扩散的收集。研究结果表明,Nhit情况下改变P阱接触布局可有效提高器件的抗SET能力, Phit情况下对P阱接触布局的变化会降低器件的抗SET能力。