C 波段高效率内匹配功率放大器设计*

2023-10-07刘鸿睿赵宏亮尹飞飞

刘鸿睿,赵宏亮,尹飞飞

(辽宁大学 物理学院,辽宁 沈阳 110036)

0 引言

在射频功率放大器中,高功率密度、高效率是人们一直追求的目标。目前主流的射频功率放大器设计方案分为单片微波集成电路(Monolithic Microwave Integrated Circuit,MMIC)、射频功率模块和内匹配三种形式。内匹配功率放大器是一种混合集成电路(Hybrid Integrated Circuit,HIC),它可以将多种不同衬底材料、不同工艺的裸芯片通过粘接、焊接、共晶等工艺装配在同一个载片上。与其他两种形式相比,内匹配具有大功率、低成本、小型化的优点[1]。由于内匹配将管芯、无源电路、偏置电路分别设计在不同的衬底上,它可以实现不同工艺的优势互补。但也正是这个因素,给内匹配功放的设计带来很多不确定性。因此,高性能内匹配功率放大器是近年来研究的重点[2-3]。根据电气与电子工程师协会(Institute of Electrical and Electronics Engineers,IEEE)对电磁波频谱的划分,C 波段指的是频率在4~8 GHz 范围的电磁波,该频段包含了卫星下行频段、5G 移动通信频段、雷达频段等,用途较为广泛,具有广阔的市场前景。本文基于氮化镓高电子迁移率晶体管(High Electron Mobility Transistor,HEMT)技术,设计了一款高效率C 波段50 W 内匹配功率放大器,其在饱和输出功率48 dBm 下可以实现55% 的功率附加效率(Power Added Efficiency,PAE),同时可装配在8 mm×8 mm 载片上,实现了小型化,可广泛应用于卫星、雷达、移动通信等领域中[4-6]。

1 电路设计与仿真

1.1 指标要求

(1) 工作频率:5~5.8 GHz;

(2) 饱和输出功率:>47 dBm;

(3) 功率附加效率:55%(平均);

(4) 功率增益:>24 dB;

(5) 功率平坦度:<±0.5 dB;

(6) 工艺制程:0.25 μm GaN HEMT。

1.2 功率预算

对于高效率设计,合理的功率预算是重要一环。为了实现47 dBm 的功率输出,在设计时,末级管芯需输出48.5 dBm 的功率,以确保留有足够的余量。末级增益的确定要兼顾效率和稳定性。较高的增益有利于功率的提升,但也会降低电路的稳定性,严重的情况下导致电路自激无法使用。通常在进行功率预算时先对末级增益进行经验预估,然后进行输入输出匹配电路的原理图设计。在进行原理图设计时通过K因子判断稳定性。当放大器的S 参数满足式(1)条件时,放大器处于绝对稳定状态。否则,电路存在稳定性风险,需要调整稳定性网络,使系统达到绝对稳定状态。本文在经过一些经验预估和仿真之后,最终确定末级功率增益为10 dB。

在本设计中,采用已设计好的MMIC 作为前级电路的方案。这种复用已成熟设计的方法可大大减小设计风险,同时缩短开发周期。由于末级功率增益确定为10 dB,前级MMIC 需至少输出38.5 dBm。为了留有一定余量,最终选择饱和输出功率为40 dBm 的MMIC电路。

1.3 管芯选择

氮化镓管芯的选择要兼顾效率和功率。若管芯的栅宽过小,则无法提供足够的功率;若栅宽过宽,则会增大晶体管的输出电容,降低效率[7]。本文所使用的GaN管芯在28 V 漏极电压下C 波段功率密度大约为4 W/mm。为了输出50 W 功率,同时留有一定余量,最终决定使用16.3mm 总栅宽的管芯进行末级的设计。

对于高性能放大器的设计来说,获得准确的晶体管模型参数至关重要。其中,如图1 所示的晶体管的13 参数小信号模型被广泛使用。本文采用零偏冷管法和正偏冷管法[8]进行模型参数提取。其中,在进行末级设计时,通常最关注的是模型中归一化的Cd(s源漏电容)和Ld(漏极电感)。本文中提取结果为Cds=0.405 pF/mm,Ld=22.6 pH·mm。

图1 HEMT 的13 参数小信号模型

1.4 匹配网络设计

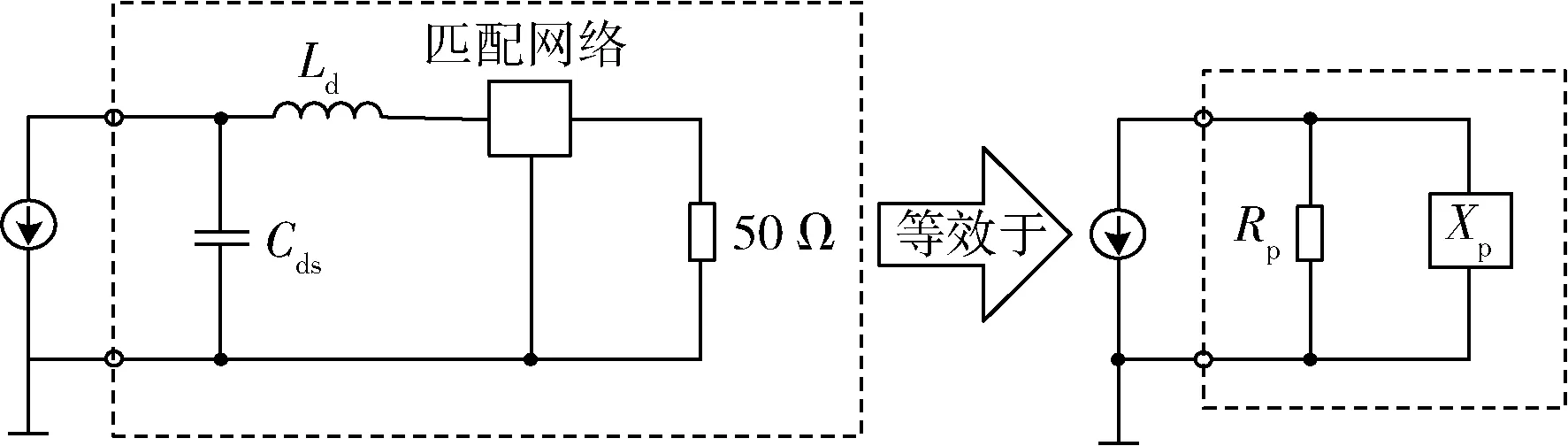

当放大器输出端处在最佳匹配状态时,管芯端面的输出阻抗可等效为一个电阻Rp和电抗Xp并联形式,输出匹配电路将这一阻抗匹配到放大器的负载阻抗(通常为50 Ω),如图2 所示。

图2 管芯电流源端面输出阻抗效为电阻Rp 和电抗Xp 并联

输出匹配电路是功放中最重要的部分,其特性直接影响功率放大器的性能。在进行输出匹配电路设计时,首先确定匹配网络的结构,然后调整谐波处理网络,确定谐波阻抗位置,最后调整基波匹配网络,选择合适的基波Rp值,使功放的各项性能满足要求。本文中功放选择J 类的匹配结构,其原理图见图3,图中R为稳定性电阻,防止功放出现自激。归一化的基波Rp的取值为120 Ω·mm,使用T 型匹配网络将基波阻抗匹配到50 Ω。对于高次谐波,其相对于Cds近似为短路状态,没有进行额外处理。

图3 功放末级原理图

理想无耗情况下输出功率和漏极效率仿真结果如图4 所示,从仿真结果来看,若输出匹配网络理想无耗,使用此结构的功放可在输出48.3 dBm 的功率下实现77%的漏极效率(Drain Efficiency,DE)。

图4 理想无耗情况下输出功率和漏极效率仿真结果

1.5 版图设计

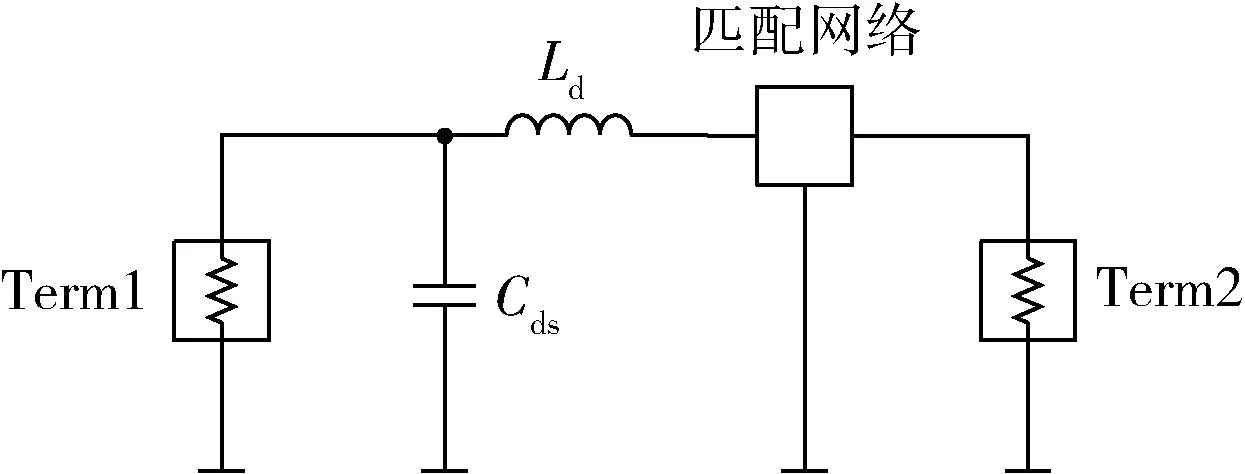

在完成原理图设计与仿真之后,需要进行版图设计,将原理图中的电容电感替换成版图中的图形。对于输出匹配电路,主要采用氧化铝陶瓷电路进行设计。由于制造工艺的限制,本文所使用的氧化铝陶瓷电路仅能制造微带线和电阻,无法制造电容,因此,电容需要采用其他衬底的陶瓷电路进行设计,与氧化铝陶瓷电路之间通过键合金线连接。对于输入匹配电路,采用砷化镓集成无源器件(Integrated Passive Device,IPD),相比于陶瓷电路工艺,IPD 可以将各种无源器件集成在同一块芯片上,精度较高,一致性较好。但其损耗较大,通常用于设计输入匹配和级间匹配电路。输出匹配电路仿真原理图如图5 所示。

图5 输出匹配电路仿真原理图

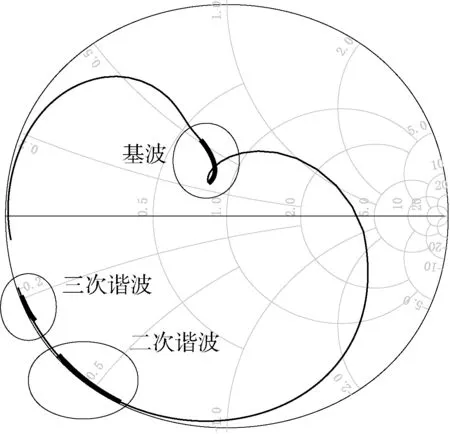

使用Keysight 公司的ADS 软件对输出匹配电路进行S 参数仿真。仿真时首先对晶体管中Cds和Ld进行等效替换,添加到匹配网络中,然后将端口1 特性阻抗设置为Rp,端口2 特性阻抗设置为50 Ω,仿真得到的S 参数结果见图6。

图6 输出匹配电路S(1,1),基波与二次、三次谐波的阻抗区域

可以看到,基波阻抗位于靠近史密斯圆图中心的感性区域,二次和三次谐波位于靠近短路点的容性区域,放大器处于J 类状态。由于高次谐波没有深入圆内阻性区域,其电压和电流是正交的,可视为谐波几乎没有功率进入匹配网络,只有基波通过匹配网络进入负载。

1.6 偏置电路设计

在射频功放中,偏置电路负责给晶体管的栅极(或基极)与漏极(或集电极)提供直流偏置,通常采用片外的λ/4 高阻抗微带线加扇形线或贴片电容进行设计。这种方法在射频放大器设计中被广泛采用,但在本设计中,其巨大的面积占用无法满足小型化的要求。此外,负责偏置的微带线为整个功放提供供电电流,其直流电流较大,在本文中供电电流最高可达5 A,过长的微带线带来的直流电阻会显著降低功放效率。本文中输出匹配电路借助其中的金线电感进行漏极直流偏置,此电感连接到50 pF 的陶瓷电容进行一次退耦,再通过载片上的1 000 pF 电容进一步短路掉射频分量,阻止其耦合到前级电路。对于输入匹配电路,由于栅极几乎不产生电流,采用高阻供电的方式进行偏置。采用这种偏置方法既有效地节省了面积,又降低匹配电路的损耗。

1.7 整体性能仿真

此功率放大器前级采用MMIC,该电路已有测试数据,因此只需要对末级功放进行仿真,就可以推算出整个功放的性能。使用ADS 软件对末级功放进行谐波平衡(Harmonic Balance,HB)仿真,仿真时输入功率38 dBm,得到功率效率曲线如如图7 所示。可以看到,功放在38 dBm 输入时平均输出功率为48.4 dBm,平均漏极效率为70%。前级MMIC 功放在输出38 dBm 时测得漏极电流为0.5 A,将其补偿到功放总电流后,功放的整体漏极效率为62%。

图7 输出功率和漏极效率版图仿真结果

2 芯片测试

采用芯片贴装、共晶焊接、金线键合等微组装工艺对芯片进行装配,如图8 所示,装配完成后对芯片进行调试与测试。通过反复调整金丝高度、芯片上预留的开路块,以及在陶瓷电路上微带弯曲的位置打金线等方式对芯片进行调试,使其性能达到最优。

图8 芯片照片

芯片测试是在漏极电压28 V,栅极电压-2.9 V 条件下进行的,采用频率1 kHz,占空比10%的脉冲工作模式。由于本设计采用的是耗尽型的HEMT,在零栅压下晶体管沟道是导通的,因此栅极和漏极的上电顺序要严格遵循先栅后漏的原则,防止器件在零栅压下产生大电流被烧毁。测试时对输入功率由小到大进行扫描,得到功放在饱和状态下的功率曲线和效率曲线。

2.1 末级性能测试

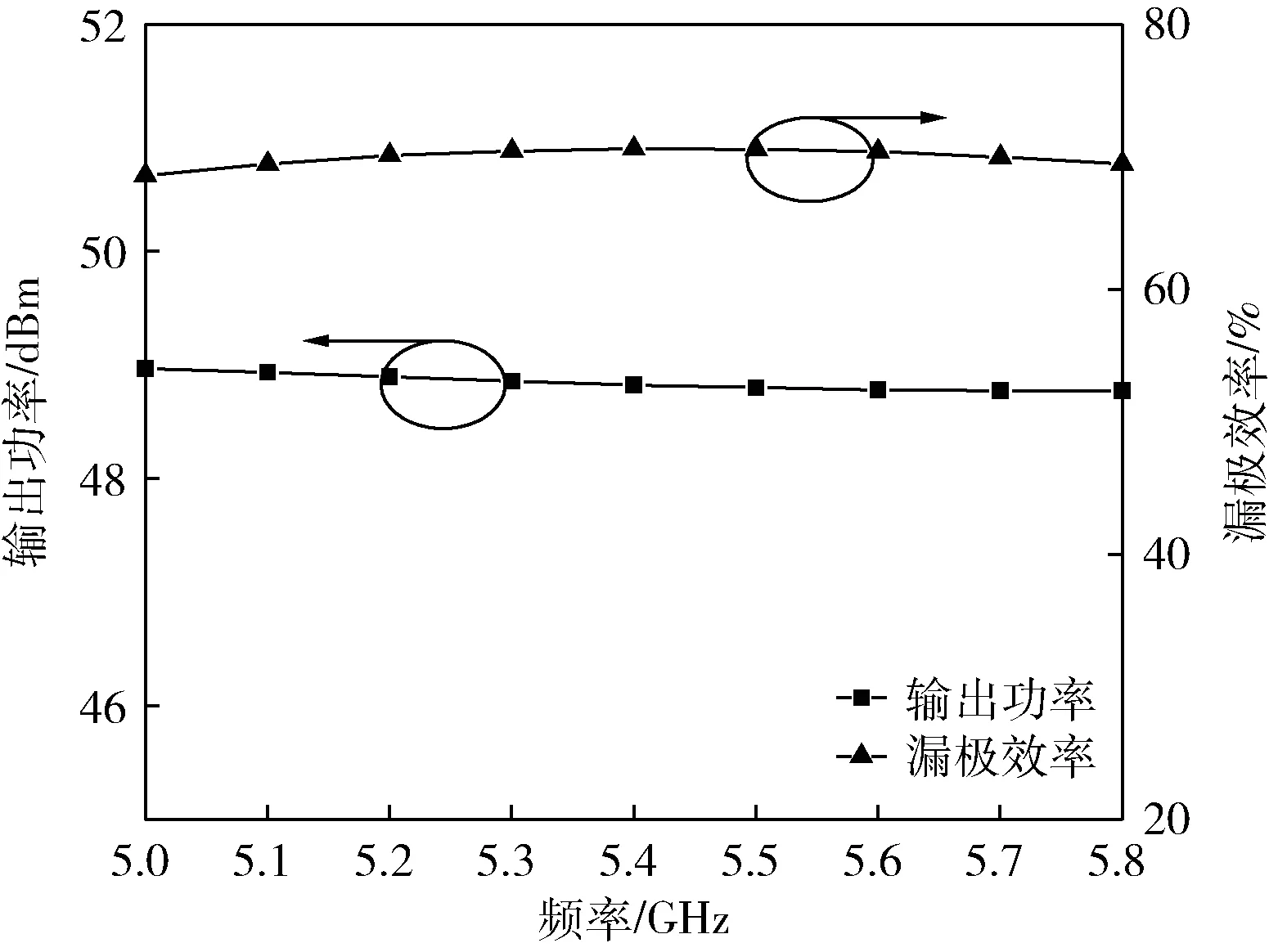

末级性能的测试项主要包括末级的饱和功率和在饱和功率输出时的漏极效率。测试时需测量输出功率和末级管芯的漏极电流,同时计算放大器末级的漏极效率。相较于整体性能测试,由于排除了前级电路的影响,末级的性能测试能够更准确地分析判断放大器的工作状态。因此,此放大器调试的前期大多采用末级测试的方法。调试的结果如图9 所示。可以看到,在频带内,其平均输出功率为47.8 dBm,平均漏极效率为66%,最高点达到67%。测试结果频带内曲线趋势与仿真结果基本一致。

图9 功放末级输出功率和漏极效率实测结果

2.2 整体性能测试

整体性能测试方法与单末级性能测试相似,区别在于,考虑到前级电路对放大器性能的影响,整体性能测试时漏极电流需测量放大器总漏极供电电流。相较于末级性能测试,由于考虑到前级电路的影响,整体性能测试的结果为功放的真实性能。因此在调试的后期,会采用整体性能测试得出放大器的整体性能。测试结果表明,此放大器在输入功率23 dBm 可以输出48 dBm 功率,功率增益25 dB,同时还可以达到55%的功率附加效率和优于0.4 dB 的功率平坦度。此测试结果与仿真结果基本相符,由于辐射、互耦、失配等非理想因素影响,测试结果与仿真结果有一些偏差,主要体现在功率和效率的退化。在设计时已为考虑到这一点并留有一些余量,此偏差在可接受范围内,满足指标要求。

表1 列出了同类成果的性能指标,从功率、效率、增益等综合性能来看,本文设计的功率放大器具有一定的先进性。

表1 同类研究成果性能比较

3 结论

本文设计并实现了一款C 波段50 W 内匹配功率放大器。采用J 类的匹配网络结构,实现了高效率。同时采用紧凑的版图布局,使电路在保证高性能的同时实现了小型化。由于受测试条件所限,本文中功放调试时金线只能采用手动打线的方式,其实测效率比仿真低4%。若使用自动化设备进行装配和打线,其一致性和精度会大大提高,性能有望进一步提升。