利用分时刷新和位置约束的卫星载荷BRAM抗辐照设计方法*

2023-09-28孙鹏跃刘旭辉毛二坤黄仰博张书政楼生强

孙鹏跃,刘旭辉,毛二坤,黄仰博,张书政,楼生强

(国防科技大学 电子科学学院, 湖南 长沙 410073)

静态随机存取存储器(static random access memory,SRAM)型现场可编程的门阵列(field programmable gate array,FPGA)具有信息密度大、性能高、开发成本低以及可重新编程的特性,在空间领域具有越来越多的应用价值,但随着SRAM型FPGA集成度的提高,对其在复杂的太空辐照环境工作的可靠性提出了更高的要求[1-3]。空间单粒子效应主要可以分为三类:配置存储器翻转、用户逻辑翻转以及控制单元翻转[4-6]。配置存储器翻转占所有空间单粒子翻转事件的90%以上,对载荷配置项的可靠性影响极大,一直以来是载荷抗辐照可靠性设计的重点,形成了一系列成熟、有效的抗辐照设计方法[7-9]。相比配置存储器,控制单元发生单粒子翻转的概率极低,一般为百年级以上[10-11],且难以通过单片FPGA实现加固,故目前载荷抗辐照设计一般不考虑控制单元的加固。而对于用户逻辑部分而言,其发生单粒子翻转的概率较高[12-13],且与用户设计密切相关,难以形成体系化的抗辐照加固方法,目前已逐渐成为空间载荷抗辐照设计的瓶颈,特别是其中的块随机存储器(block random access memory,BRAM),难以通过传统的刷新操作消除空间单粒子翻转的积累,是目前造成SRAM型FPGA空间单粒子异常的主要原因之一[14]。为此,主要研究SRAM型FPGA中BRAM资源的抗单粒子翻转加固方法。

文献[15]提出一种基于三模冗余的BRAM加固方法,但是该方法随着存储器数量的增多以及读取速度的提高,对存储的控制时序的要求也随之提高,不适用于对面积和功耗要求较高的场合。在此基础上,文献[16]提出了一种部分三模冗余的加固方法,仅对关键功能模块进行三模冗余,在一定程度上节省了面积的开销。文献[17]提出了一种基于格雷码的BRAM加固方法,可以有效降低位翻转发生的概率,但其自身可能存在可靠性问题,编码和解码电路都有可能发生单粒子翻转的错误,导致最后的数据错误。

对于星载FPGA配置项而言,资源使用情况一般都严格受限,在进行抗空间辐照加固设计时,往往需要在可靠性和资源消耗之间折中[18]。并且,FPGA设计所消耗的资源越少,其在轨抗辐照可靠性必然会越高。因此,如何针对不同载荷配置项设计特点,设计一种在资源消耗和可靠性之间折中的BRAM抗辐照加固方法,对于提升载荷配置项抗辐照性能具有重要意义。本文在分析传统BRAM抗辐照加固方法不足的基础上,提出了一种基于分时刷新和位置约束的卫星载荷BRAM抗辐照加固方法:一方面通过监控内部算法时隙,实现BRAM的分时刷新;另一方面通过位置约束固定BRAM三模冗余后3块BRAM的位置,大幅降低三模后BRAM被同时打翻两模的概率。所述方法能够在增加极少可配置逻辑块(configurable logic block,CLB)资源的基础上,有效提升BRAM的抗辐照可靠性。

1 传统BRAM抗辐照加固方法的不足

SRAM型FPGA中含有丰富的BRAM存储资源,是星载FPGA配置项中最常用的知识产权(intellectual property,IP)核,广泛应用于数据缓存和参数存储等,可以实现单口存储器、双口存储器以及先入先出队列(first input first output,FIFO)等功能。BRAM是星载FPGA用户逻辑中单粒子发生概率最高的,占2.9%[19]。但由于BRAM中存储的数据一直处于动态应用中,难以实现类似配置数据的定时刷新设计,因此,BRAM中累积的单粒子翻转难以消除。

对于数据缓存类BRAM而言,尽管BRAM数据为中间结果,一定时间后会被算法自动修复,但BRAM数据错误期间已经对算法后续数据流产生了影响。而对于参数存储类BRAM而言,用户要求BRAM中数据保持不变,但在空间辐照条件下,即使对参数存储BRAM进行了三模冗余,也无法解决单粒子累积造成的数据错误。因此,在星载配置项BRAM加固中,必须设计相应的单粒子累积消除方法,以保证数据的正确性。

传统的单粒子累积效应消除方法主要有刷新和纠错编码两类。对于刷新而言,常用架构如图1所示。

图1 刷新纠错方法基本架构Fig.1 Basic architecture of refreshing error correction method

纠错编码方法不单独占用BRAM端口,不会造成BRAM资源的浪费,但纠错编码方法并没有从根本上纠正BRAM中数据的单粒子翻转,只是在使用BRAM数据时能够检测2 bit错误并纠正1 bit错误。但随着时间的积累,当BRAM中数据发生多比特错误时,纠错编码方法将失效。

2 基于分时刷新和位置约束的BRAM加固方法

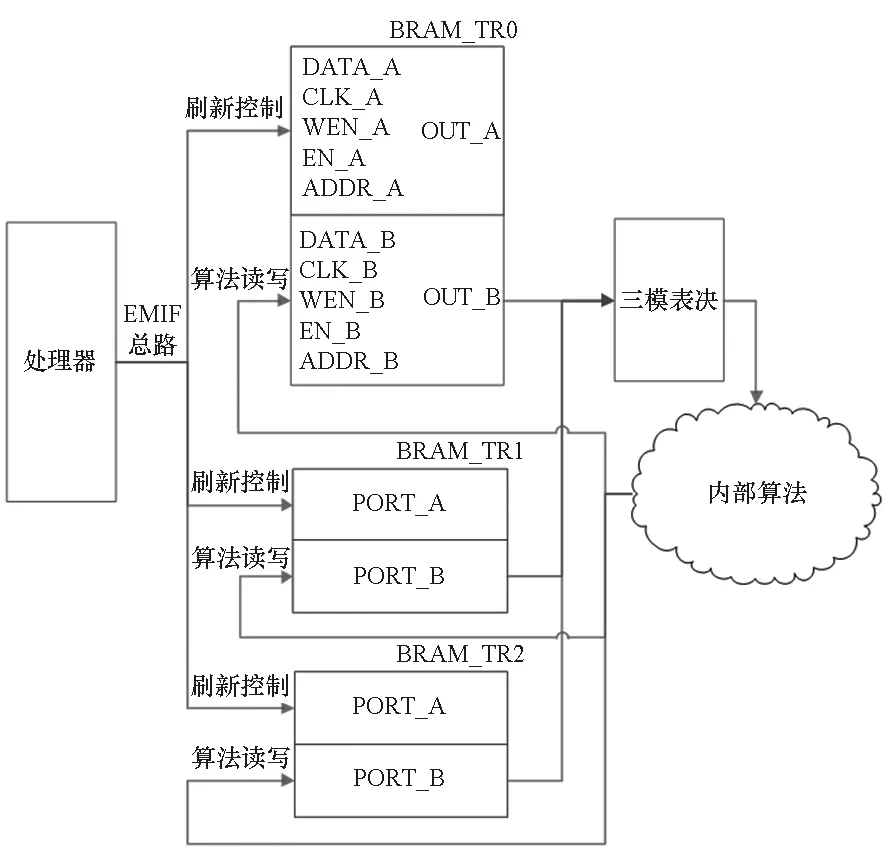

为了从根本上解决BRAM单粒子翻转的积累问题,必须采用三模冗余加刷新的策略。而针对传统外部处理器刷新方法消耗资源,且容易发生BRAM读写冲突的问题,本文提出了基于分时自刷新的星载配置项BRAM加固方法,具体架构如图2所示。BRAM及自刷新控制逻辑三模冗余设计后共有3条路径(TR0、TR1、TR2),图2中仅对TR0路径进行了细化,每条路径又包括了自刷新支路和算法读写支路,其中算法读写支路实现内部算法的BRAM访问,自刷新支路实现BRAM数据的自刷新控制。分时自刷新设计的主要思想是通过算法监控模块识别内部算法访问BRAM的空闲时段,自刷新控制模块根据当前刷新地址,将BRAM数据回读,并经三模表决纠错,再将纠错后的数据回写BRAM,并累加地址继续刷新。一旦算法监控模块检测到内部算法忙,则立即停止刷新,并记录当前刷新地址,待下次内部算法访存空闲时继续刷新。

图2 基于分时刷新的BRAM加固方法基本架构Fig.2 Basic architecture of BRAM hardening method based on time-sharing refreshing

可以看到,上述架构不需要外部处理器干预即可完成BRAM的自刷新功能。内部算法监控模块可确保BRAM自刷新在整个算法访存空闲状态下执行,因此,其不需要单独占用一个BRAM端口,也不会造成BRAM访问冲突。通过上述架构设计,卫星载荷FPGA能够自主完成BRAM自刷新加固,不会造成BRAM冲突和资源浪费,仅需要增加少量的CLB资源即可实现。

算法监控模块一般需要根据不同FPGA配置项功能进行设计,实现比较简单。而对于自刷新控制模块而言,可将其设计成通用化的共用基础模块(common building blocks,CBB),适用于不同的载荷FPGA配置项,提升开发效率。自刷新控制模块主要通过有限状态机(finite state machine,FSM)实现,其状态定义如下:

S0:空闲状态。复位后处于该状态,若BRAM处于内部算法访问忙状态,则FSM一直处于空闲状态,否则,进入S1状态。

S1:BRAM数据读取状态。当检测到BRAM访问空闲时,进入自刷新数据读取状态,当BRAM数据读取完成后,进入S2状态。

S2:BRAM数据写入状态,在该状态将三块BRAM的读取数据通过表决器进行表决,以修正单粒子翻转错误,再将表决后的数据进行回写,消除BRAM中的累积错误,写入完成后进入S3状态。

S3:单次刷新完成状态。进入该状态说明完成了BRAM单地址数据刷新,并控制刷新地址累加,并返回S0状态,继续下一地址刷新。

具体状态转移过程如图3所示。

图3 自刷新控制模块状态转移图Fig.3 State transition diagram of self-refreshing control module

SRAM型FPGA采用特殊设计的开关矩阵以提升面积利用率和信号传输质量。BRAM资源也有对应的开关矩阵和BRAM互联配置资源,若上述资源发生单粒子翻转,可能造成三模设计中的两模同时发生错误,造成载荷功能异常。造成上述问题的根本原因是两个BRAM位置分布超过了安全的几何布线间隔,使得单粒子翻转有可能影响相邻两块BRAM的功能同时异常。

而在星载FPGA配置项实现过程中,用户一般不会对布局布线过程进行控制,电子设计自动化(electronic design automation,EDA)工具为达到好的布线结果,往往将三模后的BRAM布局在邻近位置,会造成三模后超过2块BRAM布局位于同行或者同列的情况,进而导致单粒子翻转造成三模后设计发生功能异常的概率大幅提升。为此,提出了基于位置约束的BRAM布局方法,鉴于星载FPGA设计资源占用率一般较高,若采用复杂的位置约束和迭代策略,很有可能造成整个设计布线失败,本文在EDA工具对三模后设计进行布局布线时,增加简单的BRAM位置约束脚本,将BRAM布局在指定的位置上。

通过将BRAM三模冗余后各冗余模块的布线区域从几何上分割开,避免任意两个BRAM共用一个互联矩阵和可编程互连线相邻的情况,从根本上降低单粒子翻转引起多模设计功能同时异常的概率。

3 试验验证

主要从卫星载荷FPGA BRAM数据自刷新和位置约束两个方面对BRAM抗空间辐照设计方法进行了改进,为了验证所述加固方法的有效性,下面从地面故障注入试验、重离子辐照试验以及卫星载荷在轨实测情况三个层面对本文算法的性能进行验证。

目前地面故障注入试验主要是针对SRAM型FPGA配置数据进行故障注错,无法对用户逻辑部分,如BRAM存储数据进行故障注入[20],因此,地面故障注入试验难以验证BRAM自刷新设计的性能,但故障注入试验可实现对BRAM互联部分的故障注入,进而对BRAM位置约束设计的性能进行评估。

通过故障注入试验对BRAM位置约束的性能进行验证。提出一种基于配置数据异常率(rate of fault configuration bits, RFCB)的FPGA配置数据故障注入评估指标,其更容易通过故障注入试验获取,能够直观反映载荷FPGA设计抗辐照设计的性能,具体定义如下:

(1)

式中:be为会引起配置项功能异常的比特数,可通过故障注入试验测试,bT为配置数据总比特数。对于本文关注的BRAM互联而言,bT专指BRAM互联部分总比特数,对于XQR2V3000型FPGA而言,bT为4 224 bit。

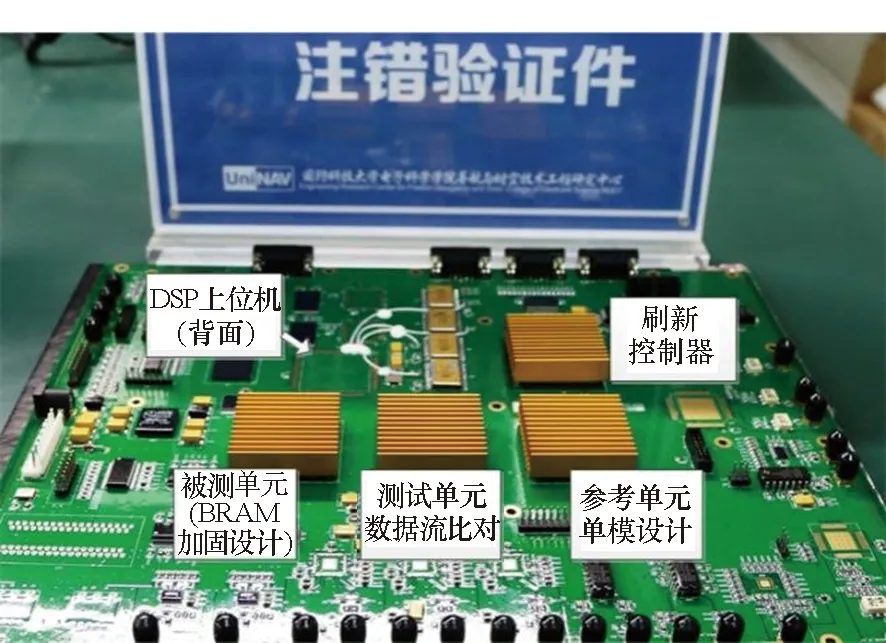

针对BRAM位置约束故障注入采用载荷配置项故障注入测试系统,具体组成如图4所示,主要包括参考单元、被测单元、测试单元、刷新控制器以及上位机组成,其中上位机由数字信号处理器(digital signal processing,DSP)实现,其他4个单元均由Xilinx XQR2V3000型FPGA实现。参考单元运行被测配置项的单模设计,作为标准参考数据流;被测单元运行采用本文所述的BRAM加固后的三模设计;测试单元完成被测单元和参考单元数据流的采集和比对功能;刷新控制器主要负责对被测FPGA的动态局部刷新,以及对所有FPGA的上电加载;上位机通过外部存储器接口(external memory interface,EMIF)与其余单元通信,控制被测单元和参考单元数据流的生成,并记录测试结果。

图4 故障注入测试系统结构图Fig.4 Structure of fault injection test system

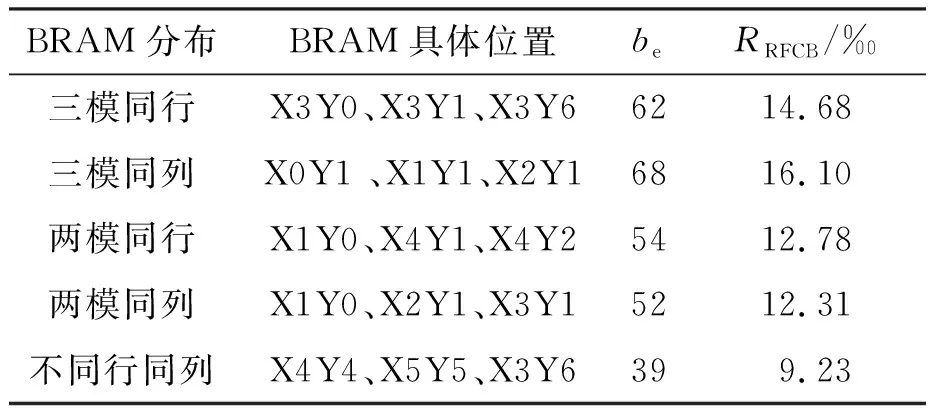

通过上述故障注入平台,通过位置约束脚本修改被测单元中三模BRAM的位置,对不同BRAM位置约束情况下BRAM互联部分的异常比特率进行测试,具体测试结果如表1所示。

表1 不同BRAM位置约束下测试结果Tab.1 Test results under different BRAM location constraint

测试结果表明,同一功能BRAM三模后3块BRAM位于同行或者同列时,单粒子翻转造成功能异常的RRFCB最高;当有两模同行或同列时,RRFCB有一定下降;当三模BRAM不同行同列时,RRFCB明显下降,相比于三模同列情况降低了约42.6%。上述结果仅为单一BRAM位置约束后的可靠性改善,若对更多BRAM进行位置约束,则可靠性改善也将更为明显。当然,位置约束在一定程度上降低了EDA软件布局布线优化的自由度,甚至可能造成布局布线失败,因此,在实际应用过程中,需要根据实际设计选择性地对关键BRAM进行位置约束设计。

为验证所述方法对星载设计面积和速度的影响,采用SM4算法对分时刷新和位置约束BRAM加固方法前、后的资源占用率和速度结果进行对比分析,以卫星载荷常用的XQR2V3000器件为例,SM4算法运算过程中的S盒(substitution box,SBOX)通过BRAM实现,为提升运算效率,采用两个SBOX进行并行运算,面积和速度评估结果如表2所示。可以看到,针对SM4算法,增加SBOX BRAM分时刷新和位置约束加固方法后,三模设计的4输入查找表仅增加84个(9.24%),寄存器仅增加81个(9.93%),时钟频率仅下降18.234 MHz(8.52%)。实际上,上述资源消耗并不会随着原有算法复杂度的提升而大幅增加,因此,对于更为复杂的设计而言,其资源增加的比例将会更小,甚至忽略不计,但速度的下降可能随着原有算法复杂度的提升而更为明显。

表2 不同设计面积和速度对比分析Tab.2 Comparison of area and clock frequency for different design

为进一步评估基于分时刷新的BRAM加固设计性能,2018年11月,在兰州中科院近代物理研究所,采用兰州重离子加速器产生的Ta离子,线性能量传输(linear energy transfer,LET)值为81.35 MeV·cm2/mg,对卫星载荷进行了重离子辐照试验。该型载荷研制阶段分为A星和B星两个阶段:在A星阶段由于未对存储关键参数的BRAM进行针对性加固设计,仅进行了三模冗余加固,存在单粒子翻转积累的问题,导致其在轨可靠性不太理想。在B星阶段,采用了本文所述的基于分时刷新和位置约束的BRAM抗辐照加固方法。重离子辐照试验是在该型卫星载荷B星发射前进行的可靠性评估试验,对A星配置项和B星配置项进行了对比测试,测试过程以单粒子功能中断达到5次,或离子总注量达到107个/cm2为辐照停止准则,上述两个条件以先达到者为准。辐照试验可靠性评价指标为单粒子功能中断截面,其主要表征了单个粒子辐射到器件单位面积上发生单粒子功能中断的事件的概率,是表征被测器件对单粒子效应敏感程度的公认指标,其定义如下:

(2)

式中,N为单粒子功能中断次数,F为器件单位截面上入射粒子的总数。辐照试验测试结果如表3所示。

表3 辐照试验测试结果Tab.3 Results of irradiation tests

可以看到,相比于A星,B星单粒子功能中断(single event functional interrupt,SEFI)截面从5.40×10-4cm2下降到9.92×10-5cm2,下降约81.63%,可靠性大幅提升。尽管辐照试验无法直接对BRAM改进部分进行性能评估,但相比A星阶段设计,B星阶段可靠性设计改进主要集中在BRAM加固设计上,因此上述结果在很大程度上证明了本文所述方法的有效性。

通过目前该型载荷的在轨运行情况,进一步验证基于分时刷新和位置约束的BRAM加固方法的性能。该型卫星载荷A星阶段共计3颗卫星,由于A星阶段BRAM加固设计不充分,其在轨发生了多次单粒子翻转异常,2015年8月至2017年9月期间,3颗卫星共计出现了7次在轨异常,后续经异常归零分析,7次在轨单粒子翻转异常的分析结果汇总如表4所示。可以看到,在所有7次在轨单粒子异常中,BRAM参数单粒子累计异常占42.9%,是造成该型工程在轨异常的主要原因。在B星阶段,采用了基于分时刷新和位置约束的BRAM抗辐照加固方法,目前25颗B星在轨运行未发生一次单粒子翻转异常,这充分证明了本文所述加固方法的有效性。

表4 在轨单粒子翻转异常的分析结果汇总Tab.4 Summary of analysis results of single event upset on navigation satellites

4 结论

尽管目前针对SRAM型FPGA配置文件抗空间辐照可靠性设计已形成一系列成熟技术,但针对用户逻辑部分,特别是BRAM的可靠性设计,相关研究还比较缺乏。传统针对BRAM的刷新设计虽然能够消除单粒子翻转的积累,但存在资源消耗大,且存在BRAM访问冲突造成在轨功能异常的风险。本文提出了基于分时刷新和位置约束的BRAM抗空间辐照可靠性设计方法,通过监测内部算法流程,通过时分复用的方式实现FPGA对BRAM的自刷新设计,并通过BRAM的位置约束有效降低单粒子翻转造成多模BRAM同时异常的概率。通过故障注入试验、重离子辐照试验以及在轨实际运行情况三个层面,对本文所述方法的性能进行了充分验证。然而,所述BRAM自刷新方法与用户设计密切相关,通用性不够强,需要根据FPGA内部算法进行针对性设计。另外,位置约束方法在FPGA资源比较紧张的情况下,可能会引起EDA软件布局布线性能下降,甚至失败,后续还需要研究位置约束设计策略,进一步提升增加位置约束后的布局布线性能。