基于FPGA的九点插值自适应图像缩放算法设计

2023-08-16朱明达辛鹏常嘉颖

朱明达, 辛鹏, 常嘉颖

(中国石油大学(北京) 信息科学与工程学院, 北京 102249)

1 引言

视频图像缩放技术目前在医疗、遥感、军事等领域有着广泛的应用[1-2],多采用FPGA进行视频图像的实时处理。当前主流的视频图像缩放算法可以分为两大类:第一类是基于传统插值的缩放算法[3],这类算法求得的插值点与图像边缘信息无关,而只与插值点周围源像素点的像素值有关。最常见的有最近邻域法、双线性插值法、双立方插值法等[4]。最近邻域法简单易实现,但生成图像质量不高。双线性插值法计算量大且本身有低通滤波器的特性,导致图像高频分量受损,图像边界变得模糊。双立方插值法虽然计算精度高,但是计算量巨大,算法复杂度高,不易于硬件实现。第二类是基于图像边缘信息的插值算法[5-7],常见的算法包括Sobel[8]、Prewitt[9]、Canny[10]等。这类算法求得的插值点与图像边缘信息相关,因此可以得到比传统插值算法更好的视觉效果,但这类算法复杂度较高,很难满足视频实时缩放的需求。

基于上述分析,本文提出一种九点插值图像缩放基本算法,该算法相比双线性插值算法减少了逻辑资源消耗,有效提高了图像缩放效果。由于最近邻域法资源量消耗小,且具有高通滤波器的特性,可以较好地保留图像边缘的高频信息,因此本文又提出一种自适应插值算法,将九点插值基本算法与最近邻域法相结合。对处于非图像边缘的像素点采用九点插值基本算法,对处于图像边缘的像素点采用最近邻域算法,在减少硬件资源使用的同时得到了比最近邻域法、双线性插值算法更好的图像缩放效果。

2 算法设计

2.1 传统缩放算法

最近邻域插值算法如图1所示,将插值点周边4个源像素点分成4个区域分别设为Area1、Area2,Area3、Area4,根据缩放比例算出的插值点坐标落在哪个区域,其像素值就取该区域源像素点的像素值。

图1 最近邻域算法Fig.1 Nearest neighbor algorithm

设插值点与周围4个邻点的距离分别为d1、d2、d3、d4,则该插值点的像素值为:

其中:g(x,y)为插值点像素值,fi(x,y)为距离插值点最近的源像素点的像素值。

双线性插值算法如图2所示,该算法将周围4个源像素点的像素值通过两次线性插值求得插值点的像素值。

图2 双线性插值算法Fig.2 Bilinear interpolation

设插值点坐标为k(x,y),周围4个源像素点设为p1、p2、p3、p4,4个源像素点坐标为p1([x],[y])、p2([x+1],[y])、p3([x],[y+1])、p4([x+1],[y+1])。设插值点与p1像素点的水平距离为u,垂直距离为v,通过两次线性插值计算可求得插值点的像素值。首先通过第一次线性插值求出f1、f2点处的像素值为:

再由f1、f2处的像素值经过第二次线性插值得到插值点处的像素值k(x,y):

最近邻域插值算法虽然运算简单,在硬件实现上需要消耗的时间资源和逻辑资源都较少,但是会引入严重的图像失真,缩放过后的图像会产生马赛克现象。双线性插值算法的图像缩放效果较好,能够很好地恢复图像的信息,但是其中包含许多小数乘法运算,即使使用定点数来代替浮点数,仍然需要消耗较多的时间资源和逻辑资源。

2.2 九点插值基本算法

针对最近邻域插值缩放效果差、双线性插值消耗硬件资源多的问题,本文提出一种九点插值基本算法。该算法无需计算小数乘法等需要消耗大量逻辑资源的运算,只需要进行加法运算和移位运算即可,最终缩放效果相较于最近邻域法缩放后的图像效果有了显著提升,但略差于双线性插值算法。算法的具体原理如图3所示。图3中黑色的点表示实际的源像素点,白色的点表示虚拟的像素点,虚拟点像素值由源像素点插值获得:

图3 九点插值基本算法Fig.3 Nine-point interpolation algorithm

将该图像区域分为4个区域分别为Area1、Area2、Area3、Area4。当插值点落在某个区域中时,其像素值取其周围4个源像素点的像素值均值,并由式(6)~(10)得到。例如当插值点落在Area1时,其像素值为:

同理可得插值点落在Area2、Area3、Area4区域内的像素值分别为:

将等式(11)~(14)两边同时乘以16,可以得到:

因此在算法实现上,将小数乘法运算改为移位相加运算,例如在计算F(Q1)像素值时,将式(11)中多个源像素点累加得到结果后,将结果右移4位,即将数值缩小16倍即可得到真正的插值点像素值,避免了小数乘法运算。减少了逻辑资源的消耗。

2.3 九点插值自适应缩放算法

根据像素点之间的相关性强弱可以将图像分为平滑区域和边缘区域。平滑区域像素点之间相关性强,用九点插值基本算法可以得到比最近邻域法更好的缩放效果;而图像边缘的像素点之间的相关性较弱,由于最近邻域法具有高通滤波的特性,在此区域使用最近邻域法可以有效保护边缘。因此,本文提出一种基于九点插值基本算法与最近邻域法相结合的自适应缩放算法,根据判定像素点位于图像平滑区还是边缘区来自动选择插值算法。

图像边缘区域检测及方向角判断采用行平均的思想,通过计算插值点所在区域4个角度的4个邻点像素点的灰度和之差,取最大值设为Amax。若Amax大于某个设定的阈值,则判定此时Amax对应的角度为此点的方向角,采用最近邻域法取该方向上源像素点或虚拟点的像素值为输出值;若Amax小于阈值,则判定为平坦区域,采用九点插值基本算法来算出插值点像素值。方向角判定如图4所示。

图4 方向角判定Fig.4 Direction angel determination

4个角度分别为0°、45°、90°、135°,通过4个方向公式来计算每个方向对应的灰度和之差:

如图5(a)所示,将一张分辨率为300×300的图像按照此方法求出图像边缘,阈值设定的越小,图像边缘显示得越清晰。边缘检测方法中阈值一般设置在60~90之间[11],本文将阈值设定为70,实验效果较好,得到的边缘图如图5(b)所示。

图5 图像边缘判定Fig.5 Image edge determination

3 算法分析

为了验证本文算法的有效性,在MATLAB中对本文方法、最近邻域法和双线性插值算法进行图像缩放实验。选用大小300×300的灰度lena图像作为原图,先将图片长宽分别缩小4倍,然后采用不同缩放算法对图像长宽分别进行4倍放大,放大后的图像与原图尺寸相同。图片经不同缩放算法处理得到实验结果如图6所示。

图6 灰度图像放大效果对比Fig.6 Comparison of grayscale image enlargement effect

由图6可见,最近邻域算法缩放的图像出现了严重的马赛克失真现象;双线性插值缩放效果比最近邻域法要好,但是图像边缘不够清晰;九点插值基本算法在平坦区域缩放算法较好,但同样在图像边缘不清晰;而九点插值自适应插值算法在图像平坦区域效果较好,同时在图像边缘区域的马赛克现象要好于前几种算法。

峰值信噪比(PSNR)是最常用的评价图像缩放效果的客观指标之一,其具体公式如式(23)所示:

其中:I代表大小为M×N的原始图像,K代表经过缩放处理后与原图像大小相同的目标图像。峰值信噪比的值越大,表示图像损失的信息越少,图像缩放效果越好。

对300×300 Lena、512×512 Baboon、480×480 Barbara、800×800 Goldhill和600×600 Peppers几张图像的长宽分别缩小4倍,然后采用不同缩放算法对图像长宽分别放大4倍,放大后的图像与原图尺寸相同,计算几张图像与原图像的峰值信噪比,结果如表1所示。

表1 算法的PSNR值对比Tab.1 Comparison of algorithm PSNR

由表1可以看出,第三列为本文提出的九点插值基本算法,其缩放效果要优于最近邻域插值算法,但略差于双线性插值算法;第四列为本文提出的九点插值自适应算法,由于其在图像边缘处对九点插值基本算法进行了算法优化,其图像质量优于其他3种算法的图像质量。九点插值自适应算法的PSNR值相比于最近邻域插值与双线性插值算法普遍高出0.5~3 dB。

4 算法硬件实现

4.1 系统组成

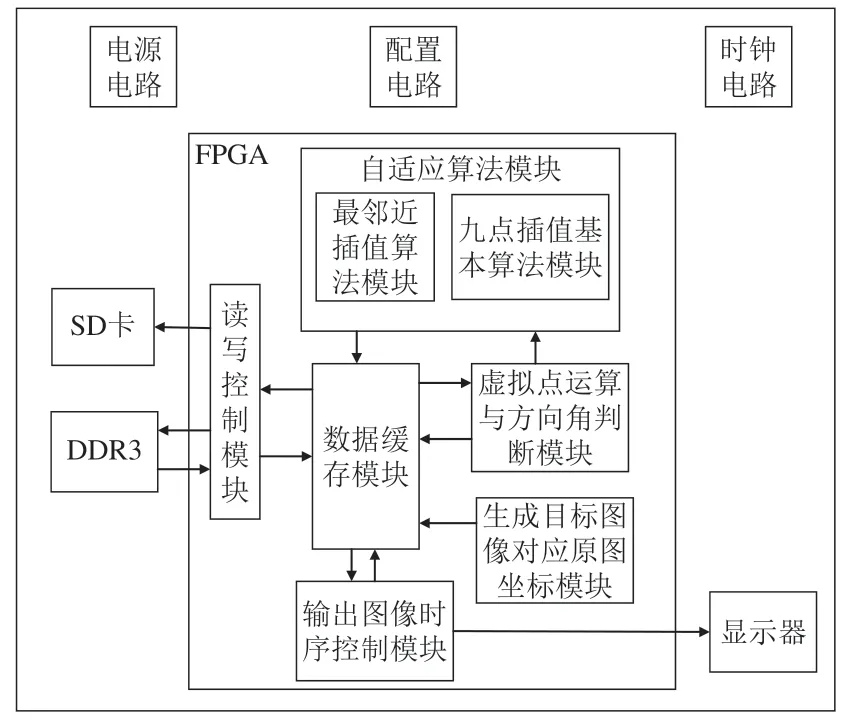

硬件系统由FPGA、SD卡、DDR3存储模块、HDMI输出接口及外围电路模块组成。系统的硬件组成如图7所示。其中主控芯片选用Xilinx公司xc7a35tfgg484-2型号的FPGA芯片。

图7 系统整体框架Fig.7 Overall system framework

4.2 插值算法的硬件设计

本文设计的自适应图像缩放算法可以根据图像边缘与平坦区域采用不同的插值算法。当插值点邻域被判定为平坦区域时,通过九点插值基本算法进行插值运算;当插值点邻域被判定为边缘区域时,通过最近邻域法进行插值运算。在进行九点插值基本算法的设计时,将小数乘法操作改为源像素点的移位操作,大幅减少了硬件资源消耗。在FPGA硬件平台上进行了图像的缩放算法实现,本文设计的九点插值自适应缩放算法流程如图8所示。

图8 算法逻辑框图Fig.8 Algorithm logic diagram

首先生成目标图像对应原图像的坐标并输入到数据缓存模块。数据缓存模块根据对应坐标从DDR3中读取原图像数据,存满两行图像数据后,将数据输入到虚拟点与方向角判断模块,此模块将计算虚拟点坐标以及判断图像边缘角度。将边缘方向4个角度、不是边缘点共5种模式用Mode的5个值来表示。当判断为边缘点时,根据边缘方向将角度分为0°、45°、90°、135°,对应将数据输入到最近邻域插值运算模块,Mode的值分别为0、1、2、3;当判断为非边缘点时,Mode的值为4,对应将数据输入到九点插值运算模块。具体FPGA功能模块设计如图7中FPGA内部功能框图所示。

采用Modelsim对FPGA实现的自适应插值算法进行硬件仿真,结果如图9所示。f11~f33分别为输入到自适应插值算法模块中的4个源像素点与5个虚拟点。Mode为不同角度对应的模式。当Mode为4时,代表此时插值点所处区域为平坦区域,通过九点插值基本算法计算输出像素值;当Mode为0时,此时插值点所处区域为边缘区且边缘方向为0°,输出像素值为此方向的像素值。通过与仿真所用图像对比可以看出,Mode为0时所对应图像位置的确是边缘,初步证明了FPGA实现的正确性。

在实际验证实验中,将拟处理图像存入SD卡中,系统读取图像并进行处理,将处理后的图像存入SD卡并通过HDMI视频接口显示在显示器上。对540×540 Baboon、540×540 Barbara、540×540 Goldhill和540×540 Peppers等图像的长宽分别进行2倍的放大操作,图像放大后尺寸为原图的4倍,放大后的图像大小为1 080×1 080。最终存储到SD卡中,缩放后的图片如图10所示。将SD卡中的图像读出并显示在分辨率为1 920×1 080的显示器上,由于图像为1 080×1 080,因此显示器屏幕两侧有黑条,最终显示器上显示的图像如图11所示。

图10 图像缩放结果图Fig.10 Image scaling result graphs

对最近邻域插值、双线性插值、九点插值基本算法、九点自适应插值算法进行硬件实现,分别统计各算法的资源用量,结果如表2所示。可以看出,九点插值自适应算法的硬件资源使用量比双线性插值减少了约20%。

表2 硬件资源使用表Tab.2 Hardware resource usage table

计算几张图像与原图像的峰值信噪比,结果如表3所示。可以看出在基于FPGA实现的处理算法中,九点插值自适应算法的处理效果最好,其PSNR值相比最近邻域插值与双线性插值算法普遍高出0.3~2.5 dB。

表3 SD卡中缩放后图像的PSNR值Tab.3 PSNR value of scaled images in SD card

5 结论

本文提出一种九点插值自适应缩放算法,对原始图像进行虚拟点的计算,通过计算插值点周围邻点0°、45°、90°、135° 4个方向上的像素变化值,并将变化值与设定的阈值进行比较,进而判断选择合适的插值算法计算得到目标像素值。通过对算法进行软件仿真与硬件实现验证得到该算法的峰值信噪比比最近邻域、双线性插值图像缩放算法提高了0.3~2.5 dB,同时在资源使用量上本文算法比双线性插值算法减少了约20%。本文算法复杂度不高,利于硬件实现。本文提出的九点插值自适应缩放算法在硬件资源极其有限的应用场景具有很高的实用价值。