基于RISC-V 芯片的内置Flash 自编程实现方式

2023-03-22张文文来鹏飞

张文文,来鹏飞

(无锡中微爱芯电子有限公司,江苏无锡 214072)

1 引言

随着科技的进步,各类产品进入智能化时代,常用的智能产品大多内置微控制单元(MCU)芯片。产品出厂前根据实际应用需求在MCU 芯片内部固化了相应的程序,这些程序存储在内置的Flash 闪存中。用户可以根据个人需求自主配置乃至定义一些应用。智能产品为了满足用户的需求,都支持灵活的Flash 编程方法。

MCU 芯片是微型的片上系统(SoC),其内部带有一个或多个核心。常见的MCU 核心有需要授权的ARM 核心,也有开源免费的RISC-V 核心[1-3],RISC-V具有低功耗、低成本、灵活可扩展及安全可靠等特征[4]。自编程技术就是在Flash 主存中定义一段存储空间,放置升级代码,即擦写Flash、读取存储器或者通信程序,升级时运行这段代码,擦写Flash 的应用程序段,实现在线自编程[5-6]。本文基于RISC-V 芯片,提出了一种灵活的Flash 自编程方法。

2 现有Flash 自编程方法分析

Flash 自编程就是在板级系统中通过程序对Flash的存储程序内容进行修改。其中的难点就是执行的程序也在Flash 中,对Flash 进行编程的时候就要暂停执行程序,等编程结束后再执行程序。

Flash 的自编程实现方法有两种:第一种方法将执行自编程的程序放到其他存储器中执行,一般是芯片内置的电易失随机存储器(RAM);第二种方法在自编程的时候将核心时钟停止,等自编程完成后再打开时钟,核心继续读Flash 的取值,执行程序[7]。

第一种方法的优点是应用主程序和自编程的程序相互独立,功能划分清晰;缺点是需要芯片中有额外的存储单元,如果没有或者容量不够那就要增加一块存储的面积,导致芯片面积增加,而且RAM 是掉电易失存储器,需要把自编程程序先放到Flash 中,执行时再搬运到RAM 中,流程复杂。第二种方法涉及时钟的控制,硬件实现比较复杂;同时应用主程序和自编程的程序都在Flash 中执行,两块程序交织在一起,整体程序繁琐。

3 RISC-V 指令集

RISC-V 是一个典型三操作数、加载-存储形式的RISC 架构。RISC-V 的指令集使用模块化的方式进行组织,每个模块使用一个英文字母来表示。其最基本也是唯一强制要求实现的指令集部分是字母I 表示的基本整数指令子集。RISC-V 架构支持32 bit、64 bit 或者128 bit 的架构,RV32 表示32 bit 架构,其中每个通用寄存器的宽度为32 bit。为了进一步减少面积,RISC-V 架构还提供了一种“嵌入式”架构,用字母E表示,E 是I 的一个子集。E 架构将通用寄存器数量由32 减少到16 个。除此之外,RISC-V 还有多个扩展指令集仍在不断地完善中,现今已经确定的有:整数乘法与除法指令(M);原子操作指令(A);单精度浮点指令(F);双精度浮点指令(D);4 倍精度浮点指令(Q);压缩指令(C)[8-9]。

本设计基于32 bit 的RISC-V 架构,基本指令集架构使用的是E,扩展指令集使用的是M、A 和C,记作RV32EMAC,共提供112 条指令,分别为E 的47 条指令,M 的8 条指令,A 的11 条指令和C 的46 条指令。其中有一条等待中断指令wfi,当执行该指令时,如果没有待处理的中断,则核心处于空闲状态[10],也就是说执行wfi 指令后,RISC-V 核心就停止运行,直到有中断唤醒再继续工作。

4 设计与实现

4.1 设计方案

本文设计了一种简单的兼容两种自编程方式的方案,在MCU 芯片中只需要增加少量硬件开支。本设计仅在Flash 的控制器模块增加自编程的控制逻辑,并将自编程的控制与正常Flash 操作的控制进行二选一。

表1 中自编程控制逻辑设计增加了3 个寄存器,基 地 址 为32’h20c12140, 数 据 位 宽 为32 bit。sp_ctrl_reg 为自编程的控制寄存器,其中低4 位为有效控制位,具体说明见表2,设计中编程功能优先级比擦除高,第1 位和第2 位都为0 时,选择读功能;sp_addr_reg 为自编程的地址寄存器,存放的是自编程的操作地址;sp_data_reg 为自编程的数据寄存器,存放的是自编程的操作数据。

表1 自编程寄存器

表2 自编程的控制寄存器说明

自编程的控制状态机共有4 个,如图1 所示。上电复位后自编程处于IDLE(空闲)状态,当配置自编程的控制寄存器中的自编程使能位后,自编程进入HALT(运行)状态;在HALT 状态下,自编程配置Flash 的读写擦操作,然后进入WAIT(等待)状态;当Flash 开始读写擦操作后,自编程进入END(结束)状态;在END状态下,自编程将读回的数据放入自编程的数据寄存器中,回到IDLE 状态,等待下一次的自编程操作。本设计不需要关注Flash 读写擦的结束时间,其由Flash的中断与wfi 指令配合实现。

图1 自编程状态

4.2 自编程工作实现的流程

控制是由MCU 芯片的内核主导的,内核通过取指操作驱动总线到存储器中读取程序,其兼容两种自编程方式,第一种存储器为Flash,第二种为RAM,两种编程方式的工作流程分别如下。

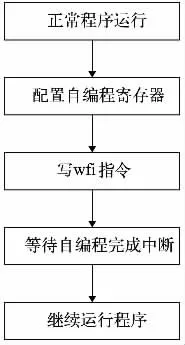

方式1:不带RAM 的自编程工作流程如图2 所示,指令程序放在Flash 里,首先配置好自编程的几个寄存器,启动自编程使能信号,发送wfi 指令,等待自编程完成的中断,然后继续运行程序。

图2 自编程工作流程

方式2:将程序放到RAM 中执行,操作同方式1。与传统方案相比,本设计的优点在于不需要配置定时器,Flash 自编程结束后,中断自动触发程序继续运行,同时内核在自编程过程中也是停止工作的,这样也降低了内核的动态功耗。

通常情况下两种方式选任意一种即可,当芯片中没有RAM 时选择方式1,应用程序复杂时选择方式2。这种兼容设计不仅解决了自编程硬件设计复杂的问题,也解决了应用流程复杂的问题。

4.3 功能验证与结果分析

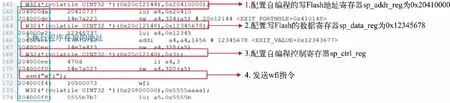

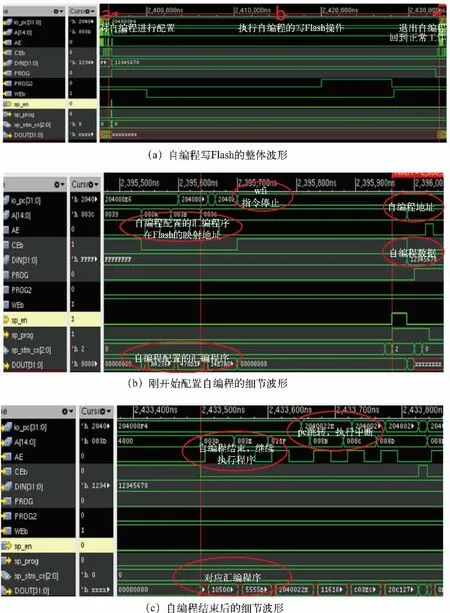

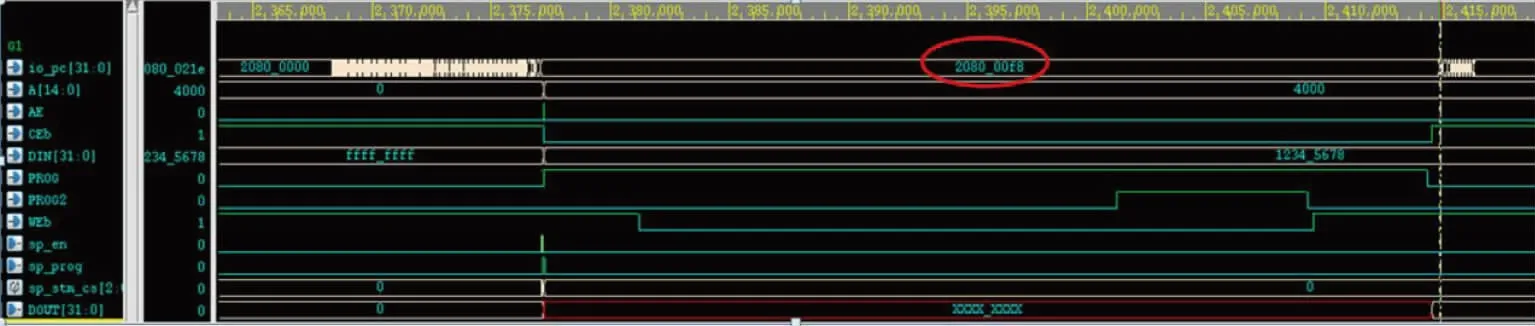

在正常运行的程序中加入自编程对Flash 编程写的操作,按照方式1 中运行的程序编译的汇编代码如图3 所示,方式1 自编程Flash 写操作仿真波形如图4所示,按照方法2 运行的自编程Flash 写操作仿真波形如图5 所示。

图3 自编程Flash 写操作汇编代码

图3 中的汇编程序是按照图2 的自编程工作流程编译的。在配置自编程控制寄存器sp_ctrl_reg 的语句中,值0x3 代表选择编程功能,当选择页擦除时值为0x5,当选择全片擦除时值为0xd,当选择读功能时值为0x1。Flash 对应的内存基地址为0x20400000,RAM对应的内存基地址为0x20800000。图3 蓝框部分为在Flash 中运行时执行程序存放的地址,当选择方式2 时对应的204xxxxx 改为208xxxxx。

图4(a)为整体波形,整个过程分为3 个阶段,分别是对自编程进行配置、执行自编程的写Flash 操作以及退出自编程回到正常工作。波形中信号sp_stm_cs为自编程的状态机状态寄存器;sp_en 为自编程的使能信号;sp_prog 为自编程的写模式选择信号;io_pc 为核心运行的pc 值;A 为Flash 的地址,由于Flash 的数据位宽为32 bit,而对应系统总线的地址按8 bit 进行索引,所以总线访问Flash 的地址为0x10000,A=0x4000;DIN 为Flash 的输入数据;DOUT 为Flash的输出数据;CEb 为Flash 的使能信号,低有效;PROG、PROG2 和WEb 为bit Flash 的写控制信号。从图4(b)可以看出,进入自编程的最后一条指令就是wfi,然后io_pc 值暂停,io_pc=0x204000F4,0xF4 是Flash 的实际地址A=0x3D,当自编程完成之后,核心继续从该地址执行。图5 与图4 的区别是执行wfi 指令之后,io_pc 值暂停为0x208000f8。

图4 方式1 自编程Flash 写操作仿真波形

图5 方式2 自编程Flash 写操作仿真波形

5 结论

在国外对处理器内核技术进行限制的背景下,RISC-V开源的属性使其在国内掀起研究热潮。本文提出了基于RISC-V 芯片的内置Flash 自编程新方法,解决了现有Flash 自编程方法硬件设计复杂、应用流程繁琐的问题,并详细介绍了实现方案,给出了操作流程,分析了验证结果。本文所述的基于RISC-V 兼容Flash 自编程的方法,使用灵活,逻辑设计简单,应用方便,市场前景广阔。