基于Python 的级联半带滤波器RTL 自动生成方法*

2023-03-22何秋秀李晓蓉邵杰卓琳

何秋秀,李晓蓉,邵杰,卓琳

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

1 引言

在现代通信领域中,数字上下变频是软件无线电中收发机的核心部分,而利用级联半带滤波器进行采样率的变换是数字上下变频的关键技术之一[1-3],所以级联半带滤波器的设计开发显得尤为重要。近年来,集成电路(IC)产业的快速发展对电路的性能、面积、功耗及生产周期的要求不断提高,利用自动化技术开发数字电路或者知识产权(IP)模块已经成为主流[4-7]。Python 是一种高级动态编程语言,拥有丰富的标准库,在实现自动化方面有可扩展性、可移植性和可嵌入性等优势[5],因此基于Python 的级联半带滤波器自动生成方法具有重要意义,可以加快设计速度,提高设计质量。

本文基于Python 编程语言,结合级联半带滤波器和并行流水线结构的特点,提出了一种级联半带滤波器寄存器传输级(RTL)自动生成方法。

2 级联半带滤波器介绍

多速率数字信号处理系统通过插值提高信号的采样速率,通过抽取降低信号的采样速率。插值操作是先在已知抽样序列的相邻两采样点之间等间隔地插入M-1 个零值点,然后进行低通滤波,就可以得到M 倍插值的结果;抽取操作是先进行抗混叠滤波,然后每隔M-1 个采样点抽取1 个采样点,就可以得到M倍抽取的结果[8-10]。

半带滤波器是一种实现数字上下变频的高效滤波器,其时域离散方程为[11]:

式中x(n)为半带滤波器的输入信号,n 为单位时间,h(i)为半带滤波器系数,L 为半带滤波器长度,y(n)为半带滤波器的输出信号。

半带滤波器主要有以下特点:1)通带和阻带对称,通带容限和阻带容限相等;2)系数偶对称,且半带滤波器长度为偶数(阶数为奇数);3)所有大于0 的偶数序列的冲击响应值均为0。半带滤波器的特性大大降低了滤波运算所需的乘法次数和加法次数,所以半带滤波器特别适合2 倍的插值或者抽取,而且计算效率高,实时性强。

半带滤波器特殊的频率响应特性使其非常适合2N倍插值或者抽取的多速率转换系统[12-13]。通过采用多个半带滤波器级联的方式,即可十分方便地实现高插值率转换或者高抽取率转换。3 个半带插值滤波器级联可实现8 倍的插值;4 个半带抽取滤波器级联可实现16 倍的抽取。

3 级联半带滤波器RTL 自动生成设计

级联半带滤波器RTL 自动生成设计流程如图1所示,首先读取设计需求参数,创建Python 字典对象,将设计参数存储于此字典对象中;然后读取字典对象中的设计参数,获取级联半带滤波器类型参数;若类型参数为“插值”,则依次生成插值时钟、单级半带插值滤波器、N 级级联半带插值滤波器和插值内建自测单元;若类型参数为“抽取”,则依次生成抽取时钟、单级半带抽取滤波器、N 级级联半带抽取滤波器和抽取内建自测单元。

图1 级联半带滤波器RTL 自动生成设计流程

3.1 级联半带插值滤波器RTL 自动生成设计

3.1.1 单级半带插值滤波器RTL 自动生成

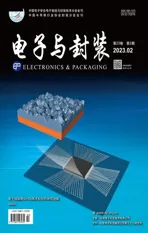

单级半带插值滤波器生成单元由延时生成器、加法生成器、乘法生成器和求和生成器组成。生成的单级半带插值滤波器为2 路输入4 路输出的4 路并行结构,图2 为其设计框图。

图2 单级半带插值滤波器RTL 自动生成设计框图

延时生成器生成延时单元的RTL 代码,通过调用Python 中的readline()函数逐行读取需求参数中的输入数据位宽和延时周期数,再利用write()函数生成延时单元的输入输出信号和always 延时结构,滤波器的两路输入为A0 和A1,则A0 经过延时得到A(n-0),A(n-4), …, A(n-4k),A1 经过延时得到A(n-2),A(n-6),…,A(n-4k+2)。

加法生成器生成加法单元的RTL 代码,读取输入数据位宽和半带滤波器长度参数,再利用write()函数生成加法单元的输入输出信号和always 加法结构,加法结构将系数相同的两个延时项相加,即adder1=A(n-0)+A(n-4k),adder2=A(n-2)+A(n-4k+2),…,共需计算k 次。

乘法生成器生成乘法单元的RTL 代码,读取加法器位宽、半带滤波器长度、半带滤波器系数位宽以及定点系数值,再利用write()函数生成乘法单元的输入输出信号和always 乘法结构,乘法结构将加法单元的结果与对应的半带滤波器系数相乘,即mult1=adder1×coeff1,mult2=adder2×coeff2,…,共需计算k 次。

求和生成器生成求和单元的RTL 代码,读取乘法器位宽、半带滤波器长度和加法流水线级数,再利用write()函数生成求和单元的输入输出信号和always 求和结构,求和结构将所有的乘积项相加求和,即sum=mult1+mult2+…+multk。

3.1.2 级联半带插值滤波器RTL 自动生成

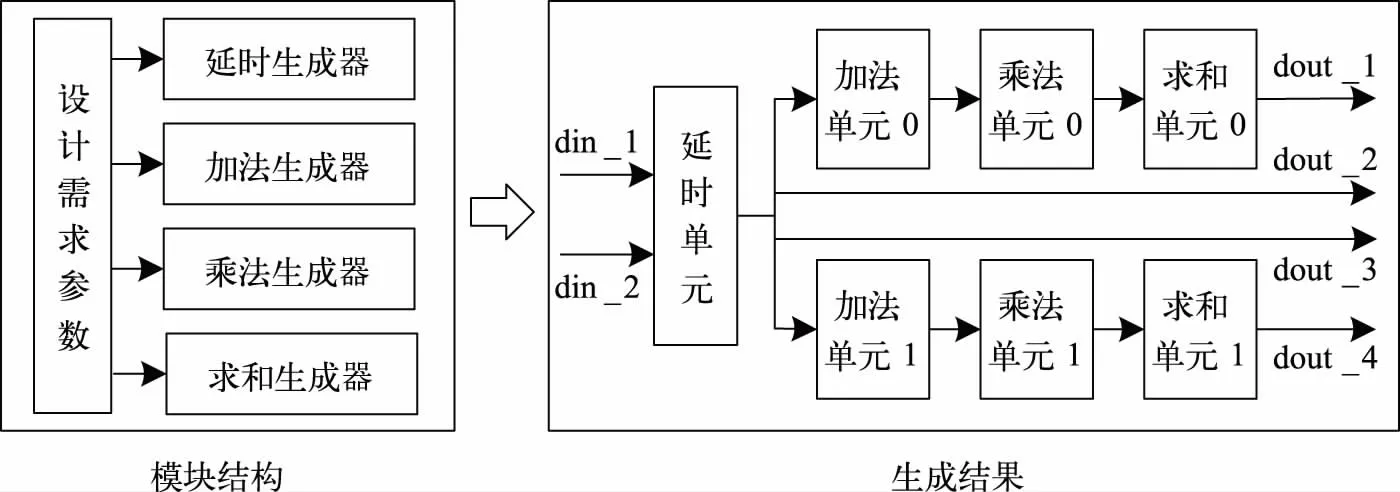

级联半带插值滤波器RTL 自动生成设计包括插值时钟生成单元、N 级级联半带插值滤波器生成单元和插值内建自测生成单元,图3 为其设计框图。

图3 级联半带插值滤波器RTL 自动生成设计框图

插值时钟生成单元生成插值时钟的RTL 代码,调用write()函数生成插值时钟单元的端口信号和always计数分频结构,计数分频结构将源时钟2、4、8…分频。插值时钟单元为各级半带插值滤波器提供时钟信号,各级半带插值滤波器的时钟分频比分别为2N+1,2N,…,4。

N 级级联半带插值滤波器生成单元生成N 级级联半带插值滤波器的RTL 代码,通过调用Python 中的readline () 函数读取需求参数中的最大插值倍数,write()函数生成N 个单级半带插值滤波器并实例化,各个半带插值滤波器首尾依次相连,得到最终N 级级联的半带插值滤波器;N=lb (max_interp),其中max_interp 为最大插值倍数。

插值内建自测生成单元由斜坡测试生成器和脉冲测试生成器组成。斜坡测试生成器生成斜坡测试单元的RTL 代码,调用write()函数生成斜坡测试单元的输入输出信号和always 加一结构,加一结构实现斜坡的产生。脉冲测试生成器生成脉冲测试单元的RTL 代码,调用write()函数生成脉冲单元的输入输出信号和always 计数结构,计数结构实现计数到指定值之后输出高脉冲功能。

3.2 级联半带抽取滤波器RTL 自动生成设计

3.2.1 单级半带抽取滤波器RTL 自动生成

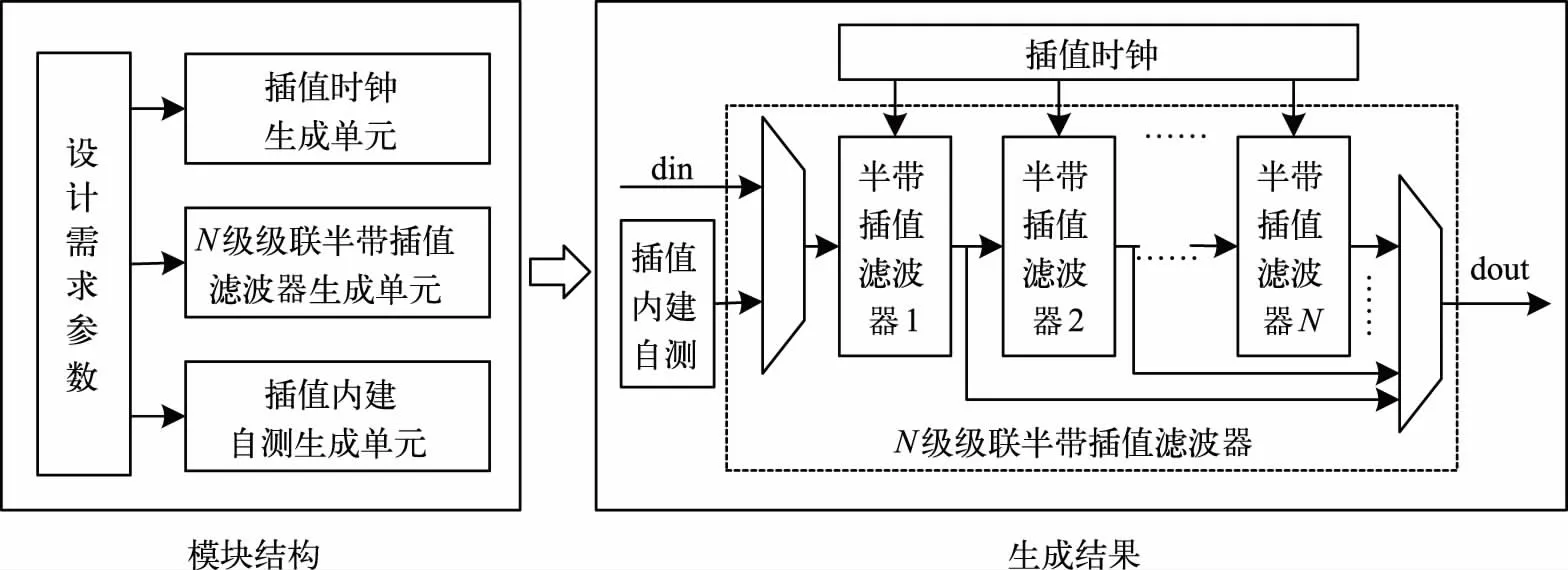

单级半带抽取滤波器生成单元由乘法生成器和求和生成器组成。单级半带抽取滤波器为4 路输入2路输出的4 路并行结构,图4 为其设计框图。

图4 单级半带抽取滤波器RTL 自动生成设计框图

乘法生成器生成乘法单元的RTL 代码,通过调用Python 中readline()函数逐行读取需求参数中的输入输出数据位宽,计算乘法器个数和乘法器输出位宽,再利用write()函数生成乘法单元的端口信号和always乘法结构,乘法结构将输入数据与对应的滤波器系数相乘,即mult1=din1×coeff1,mult2=din2×coeff2,…,共需计算k 次。

求和生成器生成求和单元的RTL 代码,首先读取加法位宽参数,计算相加次数,再利用write()函数生成加法单元的端口信号和奇偶相位的always 加法结构,加法结构将所有的乘积项相加求和,即sum=mult1+mult2+…+multk。

3.2.2 级联半带抽取滤波器RTL 自动生成

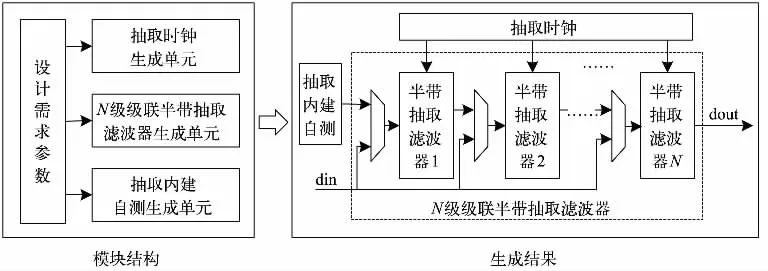

级联半带抽取滤波器RTL 自动生成设计实现包括抽取时钟生成单元、N 级级联半带抽取滤波器生成单元和抽取内建自测生成单元,图5 为其设计框图。

图5 级联半带抽取滤波器RTL 自动生成设计框图

抽取时钟生成单元生成抽取时钟的RTL 代码,调用write()函数生成抽取时钟单元的端口信号和always计数分频结构,计数分频结构将源时钟2、4、8…分频。时钟单元为各级半带抽取滤波器提供时钟信号,各级半带抽取滤波器的时钟分频比分别为4, 8, …,2N+1。

N 级级联半带抽取滤波器生成单元生成N 级级联半带抽取滤波器的RTL 代码,通过调用Python 中readline()函数读取需求参数中的最大抽取倍数,write()函数生成N 个单级半带抽取滤波器并实例化,各个半带抽取滤波器首尾依次相连,得到最终N 级级联的半带抽取滤波器,N=lb(max_decim),其中max_decim 为最大抽取倍数。

抽取内建自测生成单元由斜坡测试生成器和脉冲测试生成器组成。斜坡测试生成器生成斜坡测试单元的RTL 代码,调用write()函数生成斜坡测试单元的输入输出信号和always 加一结构,加一结构实现斜坡的产生。脉冲测试生成器生成脉冲测试单元的RTL 代码,调用write()函数生成脉冲单元的输入输出信号和always 计数结构,计数结构实现计数到指定值之后输出高脉冲功能。

4 试验结果与讨论

本文自动生成了一个级联半带插值滤波器和一个级联半带抽取滤波器,并利用Cadence 公司的NC-Verilog 仿真器在Verilog 环境下进行逻辑功能仿真。利用内建自测单元生成的斜坡信号或者脉冲信号以及利用Matlab 中的sine 函数生成的正弦信号作为测试激励,用Simvision 工具查看仿真波形,最后使用Synopsys 公司的逻辑综合(DC)工具进行电路综合。以下分别介绍自动生成的级联半带插值滤波器和级联半带抽取滤波器的仿真验证和电路综合情况。

4.1 仿真验证

4.1.1 自动生成级联半带插值滤波器

级联半带插值滤波器的设计需求参数如表1 所示,它包括4 级单级的半带插值滤波器,每级都能够实现2 倍插值,总体的级联半带插值滤波器能够实现16、8、4、2 倍插值。当4 级全部使能时,实现16 倍插值;当使能前3 级时,实现8 倍插值;当使能前2级时,实现4 倍插值;当只使能第1 级时,实现2 倍插值。

表1 级联半带插值滤波器的设计需求参数

配置级联半带插值滤波器的插值因子为16,仿真时序如图6 所示,din_1 和din_2 是2 路并行的16 位输入数据,dout_1、dout_2、dout_3 和dout_4 是4 路并行的16 位输出数据,data_combine 是4 路并行输出数据合并的1 路串行输出数据。输入数据经过级联半带插值滤波器后,输出数据的速率变为输入数据的16倍,证明了生成的级联半带插值滤波器功能的正确性。

图6 级联半带插值滤波器仿真时序

4.1.2 自动生成级联半带抽取滤波器

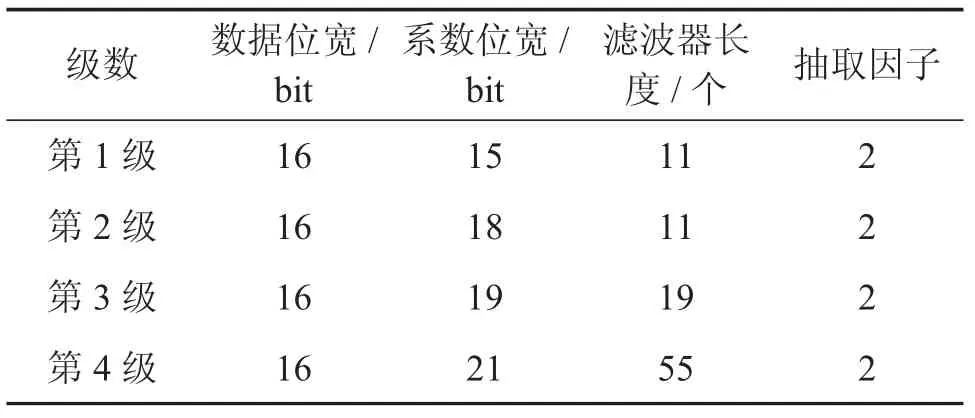

级联半带抽取滤波器的设计需求参数如表2 所示,它包括4 级单级的半带抽取滤波器,每级都能够实现2 倍抽取,总体的级联半带抽取滤波器能够实现16、8、4、2 倍抽取。当4 级全部使能时,实现16 倍抽取;当使能后3 级时,实现8 倍抽取;当使能后2 级时,实现4 倍抽取;当只使能第4 级时,实现2 倍抽取。

表2 级联半带抽取滤波器的设计需求参数

配置级联半带抽取滤波器的抽取因子为16,仿真时序如图7 所示,din_1、din_2、din_3 和din_4 是4 路并行的16 位输入数据,dout_1 和dout_2 是2 路并行的16 位输出数据,data_combine 是2 路并行输出数据合并的1 路串行输出数据。输入数据经过级联半带抽取滤波器后,输出数据的速率变为输入数据的1/16,证明了生成的级联半带抽取滤波器功能的正确性。

图7 级联半带抽取滤波器仿真时序

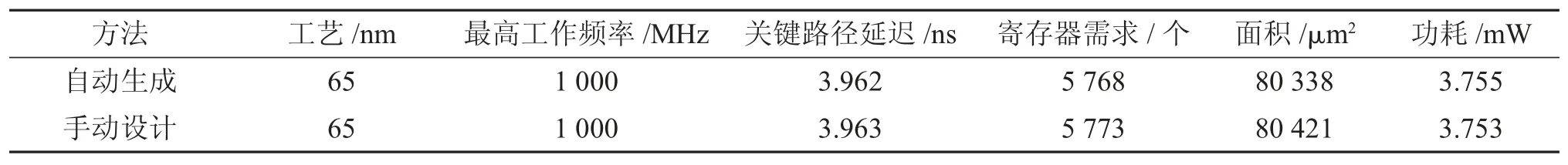

4.2 电路综合

为了进一步证明该方法的有效性,将自动生成的RTL 代码和手动设计的RTL 代码进行对比分析。基于TSMC 65 nm 工艺,使用Synopsys 公司的DC 工具进行电路综合,对比分析在相同的条件下,两者的寄存器需求、关键路径延迟、面积及功耗等指标。级联半带插值滤波器电路和级联半带抽取滤波器电路综合对比结果分别如表3 和表4 所示。

表3 级联半带插值滤波器电路综合对比结果

表4 级联半带抽取滤波器电路综合对比结果

电路综合对比结果表明,在TSMC 65 nm 工艺下,最高工作频率为1 000 MHz 时,自动生成的级联半带插值滤波器的关键路径延迟为3.962 ns,面积为80 338 μm2;手动设计的级联半带插值滤波器的关键路径延迟为3.963 ns,面积为80 421 μm2。自动生成的级联半带抽取滤波器的关键路径延迟为3.964 ns,面积为65 938 μm2;手动设计的级联半带抽取滤波器的关键路径延迟为3.964 ns,面积为65 963 μm2。自动生成的级联半带滤波器RTL 的时序和资源消耗与手动设计的RTL 代码基本一致,证明了本文基于Python的级联半带滤波器RTL 自动生成方法的有效性。

5 结论

本文基于Python 编程语言,结合级联半带滤波器和并行流水线结构的特点,提出了一种级联半带滤波器RTL 自动生成方法。试验结果证明了本文提出的方法能够自动生成任意N 级级联的半带插值滤波器或者半带抽取滤波器,生成的滤波器不仅能够实现2N倍的插值或者抽取,而且还含有内建自测单元,能对级联半带滤波器进行斜坡和脉冲测试,实现了可测试性设计,提升了设计效率,缩短了开发周期。

现有的级联半带插值滤波器或级联半带抽取滤波器都是固定的结构,而针对不同应用需求,基于性能参数智能评估,自动生成不同结构的级联半带滤波器将是今后优化的重点。