中断与跳转操作对指令串的影响

2015-03-25许江宁

许江宁

常州工程职业技术学院,江苏常州 213164

中断与跳转操作对指令串的影响

许江宁

常州工程职业技术学院,江苏常州 213164

本文介绍了中断、跳转操作对运行中的指令串的影响,首先介绍了CPU指令并行的概念,再说明中断,跳转操作对并行运行的指令的影响,介绍了解决这种影响造成的错误的方法,主要是说明中断,跳转指令的特殊性。

中断;跳转;并行运行;取消指令

1 CPU指令并行的概念

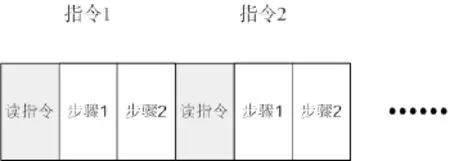

观察CPU执行一条指令,总是可以分成如下两个阶段,首先CPU要从内存中取出需要的指令,即读指阶段,其次根据指令来执行,即执行阶段,而执行阶段,可以看成两类较小的微指令的组合,第一类是数据在CPU内各个寄存器间的传输,第二类是ALU运算或I/O的输入输出,而执行中的步骤也一般就是上面两步(次序可变),或只有第一步。总体来说,CPU执行一个指令最多可以再细分为第一阶段加第二阶段的两个步骤共三步。因此系统执行指令时,可以看成是一条三部分组成的流水线。下图,是指令串的串行执行。

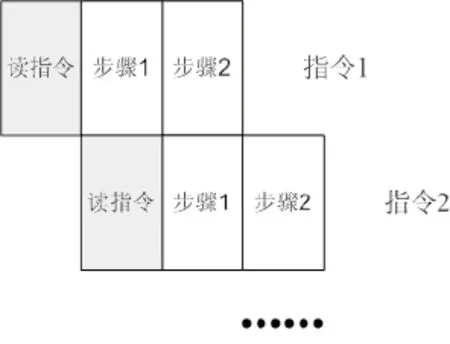

上面设计的CPU,一次只执行一条指令,一条指令执行三个步骤最少有三个周期。但上面说的三步中,仔细分析,大都是可以并行运行的。例如两类微指令,第一类只是CPU内部总线上的操作,第二类是I/O或ALU部件的操作,两类操作在空间上是独立的,可以同时执行,即并行执行。又如每条指令都要先从内存中读取,这是I/O部件的操作,除了与读写类指令的读写操作有矛盾,也可以与其他操作并行执行。总体来说,三部分间还是有较大的并行空间,下图是理想状况下指令串并行执行的方式图。

2 中断、跳转操作对并行运行指令的影响

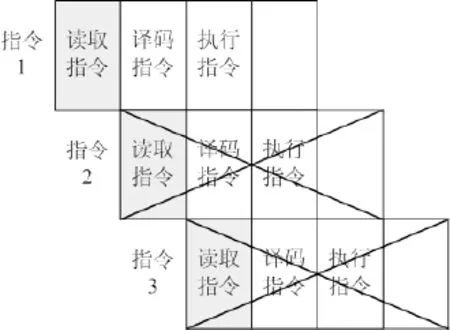

并行执行指令的结果是同时会处理数条指令,从执行的结果看,他们是顺序执行的。如果出现跳转,中断类的指令,会造成指令串的改变,本来依次执行,这种改变没有问题,但如果并行执行,一条指令先需要取指,再译码指令,只有到了译码阶段,CPU才能知道读到了一条跳转类的指令,那之后要执行的指令全部要修改,但此时,一定已经预先读取了某些指令,这些指令属于原先的指令串,必须要舍去,可以使用EMP空白指令来取代已经读取的指令,这个指令没有任何功能。

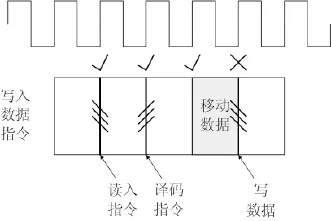

下图是取消指令的示意图,可见需要消去指令1后译码阶段和执行阶段两个时期读取的指令。

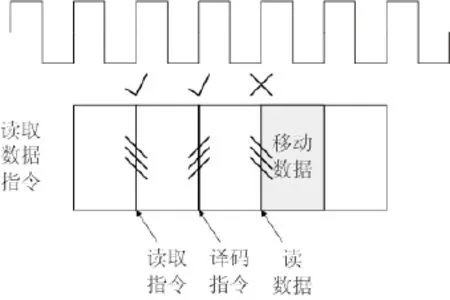

上面只介绍了改变执行指令地址这一过程的影响,但是,中断操作(包括软硬中断两种)的要求是处理完中断,最后还能返回原来正在执行的程序中,这样CS,IP两寄存器中的内容就要保存起来。下面讨论软件中断指令INT,与硬件中断类似,但更简单些。对于软件中断,被保存的CS,IP的值应该指向INT指令之后的一条指令,但是类似于上段的内容,只有在执行INT两个周期前的CS,IP才指向INT后的这条指令,而此时已经无法确定CS,IP的指向。有一个理解是过了两个周期,那CS,IP就应该指向INT后的第三条指令,此时只要把CS,IP减二保存起来就可以了。但是有一个重要的问题是,CPU在运行时,并不是每个周期都是读取指令的,I/O有时还可能被读写内存类的指令所占用,占用时,CS,IP是不变的。以下考察读写对I/O的占用情况,并分析这一影响的过程,因为微指令清零后,默认的操作就是读取指令,那么需要把不是默认情况的未读取指令的周期标示出来。

分析“读”,“写”指令对读取指令操作的影响时,对号表示此时刻可以读入指令,叉号表示I/O被占用,无法读入指令。下图是“读”指令的示意图。

可见读指令后最多只能连续执行两个指令,下图是“写”指令的示意图。

写指令后可以连续执行三个指令。按照上面分析,可能会出“读,读,软中断”的情况,并且这三者也是连续被读取,连续执行的,此时,软中断后两个周期内,I/O都是被占用的,那CS,IP根本没有变化。所以读取INT指令两个周期后,CS,IP可能会出现增加4,增加2,不变三种情况。所以此时要通过读取指令情况,对CS,IP保存的数值进行处理后再保存。

3 对指令串改变的解决方法

上面两节中已经对解决方法有所涉及,就是将后两个周期读取的指令取消掉,具体做法是用EMP指令覆盖这些指令。观察指令集表,可见EMP指令机器码的高四位是1111,当需要覆盖指令时,用1111与目标指令代码相或,目标代码就转化为EMP指令,如果不用覆盖,就用0000与目标代码相或,目标代码不变。

对于输出正确的地址,主要是一些条件判断,需要对各种出现矛盾的情况做出处理。

[1]单睿,洪缨,侯朝焕.推断与推测技术在现代高性能微处理器设计中的应用研究[J].计算机学报,2003(11).

[2]姬忠宁,陈迅,徐金甫,等.基于指令前缀的专用VLIW压缩技术研究与实现[J].电子技术应用,2013(4).

TN2

A

1674-6708(2015)149-0110-02