一种基于匹配网络结构的高效率X波段高功率放大器设计

2023-03-11汪曾达李圣麒苏国东

汪曾达,刘 军,李圣麒,苏国东

(杭州电子科技大学 集成电路科学与工程学院,杭州310018)

X波段电磁波(8~12 GHz)抗干扰性强、空间损耗低,广泛应用于军事及空地通信领域。使用在甚小天线地球站(very small aperture terminal, VSAT)及卫星通信的X波段功率放大器是射频前端芯片发射通道的主要器件之一,通过放大射频信号的功率,为信号的空间传播提供足够大的功率。高输出功率、高效率的功率放大器可拓展无线通信距离并延长设备工作时间。

当前,功率放大器的研制多聚焦于提高输出功率的同时提高功率附加效率[1-6]。2017年, Kamioka等[7]采用内部源通孔型0.15 μm氮化镓工艺,压缩芯片面积换取了更好的散热,功率放大器的工作频率为8.5~10.5 GHz,输出功率为46.1~47.4 dBm(41~56W),功率附加效率为49%~55%,增益为10.1~11 dB,实现了X波段高效率、高功率放大器,但受制于单级电路结构,增益较低。同年,Hong等[8]采用0.25 μm氮化镓工艺,在脉冲波测试条件下,功率放大器的输出功率为47.5~48.7 dBm,功率附加效率为40%~45%,增益为20 dB;连续波测试条件下的面积功率密度为5.57 W·mm-2,外围功率密度为6.43 W·mm-1,热阻为1.7 ℃·W-1,实现了X波段紧凑的较高效率高功率放大器。2019年,Tommaso等[9]采用0.15 μm氮化镓工艺,在工作频率为10 GHz时,功率放大器的饱和功率增益为20 dB,输出功率大于40 dBm(10 W),利用电源调制技术优化第二级放大级在不同输入功率下的漏极偏压,改善了放大器的线性度,实现了X波段电源调制高功率放大器。综合当前的研究工作,研究人员通过增加放大电路的级数提高功率放大器的增益,增加放大级并联的晶体管的外围或数量提高功率放大器的输出功率,利用新介质实现较低的传导损耗。

本文基于0.25 μm氮化镓工艺,设计了30 W X波段单片微波集成电路(monolithic microwave integrated circuit, MMIC)高功率放大器,在工作频率为8~12 GHz时,饱和输出功率大于44.1 dBm(30 W),功率平坦度为±0.3 dBm,功率附加效率为38%~42%,面积功率密度为1.78 W·mm-2,有源外围功率密度为4 W·mm-1。功率放大器采用的低损耗输出匹配网络结构,实现了高输出功率的同时效率也较高,可广泛应用于X波段卫星通信等无线通信领域。

1 X波段功率放大器电路设计

1.1 X波段功率放大器电路设计

图1为两级级联拓扑结构的MMIC功率放大器设计流程图。首先,射频系统工程师根据市场或者系统需求分析确定目标功率放大器电路的具体性能指标。其次,由电路设计工程师初步确定功率放大器电路的基本拓扑结构包括级联、分布式、推挽式、堆叠式、平衡式、Doherty及Chireix等;根据性能指标及采用的工艺特点,确定晶体管的静态工作点,至此,可确定功率放大器电路可实现的输出功率以及晶体管外围;进行放大级(第二级)电路的输出匹配网络设计及驱动级(第一级)电路的输入匹配网络设计;完成级间匹配网络并进行整体性能迭代优化,至此完成了原理图设计。然后进行版图设计与EM仿真,通过设计规则检查(design rule check,DRC)和版图与原理图比较(layout versus schematics, LVS)验证后方可进行流片与载片测试。最后,检验电路是否满足指标要求。

图1 两级级联拓扑结构的MMIC功率放大器设计流程图

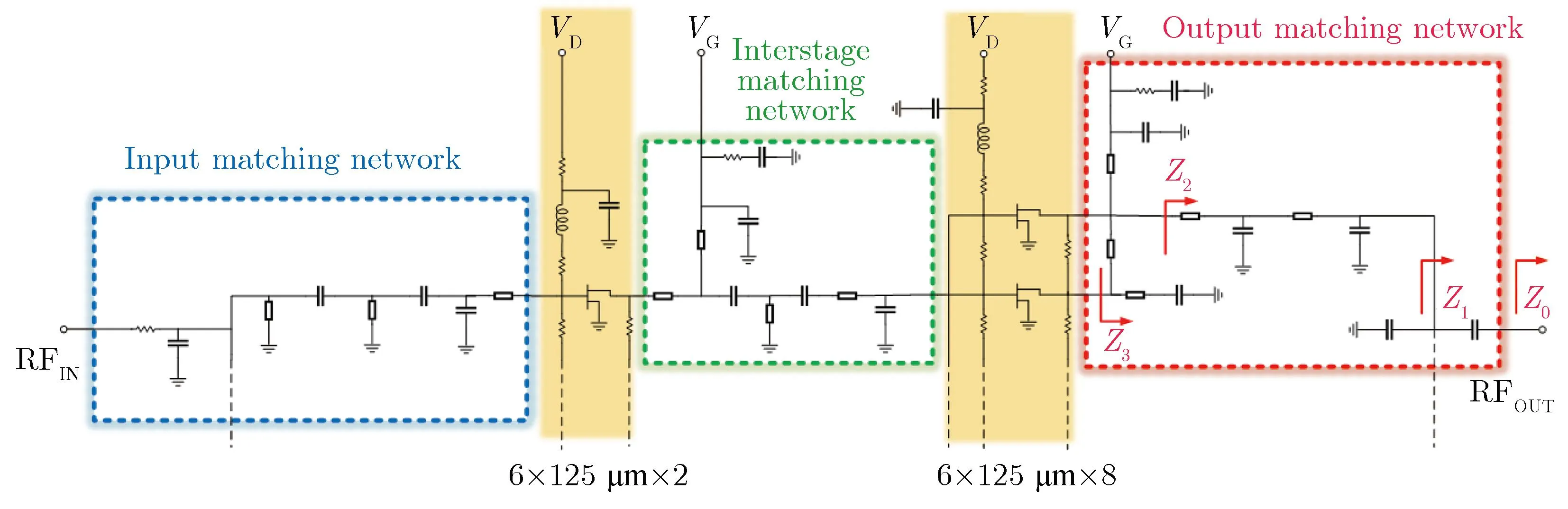

图2为30 W X波段高功率放大器电路原理图。由图2可见,电路采用两级级联拓扑结构,其中驱动级电路由2个栅指数为6,栅宽为125 μm的晶体管并联,放大级电路由8个栅指数为6,栅宽为125 μm的晶体管并联。为平衡输出功率、效率及增益,晶体管的偏置均设置为AB类放大器的偏置条件,其中栅极偏置设为-2 V,漏极偏置设为28 V。

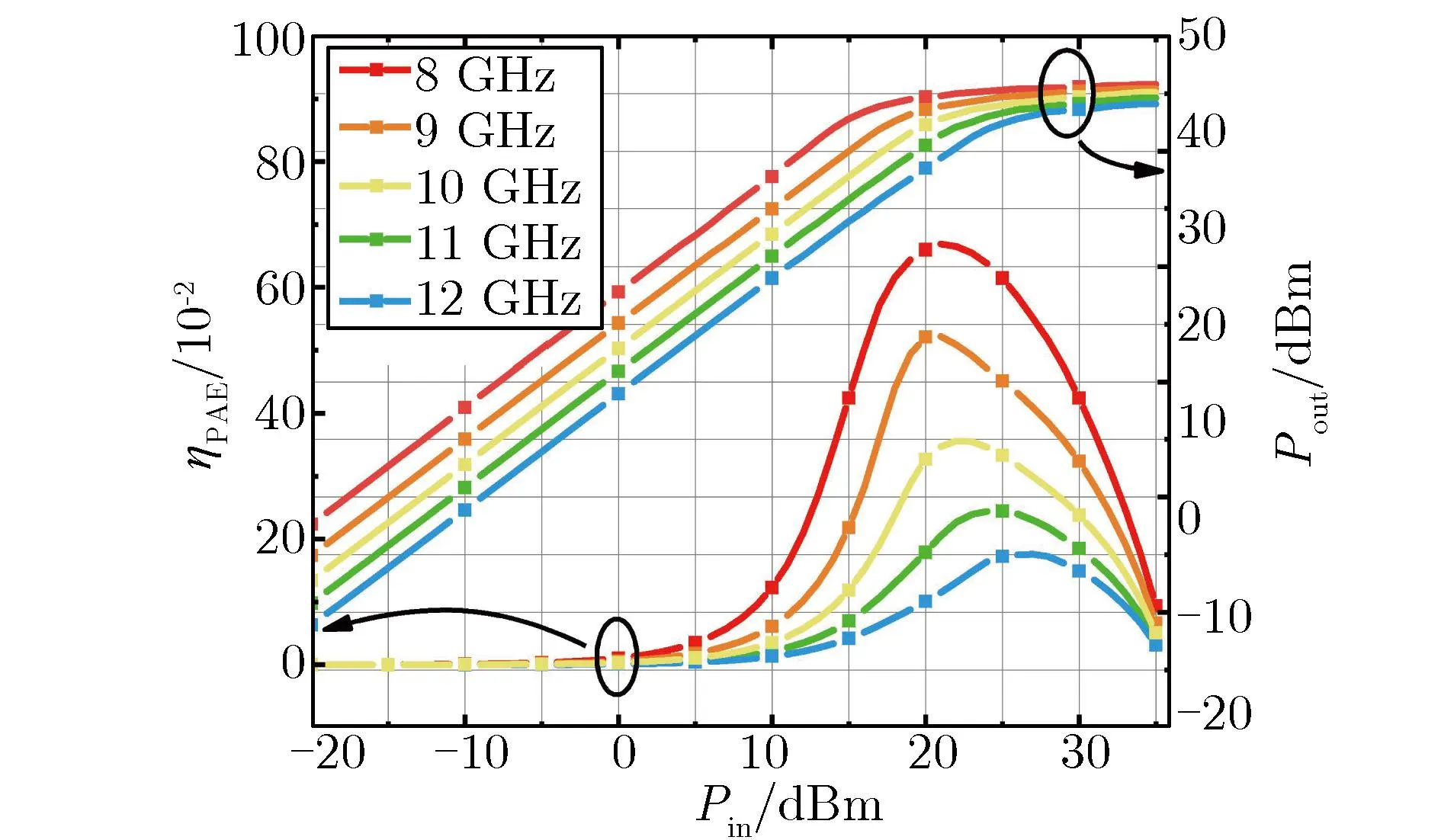

放大级和驱动级电路的功率扫描结果如图3所示。由图3可见:在固定源/负载阻抗下,放大级电路可实现饱和输出功率大于45 dBm,对应的功率附加效率ηPAE大于60%,满足设计要求;驱动级电路可实现饱和输出功率大于35 dBm,满足放大级电路所需的饱和输入功率的要求。在确定放大级及驱动级的晶体管外围后,设计放大器的稳定性结构及宽带低损耗输出、级间、输入匹配网络。

1.2 稳定性分析

有源器件引入的输入负阻,是造成放大器低频不稳定的主要原因。在低频时,假设射频匹配网络中的耦合电容开路,则放大器的输入实阻抗Zin(ω)可表示为[10]

(1)

其中:Zload为晶体管漏极负载阻抗;gm为跨导;Cfeed为射频信号输入端和晶体管之间存在反馈电容。

为避免放大器在低频处出现振荡,应尽可能避免负阻的出现,需足够大的Zload及合适的栅极偏置电阻。因此,本文设计的30 W X波段功率放大器的栅极偏置均采用电阻加电感结构,避免晶体管的输出阻抗出现负阻,同时避免放大器发生参量式振荡[11-13];而漏极偏置为降低损耗,采用微带线加旁路电容结构,降低输入阻抗负阻,再结合级间匹配网络,实现了全频段的绝对稳定。

1.3 功率附加效率分析

单个栅指数为6,栅宽为125 μm的晶体管的负载牵引结果如图4所示。其中:彩色等高线图表示不同大小的功率附加效率ηPAE;黑色等高线图表示不同大小的输出功率,由中心向外依次为36.5,36.75,37,37.25 dBm;红色圆点与图1中的阻抗值一一对应。

图2 30 W X波段功率放大器原理图

(a)The power sweep performance of the amplifier stage

(b)The power sweep performance of the driver stage

图4 单个栅指数为6,栅宽为125 μm的晶体管的负载牵引结果

氮化镓工艺晶体管存在较大的漏-源、栅-源寄生电容,在造成晶体管的增益滚降的同时,增加匹配网络的有载品质因素[2]。为实现宽带的阻抗匹配,需要采用多枝节匹配结构,不同枝节数量下的最小节点品质因素Qmin(n)可表示为

(2)

其中:n为枝节数量;Kn可表示为

(3)

其中,Ropt可表示为

(4)

其中:R0为负载端口实阻抗;Ropt为晶体管的最佳负载阻抗;VDS为晶体管的漏极偏置电压;Imax为晶体管的饱和漏极电流。

以R0=50 Ω,Ropt=10 Ω为例,Qmin(n=1)=2,Qmin(n=2)=1.11,Qmin(n=3)=0.70,由此可见,枝节数量的增加显著降低了节点品质因素,有助于实现宽带的阻抗匹配。在输出匹配网络设计中,通过耦合电容及去耦电容将端口阻抗变换至Z1点,后续通过低特征阻抗微带线以及旁路电容组成的枝节网络将阻抗变换至Z2点,最后通过漏极偏置网络将基波负载阻抗变换至最佳ηPAE和Pout点。此外,功率放大器的级间、输入匹配网络也采用了多枝节匹配结构,在拓展网络带宽的同时降低带内匹配插损。

2 版图及仿真结果

图5为X波段功率放大器芯片版图。版图由驱动级、放大级及输出、级间、输入匹配结构构成。版图设计中除栅极偏置外,不再使用集总电感器件,并且为降低每根电源线承载的电流强度,避免过大电流烧毁器件,每级电路均采用双栅极电路偏置和双漏极电源偏置。为降低高频信号耦合效应带来的性能恶化,每个独立器件之间的间距大于50 μm。特别地,偏置网络上的高Q值旁路电容,一方面为射频信号提供理想接地点,避免后续外部金丝电感对电路阻抗的影响,且规避不良好接地的偏置网络引起的内部振荡问题;另一方面,可有效避免外部脉冲信号对晶体管造成损害。驱动级电路的晶体管外围为1.5 mm,由2个栅指数为6,栅宽为125 μm的晶体管组成,而放大级电路的晶体管外围为6.0 mm,由8个栅指数为6,栅宽为125 μm的晶体管组成。射频输入、输出端口为标准GSG端口,射频焊盘中心间距为150 μm,直流焊盘的尺寸为100 μm×100 μm,芯片总面积为16.9 mm2。

图5 30 W X波段功率放大器芯片版图(长:4 760 μm×宽:3 560 μm)

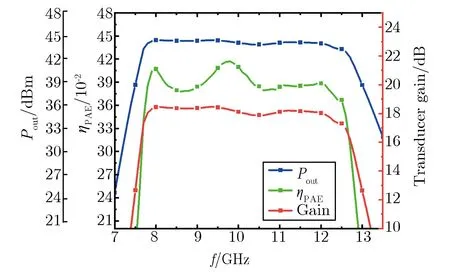

30 W X波段功率放大器后仿真结果如图6所示。由图6(a)可见,后仿真小信号结果中,带内输入驻波系数ρVSWR,I均小于2.5 ,带内输出驻波系数ρVSWR,O均小于2.2,正向小信号增益S21为22.9~25.3 dB,小信号增益平坦度为 ±1.2 dB;由图6(b)可见,后仿真大信号结果中,在26 dBm的连续波(continuous wave,CW)信号输入下,功率放大器的饱和输出功率Pout大于44.1 dBm,面积功率密度为1.78 W·mm-2,有源外围功率密度为4 W·mm-1,功率平坦度为 ±0.3 dBm,此时的功率附加效率ηPAE大于38 %,最大值达到42 %,转换增益为17.9~18.5 dB。此外,在饱和输出功率为44.1 dBm的基础上,进一步提高输入功率、晶体管的工作点及漏极偏置电压,放大器的最大输出功率可提高至46 dBm,即放大器的功率容量可达40 W。

(a)The ρVSWR,I,ρVSWR,O and S21 of the 30 W X-band power amplifier

(b)The Pout, ηPAE and gain of 30 W X-band power amplifier

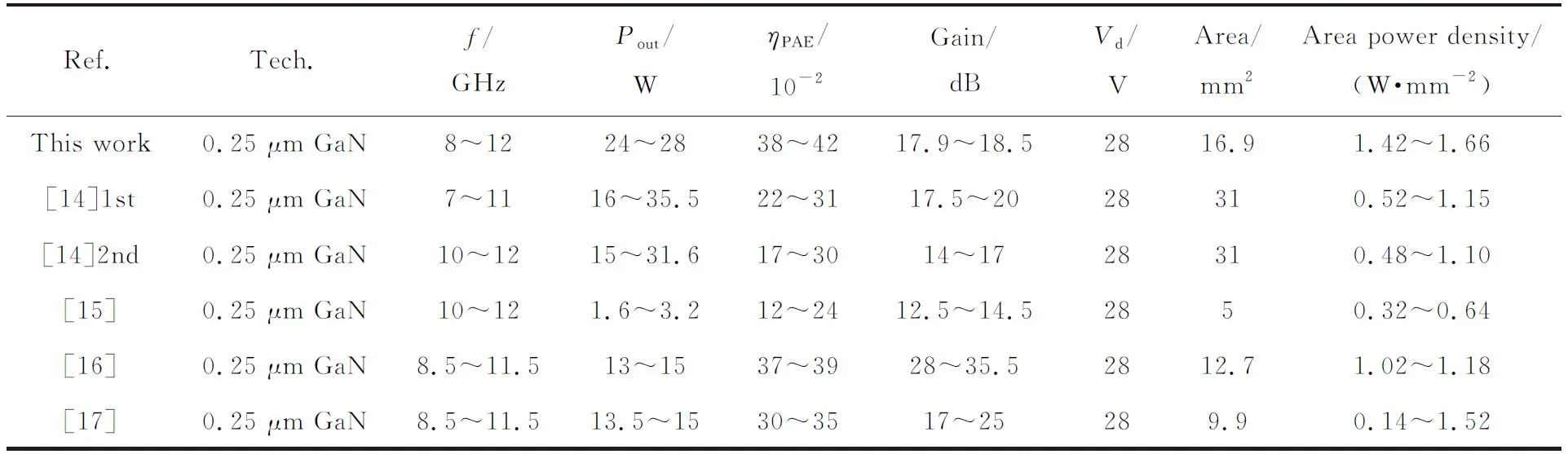

近几年国内外GaN 工艺功率放大器的仿真性能参数对比如表1所列。由表1可知,在CW输入条件下,本文设计的功率放大器带宽及饱和输出功率优于文献[15-17],ηPAE优于文献[14-17],功率增益优于文献[14-15,17],面积功率密度优于文献[14-17]。

结合本文后仿真结果及文献[14]中同样采用某商业0.25 μm GaN工艺的2款X波段功率放大器的仿真结果与测试结果可知:采用该工艺设计的X波段放大器的小信号(S参数)仿真结果与测试结果具有较高的一致性,工作频段内的输入/输出回波损耗均能满足最初的设计指标,小信号增益的测试结果一般比仿真结果小0~2 dB,且频率越高偏差越大;放大器的大信号仿真结果与测试结果的相对偏差一般小于5%~10%,其结果趋势具有较高的一致性。针对由加工工艺偏差导致的设计偏差,在该款功率放大器的版图设计中已完成包括DRC及LVS验证,确保电路版图满足工艺标准。

基于合理的电路设计流程、完备的自动化检查程序及成熟的商业0.25 μm氮化镓工艺,预期该款放大器的实测结果与仿真结果的相对偏差小于5%~10%,测试结果能够满足设计指标的要求。

3 结论

本文基于0.25 μm 氮化镓工艺设计了一款X波段高功率放大器,采用两级级联拓扑结构,利用栅极/漏极偏置网络实现了放大器全频段的绝对稳定,且同时实现了高输出功率和高效率;利用宽带低损耗的输出、级间、输入匹配网络,实现了饱和输出功率大于44.1 dBm的同时,带内功率附加效率大于38%,饱和输出功率平坦度为 ±0.3 dBm,转换功率增益大于17.9 dB。本文可为氮化镓基宽带高效率、高功率放大器的设计提供参考,特别是可为用于增强电路稳定性的偏置网络及宽带低损耗匹配网络的设计方法提供参考。

表1 近几年国内外GaN工艺功率放大器的仿真性能参数对比