基于混合介质的同轴-环形TSV 传输特性分析

2023-03-07杨贺张立文杨陈王金婵曹磊

杨贺,张立文,杨陈,王金婵,曹磊

(河南科技大学 电气工程学院,河南 洛阳 471023)

随着系统复杂度和集成密度的增加,迫切需要提高集成系统中不同芯片互连的传输性能,而硅通孔(Through Silicon Via,TSV)是实现三维集成的关键技术之一。在三维集成电路系统中,从TSV 到相邻TSV、互连线或有源区域的耦合噪声不可忽略,TSV互连的耦合噪声和信号损耗是设计的关键问题,需要仔细建模和表征[1-3]。目前,圆柱形TSV、环形TSV、锥形TSV、同轴TSV 等不同的TSV 结构得到广泛应用。由于环形TSV 能减小金属导体与硅衬底之间热失配,提高三维集成电路热应力可靠性[4-5]。同轴形TSV 结构可以有效地降低损耗和耦合噪声,同时减小所引入的热应力和KOZ(Keep-Out-Zone),提高热机械性能[6-8]。而同轴-环形TSV(Coaxial -Annular Through Silicon Via,CA-TSV)结构同时具备两者优势,在超高密度集成电路中有很大应用前景。

TSV 结构在穿过衬底介质以及其他介质网络时,信号会有不同程度的衰减,填充介质种类也会对传输损耗(S11、S21)与耦合串扰产生影响,影响信号的完整性[9-17]。Chen 等[10-11]研究发现BCB 及Air 介质层圆柱TSV 相比传统SiO2介质层,相邻TSV 泄漏电流、电容密度均大幅减小;Salah 等[12]对比了圆柱形TSV、同轴TSV 以及空气隙同轴TSV 结构三者的性能,发现空气隙同轴TSV 降低寄生电容和功耗的作用更明显;Qian 等[13]研究发现内Si 外BCB 介质CA-TSV 的S21比同轴型TSV 结构更大,且抗噪声能力相当。随着研究的深入,Curran 等[14-15]研究发现“Si-BCB-Si” 混合介质层同轴TSV 的S12参数随着中间BCB 介质尺寸减小而增大,并对RLCG(Resistance -Inductance -Capacitance-Conductance)参数进行了准确提取;丁英涛等[16]提出了一种“Si-BCB-Si” 混合介质类同轴TSV 结构,并对其传输损耗进行优化分析;杨银堂等[17]提出了一种“BCB-Air” 混合介质同轴TSV 结构,相比传统同轴型TSV 阵列,其耦合串扰减小,但损耗增大。目前对于混合介质TSV 的研究主要集中在同轴TSV 结构。而CA-TSV 作为一种新的TSV 结构,目前对其研究主要围绕在热机械特性和电学特性[6,18-20],对混合介质CA-TSV 的传输特性研究鲜有报道。

为了进一步提高CA-TSV 传输性能,本文针对外层为混合介质的CA-TSV 传输特性展开研究,首先对CA-TSV 内外层介质材料对传输损耗及串扰的影响进行分析,以此为基础,提出了一种新型“BCB-Si-BCB”混合介质CA-TSV 结构,并对混合介质尺寸及配比对CA-TSV 单管传输损耗与串扰的影响进行了研究,得到一种低串扰且传输损耗较低的混合介质配比,将模型尺寸放大发现结果不变。最后,对混合介质CA-TSV 模型的RLCG 参数进行提取,并建立等效电路模型,代入ADS 中得到S11、S21参数,并与HFSS 仿真结果进行对比,拟合效果良好证明了理论模型正确性。

1 CA-TSV 内外介质种类对S 参数影响

1.1 CA-TSV 模型参数

CA-TSV 模型如图1 所示。其中图1(a)是内外单一种类介质CA-TSV 截面图,模型尺寸见表1,硅衬底电导率为10 S/m。

表1 CA-TSV 尺寸参数Tab.1 CA-TSV size parameters

图1 两种CA-TSV 模型横截面图。(a) 内外单一介质CA-TSV;(b) 外层为混合介质CA-TSVFig.1 The cross-sections of two CA-TSV models.(a) CA-TSV with internal and outer single dielectric layer;(b) CA-TSV with outer mixed dielectric layer

1.2 CA-TSV 内外层介质种类对S 参数影响

1.2.1 内部介质种类对S参数影响

固定外层介质为Si,将内部介质种类分别设为BCB、SiO2、Si(相对介电常数分别为2.6,4.0,11.9),在HFSS 中进行仿真,仿真频段设为0.1~100 GHz、步长设为0.1 GHz,仿真精度设为0.02 dB,仿真结果如图2。显然,内层介质种类对CA-TSV 的插入损耗与回波损耗无影响;内层介质种类对串扰影响也相对较小,且相对介电常数越低、绝缘性越好的材料串扰越小,这是由于内部介质与铜环导体直接接触,漏电流通过介质层流入RDL 层,且介质相对介电常数越小其抑制漏电流的能力越强,耦合到衬底的噪声越小,串扰越小。因此本文选择介电常数相对较小的BCB 介质作为CA-TSV 结构的内层介质。进一步对比发现,100 GHz 频点处远端串扰和近端串扰相差小于0.1 dB,相差很小。

图2 内层介质种类对S 参数的影响。(a) S11;(b) S21;(c) S31;(d) S41Fig.2 Influence of internal dielectric layer type on S parameters.(a) S11;(b) S21;(c) S31;(d) S41

1.2.2 外层介质种类对S参数影响

内层介质设置为BCB,外层介质种类分别设为BCB、SiO2、Si 介质,通过HFSS 仿真得S参数结果如图3 所示。由图3 可知外层介质相对介电常数越低,S11越小、S21越大,传输损耗越小。这是因为采用相对介电常数小的BCB 作为外层介质时,信号与接地铜环之间的耦合电容最小,因而相比于SiO2、Si 介质,其传输损耗最小。从图3 发现,外层介质相对介电常数越大,串扰抑制能力越强,串扰越小。显然,外层介质为Si 时串扰最小,且BCB 与SiO2相对介电常数较低,抑制漏电流能力都很强,因而在0.1~50 GHz 范围串扰几乎相等,随着频率增大,串扰差值逐渐增大,100 GHz 相差约0.69 dB。进一步对比发现,100 GHz频点处远端串扰和近端串扰相差很小,约0.24 dB。结合图2 分析可知,内外层介质种类不同时,CA-TSV远端串扰和近端串扰相差很小,为了方便,后面讨论串扰时,远端串扰曲线不再展示。

图3 CA-TSV 外层介质种类对S 参数的影响。(a) S11;(b) S21;(c) S31;(d) S41Fig.3 Influence of CA-TSV outer dielectric layer type on S-parameters.(a) S11;(b) S21;(c) S31;(d) S41

由图3 分析可知,外层单一种类介质CA-TSV 传输损耗减小(S11减小、S21增大)的同时,阵列串扰会增大,两者不可兼顾。且CA-TSV 外层介质寄生电容大小直接决定S11、S21的大小;而寄生电容与铜导体泄漏电流同时作用影响CA-TSV 之间的串扰。结合CATSV 寄生电容提取公式可知,内外铜导体之间寄生电容受到外层介质相对介电常数与内外径比值(介质尺寸)的调控,因此对外层介质合理选择十分重要。

2 混合介质CA-TSV 传输损耗及串扰研究

2.1 混合介质CA-TSV 模型及其传输损耗

由于外层单一种类介质填充时,当信号损耗最小时对应阵列串扰最大,反之亦然,信号损耗与串扰两者性能不可兼顾,综合考虑漏电流影响与结构可靠性,为使CA-TSV 能在TSV 阵列中表现出更好的传输性能,本文提出一种新型“BCB-Si-BCB” 外层混合介质CA-TSV 结构(如图1(b)所示),即内外铜导体之间采用外层BCB 包裹Si 的混合介质结构,整个模型由内到外依次为BCB-铜-BCB-Si-BCB-铜-SiO2层。

通过HFSS 仿真软件,对提出的“BCB-Si-BCB”混合介质CA-TSV 传输性能进行仿真,并与纯Si 介质、纯BCB 介质、“SiO2-Si-SiO2” 混合介质、“Si-BCB-Si” 混合介质CA-TSV 的传输损耗S11与S21值进行对比,如图4 所示,这里设定“BCB-Si-BCB” 混合介质CA-TSV 外层混合介质尺寸比为Win∶WSi∶Wo=1 ∶1 ∶1。由图4 综合分析可知,外层采用纯Si 介质的传输损耗最大,100 GHz 频点处,纯Si 介质S11最大-2.167 dB、S21最小-5.765 dB;两边加入SiO2变成混合介质层后S11值为-5.283 dB、S21值为-1.713 dB,传输损耗大幅降低,此结论不受混合介质尺寸比的影响,也明显优于“Si-BCB-Si” 混合介质的传输损耗;若采用相对介电常数更小的BCB 替换SiO2层后S11、S21参数再次得到较大优化,S11值为-7.504 dB、S21值为-0.922 dB,此结论同样不受混合介质尺寸比的影响;相比于传输损耗最低的纯BCB 填充的CA-TSV 结构,两者S11值相差约2.2 dB、S21值仅相差约0.41 dB。另外,从图3 可以看出纯BCB 介质填充时串扰最大,可知相比于除纯BCB 介质CA-TSV 结构以外的其他类型介质填充的CA-TSV 结构,本文提出的“BCB-Si-BCB” 混合介质CA-TSV 结构传输损耗更低,传输性能更优。

图4 混合介质CA-TSV 传输损耗分析。(a) S11;(b) S21Fig.4 Analysis of transmission loss of CA-TSV with outer mixed dielectric layer.(a) S11;(b) S21

2.2 混合介质尺寸及配比对CA-TSV 的S 参数影响

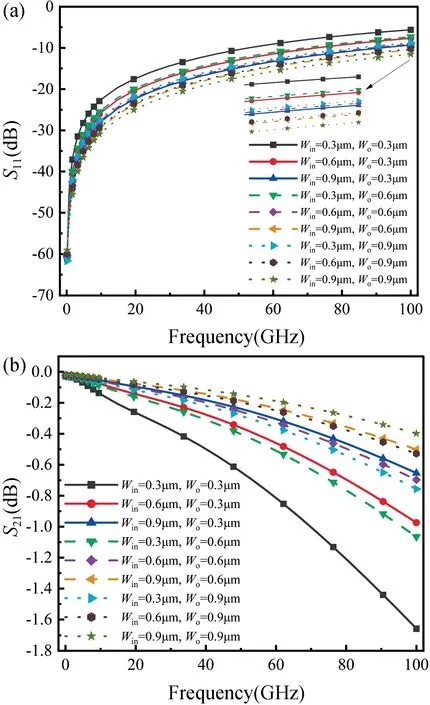

将“BCB-Si-BCB” 混合介质结构中高阻硅尺寸WSi固定不变,改变两侧BCB 介质尺寸进行分析,研究混合介质尺寸及配比对回波损耗S11与插入损耗S21的影响,将高阻硅尺寸WSi设置为0.9 μm,分别控制两侧BCB 介质尺寸从0.3 μm 到0.9 μm 变化,HFSS仿真结果如图5 所示。很明显,固定混合介质中心层Si 介质尺寸不变,随着Si 两侧BCB 尺寸增加,混合介质层总尺寸增大,从而使S11递减、S21递增,即传输损耗减小、传输性能提高。

进一步对比发现: 在混合介质层总尺寸不变的情况下,Win=0.6 μm、Wo=0.3 μm 时S11、S21参数结果优于Win=0.3 μm、Wo=0.6 μm;Win=0.9 μm、Wo=0.3 μm 时S11、S21参数结果优于Win=0.3 μm、Wo=0.9 μm;因此,可以推断当混合介质总尺寸与中间层Si 尺寸固定的条件下,内层BCB 所占比例越高,S11越小、S21越大,即传输损耗越小,且S11变化幅度较小在0.4~0.5 dB 之间。

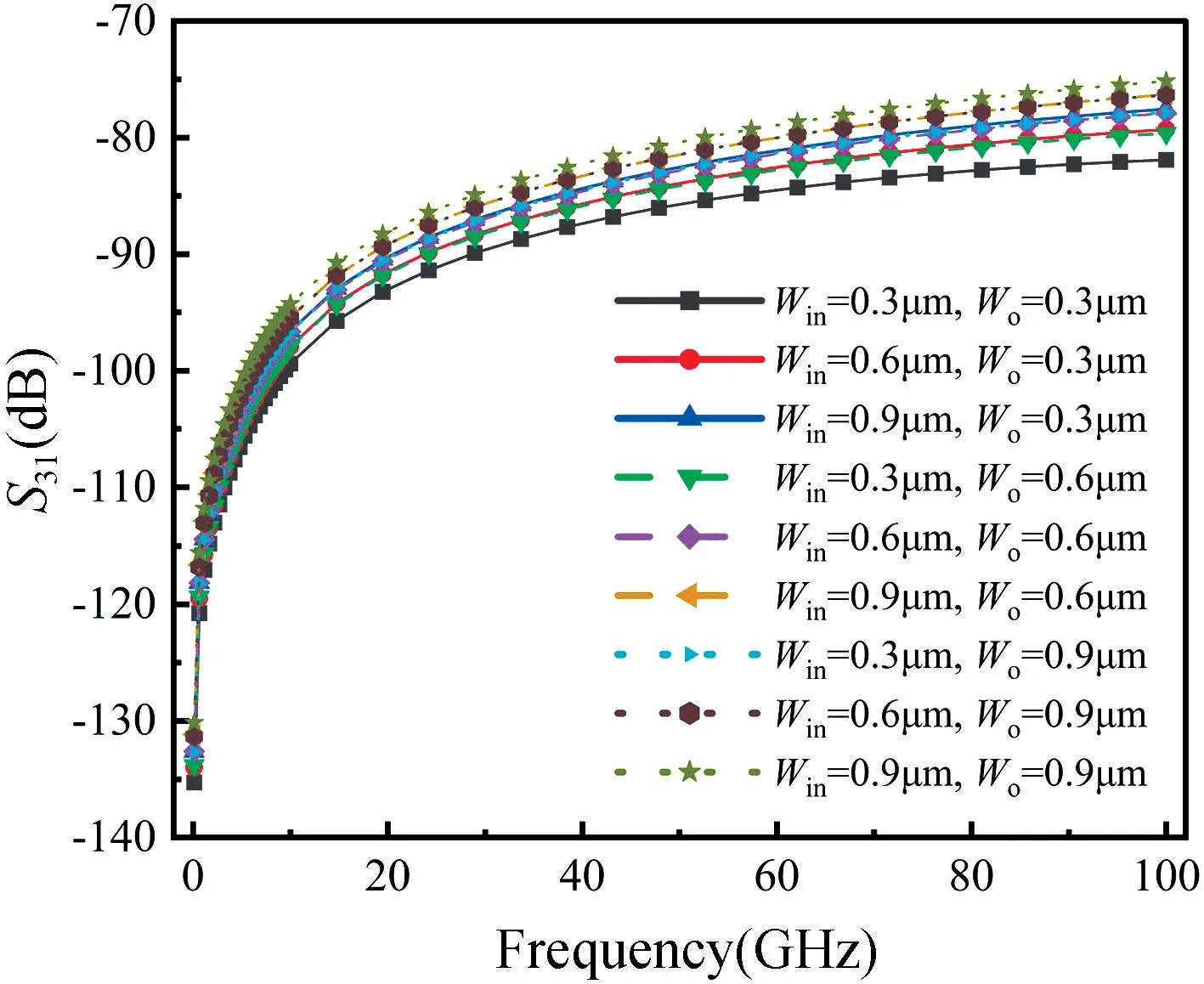

图6 给出了混合介质尺寸及配比对CA-TSV 结构串扰的影响,从仿真结果可知随着混合介质CA-TSV 两侧BCB 尺寸增大,混合介质层总尺寸增加,从混合介质层耦合到RDL 层的噪声增加,串扰增大;这些正好与图5中传输损耗逐渐减小的变化趋势相反。同时发现,在Win=0.3 μm、Wo=0.3 μm 时串扰值最小,100 GHz 时为-81.914 dB,这时混合介质比为Win∶WSi∶Wo=1 ∶3 ∶1。

图5 混合介质尺寸及配比对CA-TSV 传输损耗的影响。(a) S11;(b) S21Fig.5 Influences of size and proportion of mixed dielectric layer on transmission loss of CA-TSV.(a) S11;(b) S21

图6 混合介质尺寸及配比对CA-TSV 串扰的影响Fig.6 Influence of size and proportion of mixed dielectric layer on CA-TSV crosstalk

2.3 不同混合介质TSV 结构的串扰分析

硅通孔是三维集成电路的核心技术,随着集成度不断提高,TSV 数量不断增加、尺寸间距不断缩小的同时信号间耦合串扰越加严重,串扰的加重会导致高速数字信号之间产生码间串扰,引起传输错误,从而影响信号传输质量。因此一种低串扰的混合介质配比方式显得尤为重要。根据前述分析,采用“BCB-Si-BCB” 混合介质比Win∶WSi∶Wo=1 ∶3 ∶1 时的CATSV 结构与纯BCB 介质CA-TSV 结构及丁英涛等[16]提出的“Si-BCB-Si” 混合介质CA-TSV 结构进行对比,同时将基于“BCB-Si-BCB” 混合的CA-TSV 与同轴型TSV 串扰进行对比,仿真结果如图7(a)所示。由图7(a)可知“BCB-Si-BCB” 混合介质CA-TSV相比其他结构,串扰最低。在100 GHz 频点处“BCB-Si-BCB” 混合介质CA-TSV 相比于同样混合介质的同轴型TSV 串扰减小了约1.4 dB,也比“Si-BCB-Si”混合介质CA-TSV 结构串扰减小了约1.5 dB,这些结果表明“BCB-Si-BCB” 混合介质CA-TSV 结构模型抑制耦合串扰能力明显优于其他混合介质结构。同时将表1 中CA-TSV 模型尺寸同比放大一倍,串扰仿真结果如图7(b)所示。很显然,模型尺寸放大一倍,其仿真结果与图7(a)结论一致,由此可知该模型结论不受尺寸限制,对于大尺寸同轴TSV 与CA-TSV 结构,同样可以克服平坦化过程中内部Si 介质易断裂的现象[16]。

图7 “BCB-Si-BCB” 混合介质CA-TSV 串扰对比。(a)初始模型;(b)尺寸扩大模型Fig.7 CA-TSV crosstalk comparison of BCB-Si-BCB mixed dielectric layer.(a) Initial model;(b) Size expansion model

3 混合介质CA-TSV 电路模型及验证

3.1 混合介质CA-TSV 等效电路模型

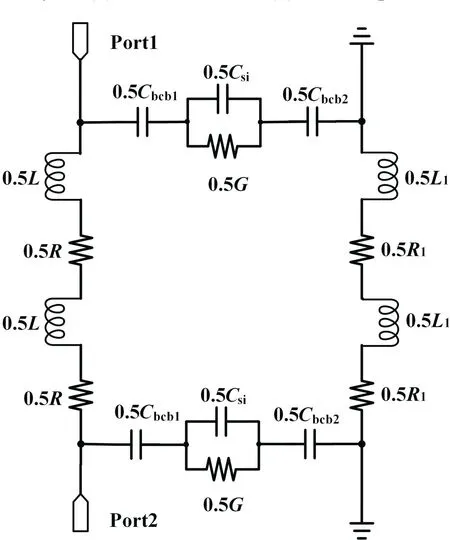

根据图1(b)所示的“BCB-Si-BCB” 混合介质CA-TSV 截面图,建立如图8 所示“BCB-Si-BCB”混合介质CA-TSV 的单位长度等效电路模型。基于Ndip 等提出的圆柱形TSV 寄生参数提取的改进方法[15]及CA-TSV 寄生电阻参数提取的方法[13-14,19],综合考虑集肤效应和邻近效应的影响,对单位长度混合介质CA-TSV 等效电路模型RLCG 参数进行提取,得出了如下适应本文提出的混合介质CA-TSV 结构寄生参数提取方程。

图8 混合介质CA-TSV 等效电路模型Fig.8 Equivalent circuit model of CA-TSV with outer mixed dielectric layer

混合介质CA-TSV 内外铜导体的电阻R由公式(1)计算:

式中:r1=r0+WCu,为信号铜导体外半径;r2=r1+Wox,为接地铜导体内半径,其中Wox=Win+WSi+Wo为外层介质环总厚度;ρ为TSV 的电阻率;δ为趋肤深度。

式中:f是频率;μ为导体磁导率。

考虑传输线的电感和电阻之间的频率相关关系,混合介质CA-TSV 内铜环间混合介质电感L用公式(3)表示,同理代入对应参数即可得L1。

式中:μ0为真空导体磁导率。

混合介质层寄生电容由三部分组成,Si 介质两侧的BCB 层寄生电容表达式如下:

式中:ε0为真空介电常数;εbcb为BCB 介质相对介电常数;Win为内侧BCB 介质层尺寸;Wo为外侧BCB 介质层尺寸,且Win=Wo;WSi表示硅介质层尺寸。

为了更好地表述Si 介质层损耗,通过安培定律引入复介电常数见式(6)和(7)[15,20]:

式中:σeff是有效电导率;εSi为硅电导率;tanδ默认为硅的导电性而产生的损耗,值为0.004,这里不考虑硅的极化损耗。

参照BCB 层寄生电容表达式(4)和(5),根据式(7)所得硅介质层复介电常数,可得等效电路中硅介质层的复电容:

则铜信号导体与接地导体之间的复电容可表示为三层介质层电容的串联形式:

结合复导纳公式:

可知介质层电导:

3.2 仿真结果验证

在ADS 中建立图8 所示的等效电路模型,将RLCG 参数提取公式代入Matlab 中计算,并将计算结果代入等效电路原理图中,仿真频率为0.1~100 GHz,步长0.1 GHz。将ADS 仿真结果与HFSS 仿真得到的S11、S21曲线进行对比,如图9 所示。HFSS 仿真得到的S11值随着工作频率增加而增大,且S11曲线整体平滑,解析法得到的S11参数在0.1~20 GHz 频段时与HFSS 仿真结果相比有一定误差,但变化趋势一致,且随着工作频率增加逐渐与HFSS 仿真结果重合;另外,解析法与HFSS 仿真得到的S21参数曲线均随着频率增加而减小,且变化速率呈“快-慢-快” 的趋势,误差在可控范围,曲线总体拟合度较高,证明了本文提出的“BCB-Si-BCB” 混合介质CA-TSV 电路模型的准确性。

图9 HFSS 与ADS 仿真结果对比Fig.9 Comparison of simulation results between HFSS and ADS

4 结论

本文首先对CA-TSV 内外层介质材料对传输特性及串扰的影响进行分析,发现内层介质相对介电常数越小,漏电流抑制能力越强,串扰越小,且对S11、S21参数无影响。外层介质相对介电常数越大,串扰越小,传输损耗越大,两者变化恰好相反。由于单一介质难以平衡传输损耗与串扰,综合考虑BCB 介质阻隔漏电流效果远优于SiO2介质且结构稳定性强,因此提出一种组合为“BCB-Si-BCB” 混合介质CA-TSV 结构。研究发现,CA-TSV 混合介质尺寸越大,传输损耗越小,串扰越大;当混合介质总尺寸与中间层Si 尺寸固定不变,内层BCB 占比越高,串扰越大,变化幅度在0.3 dB 左右,与S11减小幅度基本一致。在“BCB-Si-BCB” 混合介质比1 ∶3 ∶1 时,相比于纯BCB 介质填充、“Si-BCB-Si” 混合介质填充CA-TSV,进一步降低了TSV 之间的耦合串扰。最后,建立“BCB-Si-BCB” 混合介质CA-TSV 等效电路模型,对传统参数提取公式进行改进,经仿真验证0.1~100 GHz 频段内具有良好的一致性。