一种面向基于闪存的脉冲卷积神经网络的模拟神经元电路

2023-02-18顾晓峰刘彦航虞致国钟啸宇潘红兵

顾晓峰 刘彦航 虞致国* 钟啸宇 陈 轩 孙 一 潘红兵

①(江南大学物联网技术应用教育部工程研究中心电子工程系 无锡 214122)

②(南京大学电子科学与工程学院 南京 210023)

1 引言

近年来,基于闪存(Flash)、阻变存储器(Resistive Random Access Memory, RRAM)等非易失性器件和存算一体(Computing In Memory, CIM)网络技术的神经网络打破了传统冯诺依曼体系架构“存储墙”的限制,在图像识别、图片分类和语音识别等领域展示出了强大的计算能力,甚至具备了超越人脑的准确性[1-3]。与RRAM等技术[4-6]相比,Flash可以通过成熟的互补金属氧化物半导体(Complementary Metal Oxide Semiconductor, CMOS)工艺进行制造,促进了器件阵列与外围CMOS电路的大规模集成[7]。典型的基于Flash的卷积神经网络(Convolution Neural Network, CNN)[8,9]利用两个器件的跨导差值存储一个带符号的权重数据,二进制数字输入通过数模转换器(Digital to Analog Converter, DAC)转换为模拟电压输入阵列。乘法运算和加法运算分别利用欧姆定律和基尔霍夫电流定律实现,采用模数转换器(Analog to Digital Converter, ADC)、数字逻辑控制电路(logic)、寄存器在数字域完成滑动操作,将前一层的模拟输出转换为下一层的二进制输入。因此,在大规模CNN中,为了完成模拟数据的传递,需要大量的ADC、寄存器等外围模拟、数字电路,在这种情况下,这些阵列外围电路占据着大量的硬件成本及功耗[10,11],这成为提高卷积神经网络能效比的突破点之一。

在此基础上,研究人员借鉴人脑中神经元的工作模式,提出了基于脉冲进行数据传输的脉冲神经网络(Spiking Neural Network, SNN)[12]和脉冲卷积神经网络(Spiking Convolutional Neural Network,SCNN)[13-15]。网络中的层间数据信息通过脉冲信号(0/1)进行编码、输入和输出,可以省去大量的ADC和DAC。目前SNN的训练主要通过类似于生物学的无监督学习规则实现,难以支持复杂的实际应用,而SCNN则可以兼顾CNN训练方式简单和SNN功耗低的优点,得到了大量的关注和研究。

SNN和SCNN中的脉冲神经元根据建模种类不同,分为漏积分发放(Leaky Integrate-and-Fire,LIF)神经元和积分发放(Integrate-and-Fire, IF)神经元,但是在SCNN中,LIF模型的电荷泄漏过程会延长神经元膜电位到达阈值电压的时间,降低网络的速度和精度。

目前,针对基于Flash的SCNN神经元模拟硬件实现的报道较少,只对积分发放和复位功能进行了模拟设计,没有完整的从电压箝位到电流读出减法再到电流积分发放的功能设计,同时大多数模拟设计没有考虑低电流读出时的速度问题以及泄放到零的复位方式所带来的信息丢失问题。因此,本文面向基于Flash的SCNN设计了一种IF型模拟神经元电路,电路具备完整的电压箝位、电流读出减法和积分发放功能,并且针对上述问题,提出一种大幅提高电流读出速度和读出范围的方法,以及一种新型脉冲神经元复位方法,并进行了硬件实现。

2 基于Flash的SCNN

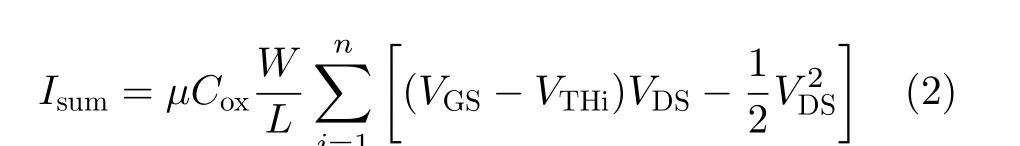

图1为基于Flash的SCNN工作示意图,权重信息通过两个Flash器件的跨导差值进行存储,存储同一权重的两个Flash器件的栅极连接同一条字线(Word Line, WL)、源极(Source Line, SL)接固定电压,漏极连接同一条位线(Bit Line, BL)并被箝位在固定电压。输入信息通过脉冲编码输入到WL上,当WL上信号是高电平时,在BL端会产生一个大小为

的单位电流,其中,µ是Flash器件的迁移率,Cox是其栅氧电容,W, L分别是其宽、长,VTH是其阈值电压。当WL上信号是低电平时,不会产生电流,通过基尔霍夫定律,在BL端输出累加电流

其中,n是卷积运算中权重的数量,然后将相邻BL的累加电流相减得到差分电流

以此完成输入数据与权重的乘加运算。由于ΔVTHi是带符号的,所以Isub可能为正值或者负值。最后对Isub进行积分,当在积分周期结束时刻t时,积分电压(Vintg)达到所设脉冲发放阈值电压(Vth)时,神经元电路输出高电平,表现为发放脉冲,神经元复位。相反,当Vintg未达到所设脉冲发放阈值电压Vth时,神经元不发放脉冲信号,积分电压进行保持,并在下一个积分周期t~t+T内继续积分。

传统的模拟神经元电路如图1所示,由运放、电阻和电容组成的RC积分电路对输出电压信号Vvmm进行积分,然后通过比较器进行电压比较,发放脉冲信号。然而Vvmm如何产生以及是否支持正负电流积分并没有论及。文献[16]提出了一种正负电流减法电路,但是减法线性度较差,在此基础上,文献[17]进行了改进,采用了cascode结构,但是未考虑低电流时读出速度慢以及低积分电压时的cascode不饱和问题。

图1 基于Flash的SCNN

文献[15,16]中提出的神经元电路在发放脉冲后均通过与电容并联的开关将积分电位泄放到0,Vintg表达式为

然而,该复位方式会带来一个问题:若积分周期后,Vintg远远高于Vth,此时若将电压泄放到零则会造成电荷的过度泄放,导致信息的丢失,降低脉冲发射率。现考虑一种极限情况,若在某一个积分周期结束时,Vintg略低于Vth,此时神经元不会输出脉冲,然而下一个积分周期中Isub为满量程输出,那么该积分周期结束时,Vintg≈2Vth,若此时仍然将积分电压泄放到零,那么几乎会造成一个满量程信息的丢失。并且随着计算的不断进行,这种丢失信息的情况会越来越多,严重影响神经网络的准确率。

3 本文所提IF型模拟神经元电路

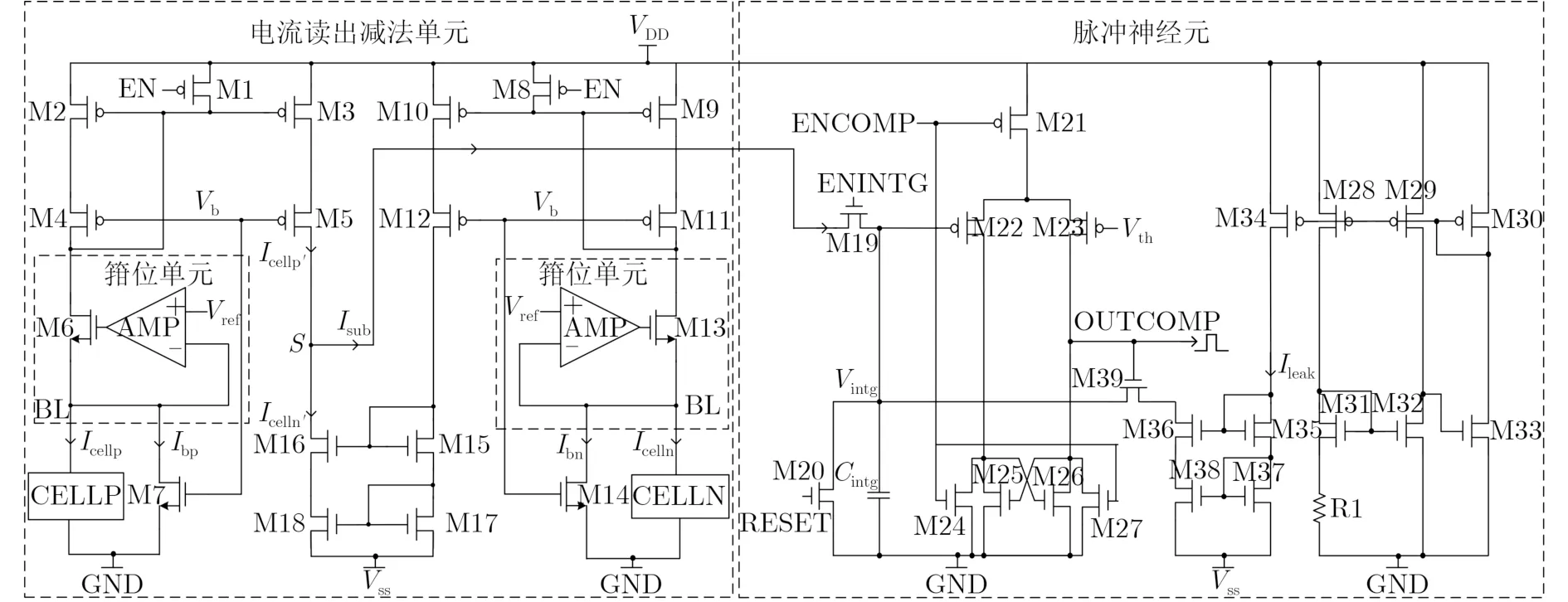

根据第1,2节对SCNN及外围模拟电路的分析,本文提出一种IF型模拟神经元电路,如图2所示,包括:(1)位线箝位单元,负责为Flash位线提供稳定的箝位电压;(2)电流读出减法单元,负责对BL端输出电流进行快速读出并将相邻BL端的电流相减,得到差分电流;(3)脉冲神经元,负责对差分电流进行积分累加,并在达到一定条件时发放脉冲,并固定泄放一个阈值电压。

3.1 电流快速读出减法单元

模拟神经元电路中电流读出减法单元的电路架构如图2左边虚框所示,CELLP和CELLN是存储同一个权重的两个Flash器件,箝位单元负责将器件的位线电压箝位在固定电压Vref,EN为读出使能信号,当信号为低电平时,M1和M8导通,M2, M3,M9, M10被关断,此时读出减法单元功耗为零。当使能有效后,M1和M8关断,电路进入读出模式。阵列内部经过运算后,在CELLP和CELLN的BL端分别输出电流Icellp和Icelln,电流读出减法电路负责将Icellp和Icelln进行读出和减法。其中,M2~M5和偏置电压Vb组成的P型共源共栅电流镜将Icellp进行读出,产生电流Icellp', M9~M12和Vb组成的P型共源共栅电流镜和M15~M18组成的N型共源共栅电流镜将Icelln进行读出,产生电流Icelln'。然后在S点根据基尔霍夫电流定律产生差分电流

图2 IF型模拟神经元电路

M17与M18的源极接负电源电压VSS,目的是确保M15~M18始终处于饱和区,保证电流读出的精度。同时,保证Isub不论为正值或是负值都可以被准确读出,防止出现信息丢失的情况。单元中电流镜均采用共源共栅结构,输出阻抗较高,提高电流减法的线性度。

考虑到实际工作中,神经网络稀疏性较大,阵列输出电流Icellp, Icelln较小,读出速度较慢。为了解决低电流的读出速度问题,增加了一条电流旁路,以提高电流读出的速度。通过M7,M14来提供旁路电流Ibp和Ibn,栅极接P型电流镜中的偏置电压Vb,漏极与存储单元位线端相连,源极接地,因为M7, M14的3端电压均相等,所以

因此,通过增加支路上流过的电流,使支路寄生电容充放电速度加快,提高低电流时的读出速度,进而提高读出电路的读出范围。

在S节点

通过以上分析,该设计具有以下5个优点:

(1)加入旁路电流,可以提高电流的读出速度和读出范围;

(2)增加的偏置电流可以在电流减法时减去,不会影响电流减法的精度;

(3)可以避免引入带隙基准电流源带来的额外面积和功耗开销;

(4)虽然未引入带隙基准电流源电路,但是由于M7和M14的3端电压均是相等的,因此两个MOS管提供的旁路电流几乎是相等的,在提高电流读出速度和读出范围的同时,保证了电流减法的精度;

(5)可以根据实际阵列电流的读出范围和电路的功耗要求设计M7,M14的宽长比,与带隙基准电路相比,调节更加方便。

3.2 高精度位线箝位单元

从第2节可知,代表阵列运算结果的BL端输出电流与位线电压成正比,所以需要箝位单元精确稳定BL端电压。

本文所提箝位单元利用运放对位线进行箝位,电路结构如图3所示。

图3 位线箝位单元

考虑到电流的高速读出和位线电压的精准箝位,舍弃了两级放大运放结构,采用1级套筒式结构和M10组成的源跟随反馈结构进行箝位。

同时,由于BL端电压在工作时箝位在Vref,因此Q点电压与读出电流Icell的大小相关,设计时通过适当增加M10管的宽长比,可以减弱Q点电压的波动幅度,进一步提高箝位电压的稳定性。

3.3 固定泄放阈值电压的脉冲神经元

本文所提脉冲神经元电路结构如图2右边虚框所示,Cintg为积分电容,RESET为复位信号,ENINTG为积分使能信号,在积分周期结束后,M21~M27组成的动态锁存比较器将积分电压Vintg与阈值电压Vth进行比较,ENCOMP为比较器比较使能信号。当ENCOMP为高电平时,比较器处于复位阶段,输出信号OUTCOMP为低电平,当ENCOMP处于下降沿时,比较器对Vintg和Vth进行比较,由于动态锁存比较器功耗很低,所以适用于神经网络这种低功耗的应用场景。M39为电压泄放开关。

为了解决第2节提到的信息丢失问题,将脉冲神经元复位方式由直接泄放到地优化为通过泄放电流Ileak进行泄放,在复位阶段仅令Vintg泄放一个阈值电压Vth。Ileak由M28~M33、电阻R1组成的3支路基准电流源和M34~M38组成的电流镜产生,其中,M37,M38源极接负电源电压VSS,以保证电流镜的复制精度。

脉冲神经元电路工作时序如图4所示:在初始复位阶段,RESET信号有效,释放掉Cintg上的残余电荷。在积分阶段,信号ENINTG置高,置高时间即积分时长,通过Cintg对差分电流Isub进行积分,电容上级板积分电压变化量为

图4 脉冲神经元工作时序

其中,Tintg为积分时长,C为积分电容Cintg的值。积分结束后,比较器比较使能信号ENCOMP由高电平下降为低电平,进行电压比较,若Vintg≥Vth,比较器输出OUTCOMP翻转为高电平,发放脉冲,同时,电压泄放开关M39导通,Cintg极板电荷以Ileak的速度进行泄放,Vintg表达式为

其中,Tleak为ENCOMP信号低电平持续时间,即泄放时长。通过调整R1和Tleak的大小,使得

因此,在复位阶段不会泄放掉多余的电荷,防止出现信息丢失的情况,提高神经网络的精度,相反,如果Vintg<Vth,积分电压保持,不发放脉冲。

4 后仿真、测试结果及分析

4.1 电路后仿、芯片测试结果及分析

模拟神经元采用55 nm CMOS工艺进行电路设计、流片测试,图5为电路版图,面积为0.0042 mm2。其中Ⅰ是电路中的泄露电流产生电路,Ⅱ是电压箝位、电流读出减法和积分发放电路,其中Cintg是积分电容,采用工艺库中温度系数低、精度高的MOM电容。

图5 模拟神经元电路版图

使用Keysight E3631A型电压源、B2902B数字源表以及FPGA开发板等仪器和设备对芯片性能进行测试,图6是芯片测试板照片。

图6 模拟神经元电路测试板

电路的电流读出速度、脉冲神经元功能等动态特性通过后仿测得,考虑到神经元电路易受工艺角、温度等条件的影响,所以主要针对以下3种条件进行后仿:tt与25°C(经典),ss与80°C(最慢),ff与-20°C(最快)。位线箝位精度、电流减法线性度等静态特性通过芯片测试板进行测试。

图7为电路在tt与25°C条件下0~20 μA电流输出范围内电流读出速度的后仿波形图,其中红色曲线为增加旁路电流时的结果,蓝色曲线为未增加旁路电流的结果,可以看出,在输出电流为0 μA时读出时间从80 ns缩短到22 ns,读出速度提升了263.6%,在输出电流为20 μA时读出时间从40 ns缩短到20 ns,读出速度提升了100%。

图7 电流读出时间后仿波形图

其余PVT条件下的电流读出时间如表1所示,在ss与80°C条件下,电流读出速度最慢,在ff与-20°C条件下,电流读出速度最快,通过分析推断ss与80°C时,旁路电流最小,导致电流读出速度最慢。相反,在ff与-20°C时,旁路电流最大,电流读出速度最快。

表1 电流读出时间(ns)

位线箝位电压误差的测试结果如图8所示,在0~20 μA电流输出范围内,箝位电压误差小于0.2 mV,整体波动范围小于0.4 mV。

图8 位线箝位电压误差测试结果

位线箝位电压误差的测试结果与仿真结果对比如表2所示,误差基本一致,推断实际制造偏离了tt工艺角,仿真在ff与-20°C时误差最小,分析此时MOS管跨导最大,运放增益最大,同时Q点电压波动最小,导致箝位电压误差变小。

表2 位线箝位电压误差(mV)

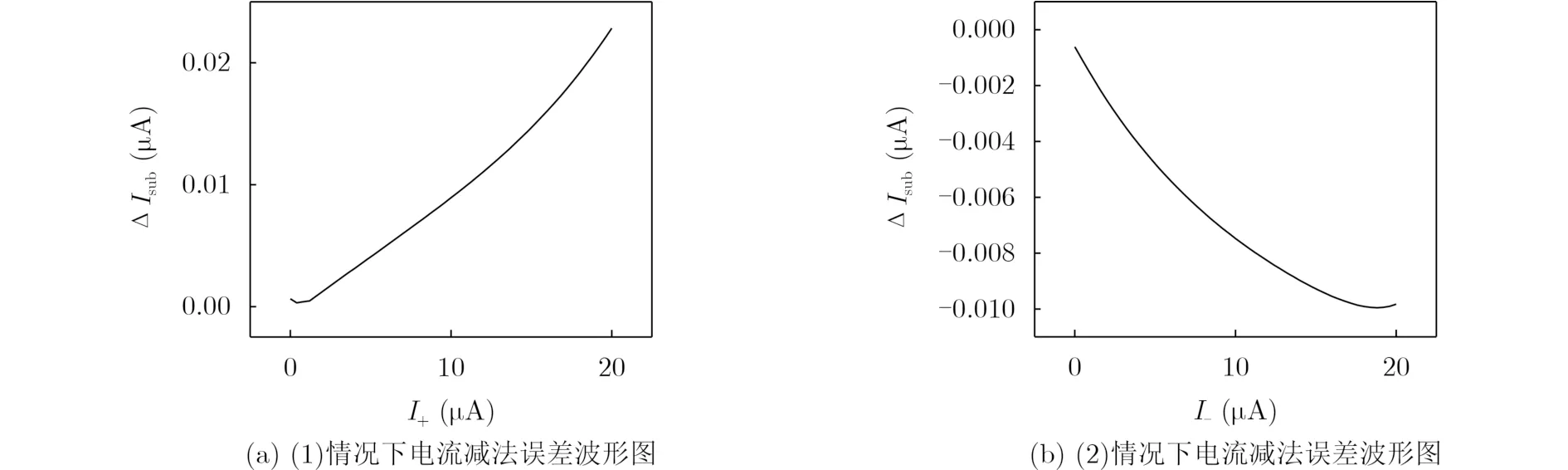

为了测试电流读出减法的线性度,分别令相邻两条BL输出电流I+, I-按照以下两种情况变化:(1)I-=0 μA, I+从0~20 μA线性变化;(2)I+=0 μA, I-从0~20 μA线性变化,通过测试差分电流Isub(I+-I-)的误差ΔIsub计算电流读出减法的线性度,结果如图9所示,在情况(1)下电流减法线性度可达99.9%,在情况(2)下电流减法线性度可达99.95%,表明3.1节所提出的加入旁路电流的方法几乎不会影响电流减法的精度。电流减法线性度测试结果与PVT后仿结果对比如表3所示,相对偏差较小,基本符合后仿结果。

表3 电流减法误差(nA)

图9 电流读出减法误差测试结果

综上所述,电路中箝位单元和电流读出减法单元在0~20 μA的电流输出范围内具有良好的精度、速度和稳定性等性能。

根据图4设计的工作时序对脉冲神经元进行后仿,如图10(a)所示,神经元可以在积分窗口内实现对正负差分电流的积分,表现为积分电压Vintg的上升和下降,并且当积分电压达到所设脉冲发放阈值电压Vth(100 mV)时,比较器输出翻转为高电平,发放脉冲,并且在复位阶段,积分电压通过泄放电流固定下降一个Vth(99.8 mV),符合3.3节提出的泄放方式。PVT仿真结果如图10(b)所示,电路功能正常,但是积分电压出现了偏差,分析是积分电容受到了PVT条件的影响,容值发生了变化。

本文所提IF型模拟脉冲神经元电路与国内外相关研究的对比如表4所示。

表4 模拟神经元性能总结以及与相关文献模拟神经元对比

4.2 SCNN识别准确率测试结果及分析

为测试模拟神经元电路性能对SCNN识别准确率的影响,选取了两种经典神经网络LeNet和AlexNet分别对MNIST数据集和CIFAR-10数据集进行识别率测试。

对箝位电路、电流读出减法电路和所实现的复位方式进行模型搭建,将模型带入到网络算法中进行测试,两种网络的测试结果分别如图11(a)和图12(a)所示,两图中红色曲线为理论模型(未考虑误差),泄放到零模式下的识别率测试曲线;黑色曲线为电路误差模型,泄放到零模式下的测试曲线;蓝色曲线为电路误差模型,固定泄放阈值电压模式下的测试曲线。纵轴是识别准确率,横轴是网络的运行结束时间参数。图10(b)和图12(b)是测试结果局部放大图。从红色和黑色曲线对比可以看出,与理想模型相比,模拟神经元电路的误差对网络识别准确率并未产生明显影响,仅有0.2%~0.3%的下降,在可接受范围之内。而从蓝色与黑色曲线可以看出,与直接泄放到0的复位方式相比,泄放固定电压的复位方式令LeNet对MNIST的识别率上升了1.4%,图12中,AlexNet对CIFAR-10的识别率则上升了38.8%,均表现出了上升行为,表明泄放固定电压的复位方式在一定程度上保证了信息的完整度,提升了SCNN的识别准确率。由于两种网络的权重位数等参数一致,因此分析推断上升幅度的差别主要是由于两种网络的脉冲发放阈值电压参数设置相差较大,AlexNet所设阈值电压较小,脉冲发放频率高,信息丢失量越大,采用新型复位方式后的识别率上升效果也就越明显。

图10 脉冲神经元仿真结果

图11 LeNet对MNIST数据集的识别准确率测试结果

图12 AlexNet对CIFAR-10数据集的识别准确率测试结果

4.3 设计参数考量与分析

权重位数:考虑到网络权重位数的增加会提高对模拟电路的精度要求,电路误差对神经网络的识别率的影响也更加明显,因此评估了不同权重位数下电路模型对网络识别率的影响。图13(a)给出了LeNet权重位数与MNIST识别率的关系,图中黑色曲线是理想模型,红色曲线是误差模型。可以看出,理想模型下电路的识别率在4 bit时达到最高,随着位数的增加,识别率不再有明显上升。而误差模型下,识别率在4 bit时达到峰值,说明在此之前位数对网络识别率的影响大于电路误差的影响,而随着位数的不断增加,电路误差的影响逐渐明显。

图13 采用不同权重位数与电容偏差的LeNet对MNIST数据集识别准确率测试结果

电容偏差:通过脉冲神经元的PVT仿真结果可以看出,积分电容值易受制造工艺偏差的影响,一般情况下,电容工艺偏差在20%以内。图13(b)表示电容偏差与LeNet识别准确率的关系,电容偏差越大,识别率下降越严重。因为电容值会直接影响积分电压的变化量,进而影响脉冲的发放频率。

5 结论

本文采用55 nm CMOS工艺提出了一种面向基于Flash的SCNN的IF型模拟神经元电路,电路实现了位线箝位、电流读出减法和积分发放功能。同时提出一种提高电流读出范围和读出速度的方法,并且在传统神经元的基础上增加了泄放固定阈值电压复位功能,保证了信息数据的完整性。电路后仿真结果表明,在20 μA电流输出时,读出速度提升了100%,在0 μA电流输出时,读出速度提升了263.6%,脉冲神经元积分和复位功能正常。流片测试结果显示,在0~20 μA电流输出范围内,箝位电压误差小于0.2 mV,整体波动范围小于0.4 mV,电流减法线性度可达到99.9%,与后仿真结果基本一致。将模拟神经元电路行为进行模型搭建并通过SCNN算法测试,结果显示,电路误差对神经网络准确率的影响在可接受范围内,同时提出的新型复位方式可以提高识别准确率。以上结果表明神经元电路功能完整并且具有优良的性能,为高性能SCNN阵列外围神经元电路设计提供了实用的模拟硬件实现方案。