基于薄外延的ESD 结构设计

2022-08-31李晓蓉吴建东高国平

李晓蓉,吴建东,高国平

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

静电放电(ESD)脉冲对芯片放电会产生瞬间大电流及高电压。瞬间大电流会使器件内部产生极大热量而无法及时散出,造成金属熔断、PN 结热损毁等,导致器件开路或短路;瞬间高电压会引起绝缘层击穿,漏电增加,导致功能失效或电参数超差[1-2]。芯片通过内部集成ESD 保护器件,在ESD 脉冲产生时依靠ESD 保护器件泄放瞬态大电流,从而避免芯片内部常规器件受到大电流或高电压的损伤[3-4]。

在空间辐射环境中,CMOS 集成电路中固有的寄生可控硅(SCR)结构易受空间粒子轰击触发单粒子闩锁效应(SEL)[5],该效应在电源与地之间形成不断增大的电流,致使器件失去功能甚至被烧坏,因此必须对抗辐射芯片进行SEL 加固设计。针对SEL 的加固方法有多种[6-7],其中采用3 μm 左右薄外延可基于已有非抗辐射电路,在不对版图进行更改的基础上即可满足SEL 性能要求,避免了常规的版图加固设计,能有效降低版图设计难度、减小抗辐射芯片面积并提升芯片性能,具备良好的应用场景。

本文对代工厂提供的栅极接地MOS(GGMOS)结构的ESD 性能进行评价及分析,开发了新的ESD 结构并优化了ESD 保护网络。

2 GGMOS 结构在薄外延下的性能分析

代工厂提供的全芯片GGMOS 防护结构中NMOS 的栅端、源端及体接触均接地。图1(a)为GGMOS 等效截面图,图1(b)为传输线脉冲(TLP)I-V曲线示意图。电路正常工作时,压焊块(PAD)处于常规工作电压,GGMOS 关断。当PAD 受到ESD 应力时,对应的GGMOS 漏端电压升高,造成漏端对衬底的PN 结反向击穿,击穿后产生的电流少部分形成寄生NPN 管的基极电流,多数形成衬底电流,通过寄生电阻RPwell流向体接触形成寄生NPN 管的基极电势,当该电势达到0.7 V 左右时,寄生三极管导通,此时GGMOS 的漏端电压对应于图1(b)的触发电压Vt1,基于寄生NPN 管的电流放大效应,基极电流提供自偏置,此时不需要寄生NPN 管维持击穿状态来提供基极电流,漏极电位返回到相对较小的保持电压,GGMOS发生回滞现象,对应的保持电压为图1(b)的Vh,随着寄生NPN 管放电电流的增加,集电极与发射极间电压不断增加导致自热效应增强,最终发生热击穿,热击穿电压对应于图1(b)的Vt2,It2为失效电流,It2值体现GGMOS 结构的稳健性。

图1 GGMOS 等效截面及TLP I-V 曲线

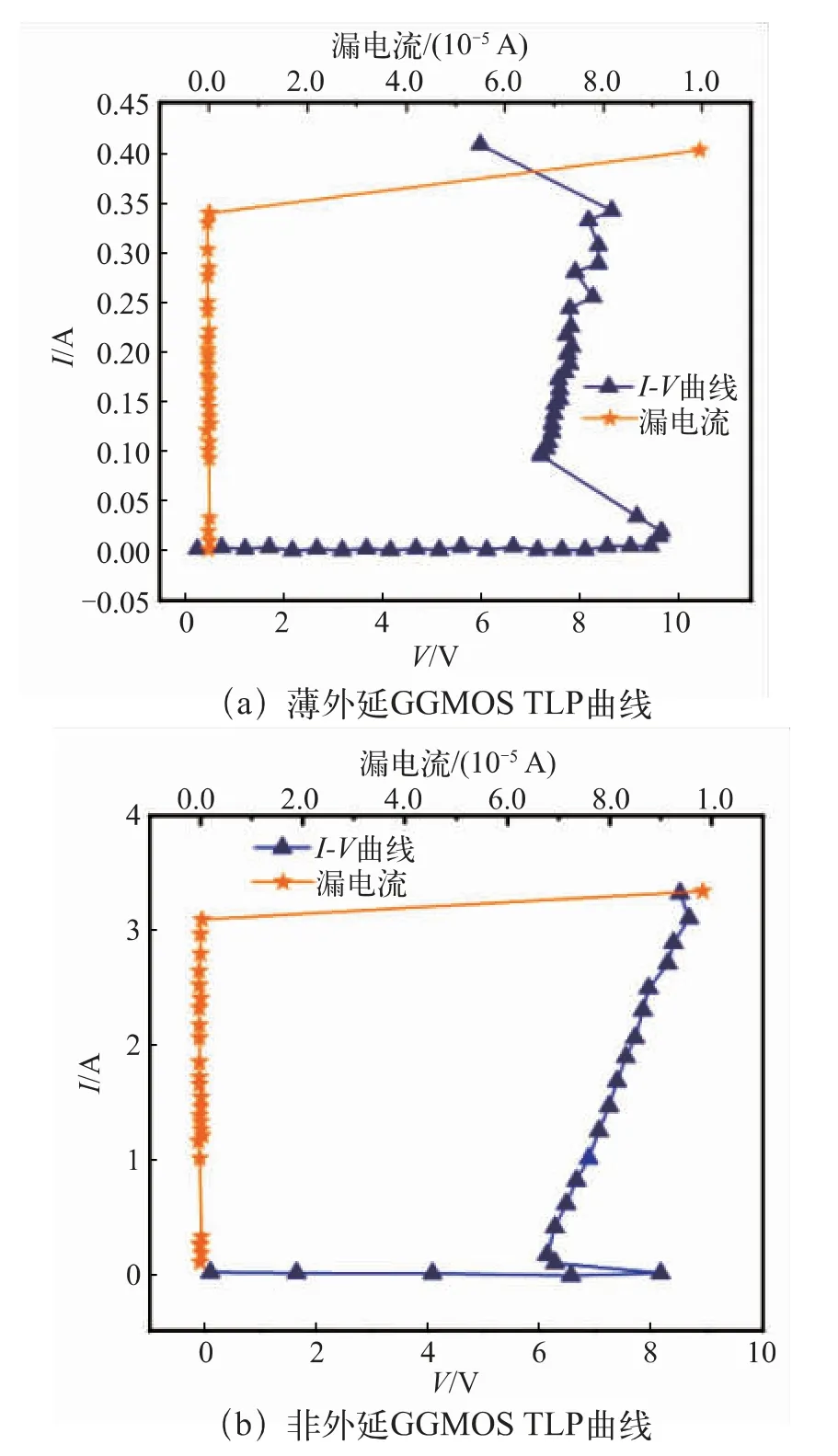

薄外延下使用GGMOS ESD 结构,经过ESD 摸底测试,电压只能达到500 V,性能明显减弱。对薄外延下GGMOS 结构进行TLP 分析,TLP 结果如图2(a)所示,代工厂提供的非外延片GGMOS TLP 结果如图2(b)所示,根据TLP 曲线对比,薄外延后的Vt1较非外延由8.2 V 左右增加至9.5 V 以上,且对应的It2由3.0 A 降低至0.35 A 左右,薄外延后GGMOS 结构电流泄放能力只有非外延GGMOS 结构的近1/10,同时0.35 A 的失效电流与500 V 摸底测试结果也基本符合。依据GGMOS 结构工作机理,电流需经衬底电阻形成寄生NPN 管基极电势,由于薄外延大大降低了衬底电阻,需要更大的衬底电流才能打开寄生三极管。增加衬底电流只能通过提升GGMOS 漏端对衬底的PN 结反向击穿电压实现,即GGMOS 漏端需要更大的Vt1,GGMOS 的Vt1升高后导致GGMOS 内部叉指结构无法均匀打开,局部叉指的寄生NPN 管打开后迅速热击穿,It2值明显降低。

图2 薄外延及非外延GGMOS TLP 曲线

3 电源钳位ESD 结构设计与仿真

由于GGMOS 的寄生NPN 管在薄外延条件下难以满足ESD 性能要求,本文采用了电源钳位ESD 结构,该结构依靠MOS 器件沟道导通状态,采用较大的器件尺寸减小沟道导通电阻以获得良好的ESD 防护能力。电源钳位ESD 结构如图3 所示,该电路主要由电阻R 及NMOS 构成的电容C 组成RC 耦合网络,该耦合网络及下一级P1 和N1 构成的反相器用于确定大驱动管N2 在ESD 应力下的打开时间,人体放电模型(HBM)ESD 持续时间为100~150 ns[8],电源上电通常在毫秒级,RC 延时通常设计为1 μs 左右。当VDD正常上电时,RC 延时远小于电源上电时间,反相器的输入结点可以被正常充电至VDD,反相器输出为VSS,大驱动管N2 处于截止状态。当正向ESD 应力出现在VDD上时,RC 延时明显大于ESD 脉冲的上升时间,电容C 通过电阻R 的充电速度变慢,反相器的输入电平增加,速度慢于VDD的上升速度,此时输入变为低电平,反相器的输出为高电平,在VDD与VSS之间形成低阻泄放通路,ESD 脉冲完成对电容C 充电后,反相器输入电平与VDD一致,此时大驱动管N2关闭,电路恢复正常工作状态。按照合理的RC 延时及较小的钳位电压设定设计各器件的具体尺寸,最终电源钳位的实际版图结构如图4 所示,图中标注了与图3 对应的各器件的具体位置。

图3 电源钳位ESD 结构

图4 电源钳位的实际版图结构

为保证电源钳位结构具有良好的ESD 性能,同时对电路正常工作状态不产生影响,分别对图4 所示结构的ESD 性能、上电过程是否产生大电流、电源噪声下是否存在误开启进行仿真确认。

3.1 ESD 性能仿真

HBM 等效仿真模型如图5 所示[9],该模型由100 pF 人体等效电容、1.5 kΩ 人体等效电阻、1.5 pF 等效寄生电容及7.5μH 等效寄生电感、电源钳位电路DUT组成。将ESD 电平分别设置为2 kV、3 kV、4 kV 进行仿真,仿真结果如图6 所示,对应的电源钳位结构大驱动管N2 的栅端峰值电压Vpeak分别为3.72 V、4.94 V、6.02 V,对应的开启时间均为750 ns 左右。峰值电压较3.3 V NMOS 管的栅端击穿电压仍有余量,大驱动管N2 开启时间也与设计预期值相符,电源钳位结构在HBM 等效仿真模型下具备良好的ESD 仿真性能。

图5 HBM 等效仿真模型

图6 ESD 性能仿真结果

3.2 电源钳位结构对电路性能的影响

为确认电路上电过程电源钳位结构是否会产生大的导通电流,将上电时间分别设置为10 μs、100 μs、500 μs 及1 ms,仿真结果如图7 所示,上电时间为10 μs 时电源到地的瞬间峰值电流Ipeak为1.2 mA,上电时间超过100 μs 后电源到地的瞬间峰值电流为纳安级,因此电源钳位结构不会对上电电流产生影响。

图7 上电过程中电流仿真结果

为确认电源噪声环境下电源钳位结构是否会误开启,仿真时给3.3 V 电源添加频率为100 MHz、正负摆幅分别为0.5 V、1.0 V、1.5 V 的正弦波噪声,对电源钳位大驱动管N2 的栅端电压的影响如图8 所示,即使电源出现±1.5 V 的噪声,大驱动管N2 的栅端电压峰值仅为132 mV,不会发生误开启的现象。

图8 电源噪声下大驱动管栅端电压仿真结果

4 ESD 防护网络设计与实测结果

全芯片ESD 防护网络如图9 所示,薄外延材料下寄生双极管难以打开,因此IO 端用于ESD 保护的PMOS 及NMOS 在此网络下只作为P+/Nwell、Pwell/N+等效二极管使用。PD、ND 分别为IO 对VDD的正负电压放电通路,PD 模式下泄放电流经IO 通过P+/Nwell等效二极管至VDD,ND 模式下泄放电流经VDD通过电源钳位及Pwell/N+等效二极管至IO;PS、NS 分别为IO 对VSS的正负电压放电通路,PS 模式下泄放电流经IO 通过P+/Nwell等效二极管及电源钳位至VSS,NS 模式下泄放电流经VSS通过Pwell/N+等效二极管至IO;PESD、NESD分别为VDD对VSS的正负电压放电通路,正向模式PESD下泄放电流经VDD通过电源钳位结构至VSS,负向模式NESD下泄放电流经VSS通过电源钳位结构的Pwell/N+等效二极管至VDD;IO 对IO的放电路径类似,均通过P+/Nwell、Pwell/N+两个等效二极管及电源钳位泄放电流。

图9 全芯片ESD 防护网络

根据对全芯片ESD 防护网络的分析,ESD 通路除了PD、NS、NESD3 个模式下通过单个等效二极管直接放电外,其他模式放电通路均需通过电源钳位及等效二极管,实际泄放通路较非外延下GGMOS 结构泄放通路更长,0.13 μm 及之前的CMOS 工艺ESD 泄放路径等效电阻要求在3 Ω 以内[10],本研究中ESD 泄放路径按照等效电阻不大于1.5 Ω 设计,同时在相邻端口间距满足尺寸要求的前提下,将电源钳位结构作为Filler 单元进行填充,以进一步降低ESD 泄放路径等效电阻。对3 只流片后的电路进行HBM ESD 摸底,测试结果如表1 所示,电路ESD 性能达到4 kV。根据GGMOS 结构及电源钳位结构的ESD 实测结果对比,采用电源钳位ESD 结构可有效提升电路在薄外延下的ESD 性能。

5 结论

本研究在采用薄外延片材料增强电路抗SEL 能力的条件下,使用GGMOS ESD 结构发现内部叉指结构的寄生三极管触发不均匀,ESD 性能衰减严重,采用电源钳位ESD 结构有效抑制了薄外延材料对ESD性能的影响,基于电源钳位结构优化了ESD 防护网络设计,仿真及实测结果表明,电路ESD 性能满足4 kV设计要求。