基于TSV 倒装焊与芯片叠层的高密度组装及封装技术

2022-08-31汤姝莉赵国良薛亚慧杨宇军

汤姝莉,赵国良,薛亚慧,袁 海,杨宇军

(西安微电子技术研究所,西安 710119)

1 引言

微系统融合了微电子、微机电、微光电技术,通过系统架构和算法将处理器、传感器、控制器等具有多种功能的集成电路、光电子器件、微机电系统(MEMS)及各类无源器件进行一体化、多功能集成[1-2]。系统级封装(SiP)采用高密度组装、先进封装技术将模拟、数字、射频等多个不同功能的半导体器件及无源元件集成至同一封装体内[3-5],以更小的体积实现整机系统功能,是提高电子器件集成度的有效手段,也是实现微系统的重要封装技术之一。宇航、武器等高端领域对电子产品的信息处理性能要求不断提高,同时对其小型化、轻质化、多功能化也提出了更高的要求,因此能够满足上述需求的SiP 及微系统技术具有在高可靠领域广泛应用的巨大潜力。

面对SiP 及微系统更高集成密度、更高性能、更高工作频率的发展方向,传统的组装及封装技术难以满足要求,这促进了如2.5D/3D 集成等先进封装技术的发展[6-7]。例如倒装焊技术,通过芯片表面的微凸点与基板或管壳进行互连,微凸点既能够作为机械支撑也可以实现电气互连,显著提高芯片单位面积输入/输出(I/O)数及组装密度[8]。作为立体互连及封装形式,硅通孔(TSV)被认为是“超越摩尔”最有前景的技术之一[6]。TSV 结合微凸点,能够在三维方向获得最大的堆叠密度及最小的外形尺寸,并且大大提升了芯片速度和低功耗性能,因此被视作是继引线键合、载带自动键合(TAB)和倒装芯片之后的第四代封装互连技术。除此之外,随着芯片减薄技术及高密度键合技术的不断发展,基于引线键合的裸芯片叠层技术能力持续提升,在基于TSV 的倒装焊芯片叠层基础上进一步提高了组装密度,成为实现高密度SiP、微系统的重要技术之一[9]。

后摩尔时代促使国际上的主流组装及封装技术由二维向三维方向发展。2011 年,美国Xilinx 公司与台积电合作,利用TSV 转接板技术推出了2.5D 封装的现场可编程逻辑门阵列(FPGA)产品,在国际上首次利用转接板技术实现了功能芯片的立体结构封装并成功应用于成熟产品。随后,IBM、Samsung、Tezzaron 等世界各大顶尖的半导体公司和研究所开发出了不同TSV 转接板的立体封装结构并实现微组装。同时美国国防部高级研究计划局(DARPA)设立项目研发了多功能芯片、多功能基板、立体组装及三维板间垂直互连等关键技术,成功实现了高密度、小型化微系统功能模块的三维立体集成。近年来,如长电科技、华天科技等国内领先的封装企业以及如中国电科各研究所和西安微电子技术研究所等国内科研院所,也陆续开发了2.5D/3D、SiP 技术和高性能倒装焊及引线互连技术,具备一定的高密度模块组装及封装能力。

然而随着信息处理及传输速度要求的不断提高,SiP、微系统模块的高功能密度集成带来了功率密度急剧增加的问题,因此保证内部器件尤其是倒装芯片的良好散热通道是模块结构设计的关键。单倒装焊芯片的非气密性散热封装已十分成熟并在高可靠领域得到应用。随着高性能、小型化的需求日益增加,新一代SiP、微系统为集成了多个功能器件的系统化模块,需同时将倒装芯片与其他片式元器件和键合互连的裸芯片共同集成在腔体内,因此需采用气密性封装保证键合的可靠性,传统的非气密性倒装焊封装方案无法满足要求。

本文针对微系统的高集成度、高功能密度需求及倒装焊芯片的散热问题,重点介绍了基于TSV 转接板的倒装焊立体组装、基于键合工艺的芯片叠层等高密度组装技术以及倒装焊芯片的双通道散热封装方法。结合两款高密度模块的组装及封装工艺实施过程,介绍了相关技术在高可靠、高性能SiP 及微系统领域的典型应用。

2 高密度集成关键技术

高密度集成关键技术包括高密度管壳和基板制造、高密度组装互连、封装和测试技术等多个环节,具体涉及封装堆叠、芯片堆叠、TSV、基板埋置等先进封装技术及引线键合、倒装芯片、微凸点等其他封装工艺[10]。本文重点对模块组装和封装的工艺技术进行了介绍,包括基于TSV 转接板的倒装焊立体组装技术及其过程控制、基于引线键合的裸芯片叠层技术等。

2.1 基于TSV 转接板的倒装焊立体组装技术

传统的倒装焊裸芯片封装直接在高温共烧陶瓷(HTCC)管壳或低温共烧陶瓷(LTCC)基板上进行焊接,但随着倒装芯片的I/O 规模急剧增加,凸点尺寸不断减小,模块内部集成度不断提升,直接采用陶瓷管壳或基板进行互连存在两方面问题:(1)集成电路之间需要大量的布线互连,陶瓷管壳或基板受其布线尺寸的限制,将极大增加封装尺寸,同时带来更大的寄生电阻和串扰,严重影响高速信号的传输;(2)随着大规模集成电路I/O 数的增加,倒装芯片凸点的特征尺寸进一步减小,陶瓷管壳或基板内部焊盘的对位精度及倒装焊区域的翘曲控制难度急剧增加,严重影响倒装焊的质量及可靠性。

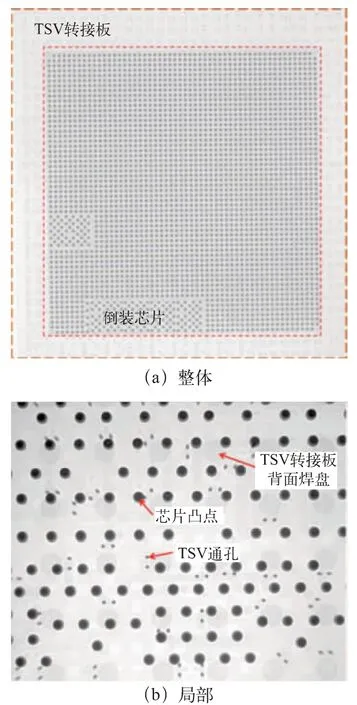

通过TSV 转接板进行倒装芯片的立体组装可有效改善上述问题。图1 中在倒装芯片与陶瓷基板或管壳之间增加了一层TSV 转接板,通过在TSV 转接板上布线将倒装芯片内部的电源、地分别进行合并引出,减少端口数量,从而可在硅基板另一面分布更大的凸点,实现“小球”转“大球”,降低在陶瓷管壳上的组装难度;此外,由于TSV 转接板采用垂直互连方式,其经过转接后尺寸增量很小,满足电子器件小型化的需求。

图1 基于TSV 转接板的倒装焊叠层组装结构

当模块内部集成多个倒装芯片时,采用TSV 转接板的优势将更加明显。首先,由于硅基板的线条特征尺寸通常为10~20 μm,远小于HTCC 的布线尺寸(50~70 μm),采用TSV 转接板集成多芯片时尺寸远小于直接集成在HTCC 管壳上的尺寸;其次,可根据功能需求将多个芯片集成在同一片TSV 转接板上,形成标准化的功能单元组件,从而在后续设计过程中灵活选用,并能够在组件级实现测试筛选,大幅降低设计及组装、测筛成本。

高密度SiP、微系统模块不同于传统的混合集成电路,其内部采用了如TSV、倒装焊、键合芯片堆叠等立体组装及先进封装工艺,且具有复杂的结构,因此需着重对上述先进组装及封装工艺进行过程质量检验及可靠性评估。倒装焊工艺质量过程控制涉及基于TSV 的倒装焊工艺可靠性评估、微凸点质量检测、倒装焊翘曲控制等方面。目前业内已针对单项工艺制订了相关文件,但暂未形成完整的标准体系。

倒装焊的工艺难点在于对位、焊球焊接、翘曲度、超细间隙清洗及底部填充等方面。针对以上难点,设计了芯片倒装焊工艺流程(如图2 所示),包括来料质量控制、倒装焊过程控制及焊后检测等关键工序。为了提高倒装焊接的成品率,制订了以下质量控制点:(1)对来料进行芯片凸点检验并利用台阶测试仪进行基板翘曲度及凸点共面性检测;(2)焊前对芯片及基板进行预处理,以提高焊接质量;(3)对位贴片后利用X光进行初步检测;(4)焊后清洗采用真空汽相工艺;(5)焊后进行X 光检测、焊点外部目检及剪切力抽测。由于助焊剂主要存在于芯片与基板/管壳的细微间隙内,为了提高清洗效果,采用真空汽相清洗工艺可对超细间隙内的助焊剂进行有效清洗[11],再利用X 光及通断测试对倒装焊质量进行检测(如图3 所示),并从批量倒装芯片中抽取数只进行剪切力测试。

图2 倒装焊工艺及过程质量控制流程

图3 倒装焊后X 光检测结果

2.2 基于键合工艺的芯片叠层技术

高密度集成的另一项关键技术是基于键合工艺的芯片叠层,将多个芯片在垂直方向上进行堆叠,并利用引线键合进行互连。常见的三维芯片叠层结构为金字塔型、十字交叉型及悬臂梁型[12]。金字塔型叠层芯片面积由下至上需依次减小,一般用于不同功能及尺寸芯片的堆叠,十字交叉型叠层芯片键合的引出端只能在芯片的两端,悬臂梁型更适用于堆叠尺寸及布线相同的芯片,如存储器等[12]。无论采用何种方式堆叠均存在散热性能相对较差的问题[13],因此功耗较大的芯片不宜采用该工艺。此外,随着堆叠层数的增加,堆叠成品率将急剧下降,任何一层芯片的失效将导致整个堆叠组件的失效,因此在堆叠器件的选用、堆叠层数的设计上应综合考虑,以达到最优设计。

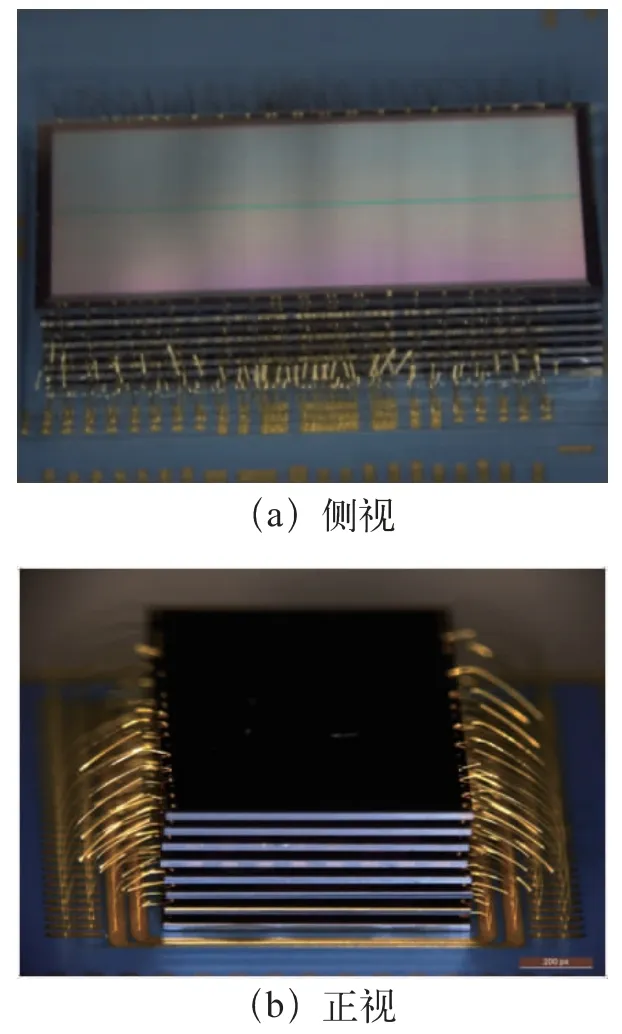

悬臂梁型叠层的基本结构为芯片-垫片-芯片的叠层结构。芯片叠层的工艺流程如图4 所示,各层芯片及垫片利用绝缘胶进行粘接,并依次进行芯片的键合。根据所需层数重复粘接及键合的工序,每次粘接及键合后分别进行目检,最后通过拉克试验对键合强度进行无损检测。为了减小堆叠芯片的整体高度,通常需对芯片及芯片间的垫片进行减薄。由于两层芯片的间隙为减薄后的垫片厚度,为了避免上层芯片压住下层键合丝,应对每一层芯片的键合丝引弧高度进行控制。因此采用低引弧高度的键合工艺来降低引弧高度,即在键合前先在芯片上预置金球,并将一焊点键合在基板上,二焊点键合在预置的金球上,利用此方式最低可达到70 μm 左右的弧高,满足减薄后垫片的叠层需求。已制作完成的悬臂梁型8 层堆叠芯片如图5 所示。

图4 芯片叠层工艺流程

图5 基于键合工艺的悬臂梁型8 层堆叠芯片

3 基于倒装焊的高效散热封装技术

为了解决倒装焊芯片的散热问题,设计了具有双散热通道的封装结构,即主散热通道为芯片背面通过导热胶、热沉连接至封装盖板,副散热通道为芯片凸点通过焊球、基板连接至封装衬底。

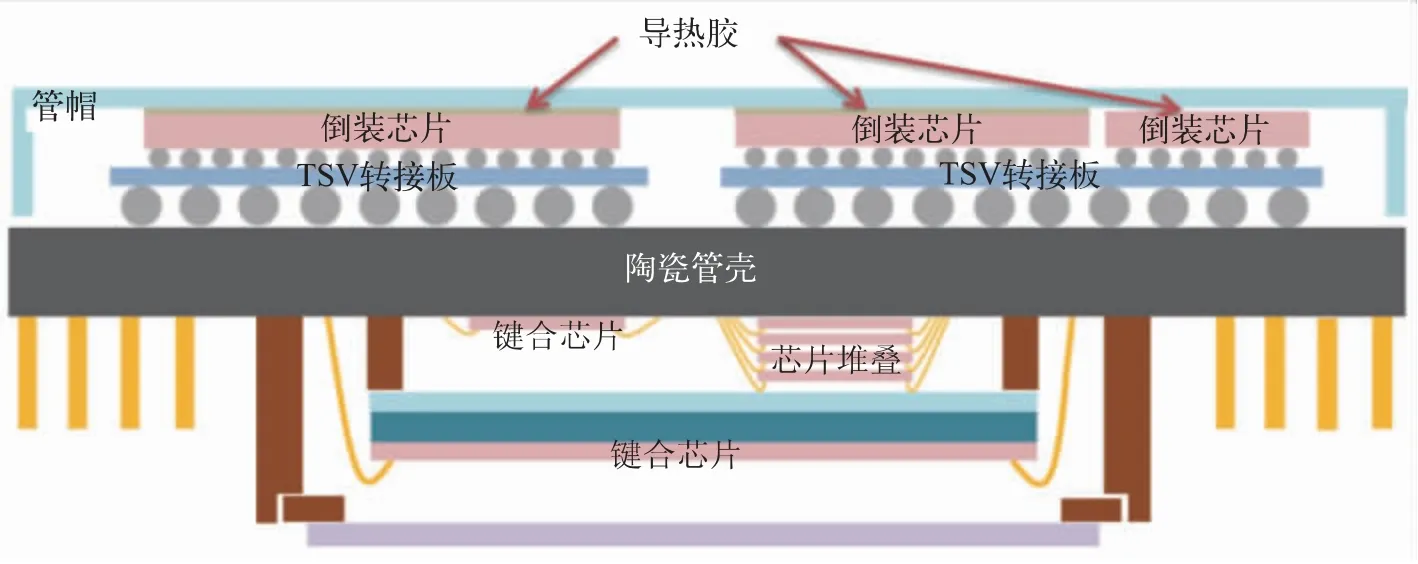

对于内部存在裸芯片及键合丝的模块,需要采用气密性封装方式保证其可靠性,此时双通道散热的核心是如何实现倒装芯片与封装盖板之间的良好热接触,同时保证模块在受到机械外力时应力不会完全施加至芯片上。图6 为一种典型的气密性高密度SiP 模块双散热通道封装结构,该结构通过在倒装芯片上增加不同厚度的热沉,并通过导热保证不同高度的芯片与盖板实现良好的接触,同时增加盖板厚度来提高刚度,抑制其形变。在工艺实现时,存在倒装焊芯片高度不一致的情况,可利用光学测高及粘接不同厚度的热沉进行高度补偿。

图6 气密性双散热通道封装结构

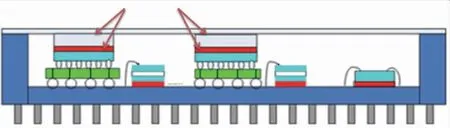

当模块集成度需求持续提高时,单面组装已无法满足更高的组装密度需求,因此利用双面立体封装结构来进一步增加集成度。图7 中将键合互连的裸芯片与基于TSV 转接板的倒装焊芯片分别置于模块的两个腔体。图7 中上腔体为非气密封装,倒装焊芯片/TSV 转接板组件组装完成后,在芯片表面涂抹导热胶后进行管帽的粘接,导热胶同时起到散热及粘接的作用。下腔体为气密性封装,为裸芯片键合工艺可靠性提供了保障。

图7 非气密性双通道散热封装结构

4 高密度组装及封装技术的典型应用

基于上述关键技术,实现了一款高可靠高性能信息处理SiP 模块的高密度组装及高效散热封装,其封装形式为陶瓷柱栅阵列(CCGA)气密性封装,内部包含处理器、FPGA、存储器等多款大规模集成电路以及薄膜电阻网络、表贴电容等其他元器件,完成组装的SiP模块如图8 所示。模块尺寸为43 mm×43 mm×5.65 mm,气密性可达5×10-9Pa·m3/s,其平面面积约为采用印制电路板(PCB)装配工艺实现相同功能的产品的1/10。

图8 高密度组装SiP 模块

模块制造过程为:(1)基于TSV 倒装焊叠层技术分别将处理器、FPGA 等倒装芯片与TSV 转接板互连,形成TSV 组件;(2)通过定制的测试夹具对组件进行测试,然后将测试合格的TSV 组件背面植球栅阵列(BGA)焊球后倒装焊接至HTCC 上;(3)利用基于引线键合的多层芯片堆叠技术组装存储器等叠层芯片,采用成熟的粘接、键合工艺组装其他电容、芯片等元器件;(4)通过导热胶及不同厚度的热沉使倒装焊芯片与盖板实现良好的接触;(5)利用激光熔封工艺对模块进行气密性封装。

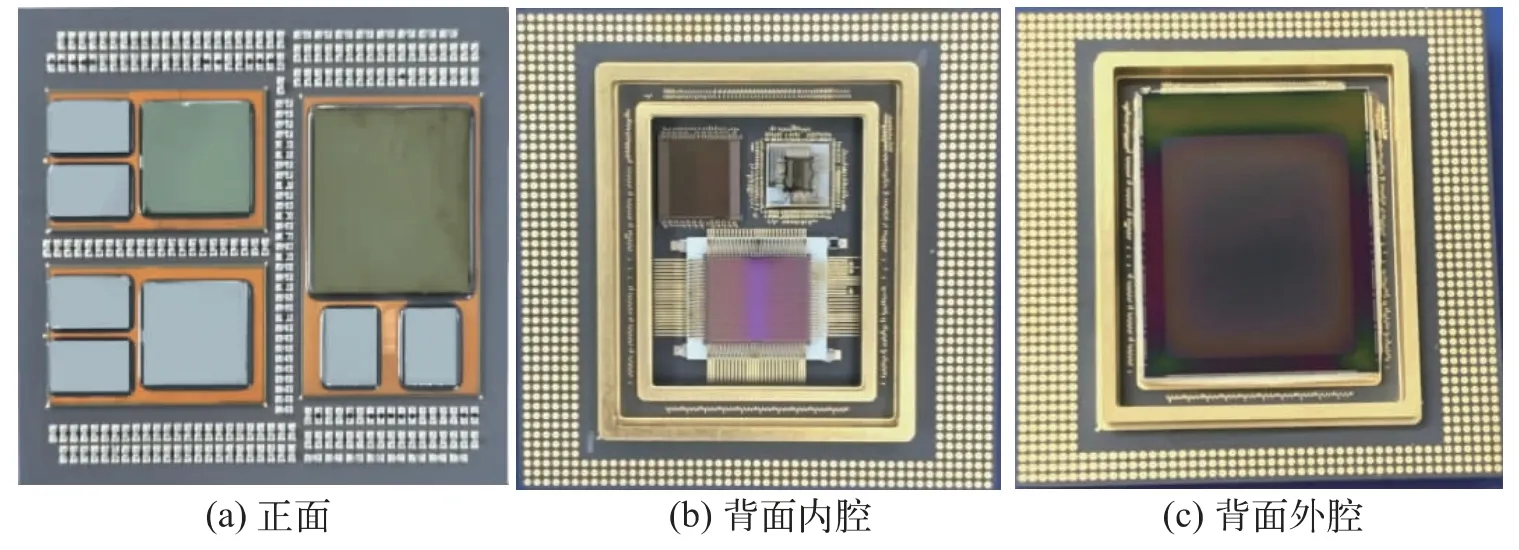

双面嵌套腔体封装结构的微系统模块如图9 所示,其正面为非气密性腔体,采用基于TSV 的多芯片倒装焊技术组装了处理器、FPGA、PowerPC 中央处理器等倒装芯片,同时还集成了200 余只表贴阻容器件;背面为两个嵌套气密性封装腔体,组装了所有的键合裸芯片,包括内腔的存储器、Flash 等芯片及外腔的CMOS 图像传感器(CIS)芯片,腔体的气密性可保证键合可靠性。

图9 双面嵌套多腔体微系统模块

模块制造过程为:(1)分别将倒装芯片与TSV 转接板互连形成多芯片组件,并进行测试、底部填充及背面植球;(2)将多芯片组件倒装焊接至HTCC 上并进行底部填充,同时利用回流焊工艺组装表贴阻容器件;(3)倒装芯片背面涂抹导热胶,与管帽进行接触散热,并通过管帽边缘用环氧树脂粘接的方式进行非气密性封装;(4)背面内腔利用基于引线键合的多层芯片堆叠技术组装裸芯片后,采用平行缝焊进行气密性封装;(5)在内腔盖板上粘接陶瓷垫片及CIS 芯片并完成键合;(6)同样利用平行缝焊进行外腔光窗盖板的气密性封装。双面三腔体模块结构可同时满足倒装芯片的散热及CIS 的采光需求。

5 结论

本文重点介绍了基于TSV 倒装焊、芯片叠层的高密度组装工艺与高效散热封装技术在高密度SiP、微系统领域的典型应用。利用基于TSV 转接板的倒装焊实现了多芯片的模组化立体集成,并通过来料质量检测、倒装焊接过程控制、焊后检测等关键工序提高了工艺成品率。此外,采用芯片、垫片减薄技术及低引弧高度键合工艺实现了芯片叠层,可显著提升组装密度。针对倒装芯片的散热问题,设计了具有双散热通道的封装结构。基于以上技术,实现了信息处理SiP 模块的高密度、气密性封装以及同时满足多倒装芯片散热与CIS 采光需求的双面三腔体微系统模块封装。