针对DSP 的系统级封装设计和应用

2022-08-31邢正伟陈康喜

邢正伟,许 聪,2,丁 震,陈康喜

(1.安徽芯纪元科技有限公司,合肥 230000;2.中国电子科技集团公司第三十八研究所,合肥 230000)

1 引言

系统级封装(SiP)狭义上是一种封装的概念,广义上是将一个系统或者子系统的全部或者大部分电子功能集成在同一个整合型基板上,该系统内的芯片以2D、3D 等方式接合到整合型基板上[1]。系统级封装集成度高,能够解决异质集成问题,目前在手机、5G 领域都得到广泛的应用[2]。目前国内针对数字信号处理器(DSP)的系统级封装的研究越来越广泛和深入,2016年,中国电子科技集团公司第五十八研究所采用SiP陶瓷封装技术将DSP 芯片和FPGA 芯片结合[3]形成微系统模块;2018 年,北京计算机技术及应用研究所研制出集成四核及1553B 总线控制器的SiP 封装电路[4];2019 年,上海航天控制技术研究所采用SiP 技术将DSP 芯片、存储芯片和FPGA 芯片制成多信息处理电路[5];2020 年,航空工业西安航空计算技术研究所提出处理器+FPGA 通用架构,满足最大化系统需求[6]。这些研究表明采用系统级封装可以有效减小系统尺寸和重量。

雷达是目前常见的探测侦察设备,其最基本的原理是射频前端发射调频电磁波,雷达系统将接收到的回波与发射波进行算法处理,可以得到目标的各种信息。雷达系统包含信号发射器、接收天线、信号处理器、信号传输系统和控制系统。为满足某款雷达系统小型化应用需求,本文利用系统级封装技术,将多片具有自主产权的高性能DSP 芯片[7]进行集成,形成雷达一体化通道处理模块,经过电性能分析、热分析和应用测试,讨论和分析了该模块的可行性。

2 封装设计

2.1 系统结构

雷达系统需要具备对数据进行高效处理和高速传输的能力,单颗DSP 芯片能力有限,需采用多片配合使用,以达到系统要求。系统模块包含4 片DSP 裸芯片与90 个电阻和电容器件,内部以DSP 4 作为主控芯片,采用星型拓扑结构,通过高速SerDes 接口对其他DSP 进行控制,协作4 片DSP 之间的数据处理和传输,外部预留高速SerDes 接口和低速接口,可以满足雷达系统的板级信号传输,其功能框图如图1 所示。

图1 模块功能框图

2.2 封装和布局设计

倒装焊技术(FC)是指将芯片面朝下、与封装外壳或布线基板直接互连的一种技术。本模块主要器件是4 片DSP 裸芯片,单个DSP 裸芯片尺寸为17.5 mm×8.6 mm,采用平铺方式进行布局,DSP 裸芯片均采用倒装焊技术进行组装,模块尺寸达到40 mm×40 mm。

2.3 封装基板设计

封装基板可为芯片提供电连接、保护、支撑、散热、组装等功能。积层法多层板(BUM)是能使封装基板实现高密度化的新型技术,采取涂布绝缘介质再经化学镀铜和电镀铜形成导线及连接孔,多次叠加,累积形成所需层数的多层印制板。该模块封装基板采用积层封装工艺,共10 层,从上至下依次为L1~L10;在材料选择上,采用味之素堆积膜(ABF)有机基板,基板材料型号为ABF-GZ41,其介电常数为3.2,优于PCB 基板材料FR4 的介电常数4.0,更适合于高速信号走线。各叠层的设计为:L2/L4/L7/L9 为关键信号走线层,L1/L3/L5/L8 为地层,信号与地间隔分布,使得信号绝大部分返回电流在信号路径下面流动,回路电感保持最小,有助于提升信号质量;L6/L9 为关键电源层,通过大面积铺铜保证低阻抗,减少电源振荡,同时有利于模块散热;L10 层为焊球层,用于安装焊盘。

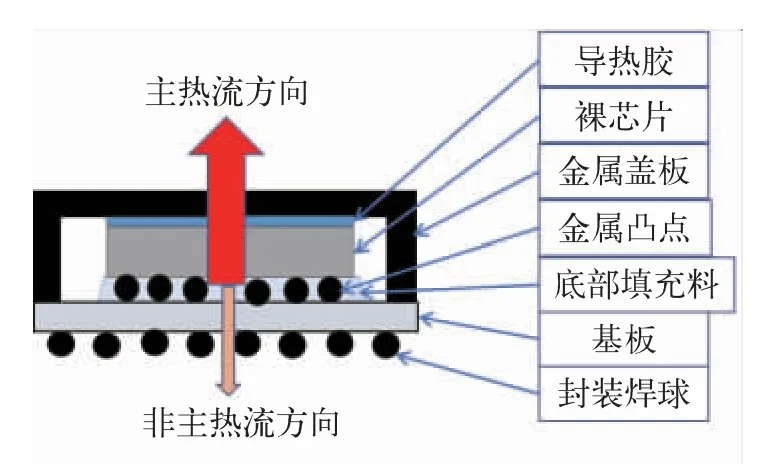

2.4 热设计

在模块内部狭小空间中平铺多个芯片会导致热量堆积,单位面积的热流密度大大提升,如果不能通过有效的方法进行散热,必然会导致芯片热可靠性出现问题。对于模块而言,需要建立散热通道将内部热量传导至外界,再通过空气对流等手段带走热量。该模块内部集成4 个DSP 裸芯片,散热需求高,散热结构如图2 所示,通过导热胶到金属盖板的主热流方向将热量传导至外界,以此满足芯片工作时的散热需求。

图2 模块散热结构

3 仿真分析与测试

3.1 电性能仿真分析

3.1.1 电源完整性分析

从电源完整性角度出发,电源平面等效于多个电感和电容构成的网络,在不同频率作用下,等效电容和等效电感会发生谐振现象,导致电源层的阻抗发生变化。随着频率的增加,电源阻抗是不断变化的,尤其是在并联谐振效应显著的时候,电源阻抗也随之明显增加,进而造成电源的不稳定。该模块通过电源系统的平面阻抗在工作频率范围内有无明显谐振(电源的主要能量谱集中在30 MHz 以下)来判定电源系统的好坏。模块内部电源阻抗曲线如图3 所示,不同颜色代表不同的电源平面,该模块电源系统平面阻抗在工作频率范围内(小于30 MHz)无明显谐振,说明电源系统的结构满足设计要求。

图3 模块内部电源阻抗曲线

3.1.2 信号完整性-损耗分析

信号完整性的重点是通过链路设计及优化使得电压或电流具有完美波形及质量,通常高速互连是信号不完整的根源。本模块内DSP 之间采用并串/串并转换(SerDes)来实现高速数据传输,SerDes 关注的频率范围是0 Hz 到奈奎斯特频率,也就是2 倍的信号基频。信号的基频是信号线速率的一半,也就是说信号的奈奎斯特频率就是线速率。链路对信号的损耗包括插入损耗、回波损耗等,可以通过S 参数模型来表达。本模块内DSP 之间传输速率为5 Gbit·s-1,根据SerDes信号完整性要求,回波损耗SDD11 小于等于-14dB@5GHz,插入损耗SDD21 大于等于-3dB@5GHz,再利用S 参数仿真高速链路眼图进一步分析信号质量。

本文针对系统级封装,利用4 片DSP 芯片搭建相同功能的测试板,用于封装前功能验证,以下将针对两者进行对比分析。

本文采用Sigrity 软件提取S 参数,高速差分信号封装前后的S 参数曲线对比如图4 所示,从图中可以看出,封装前(板级)SDD11 大于-14 dB@5 GHz,SDD21 小于-3 dB@5 GHz,曲线谐振大,表明封装前高速链路阻抗匹配差,反射严重;封装后(模块)SDD11小于等于-14 dB@5 GHz,SDD21 大于等于-3 dB@5 GHz,曲线连续、波动小,表明封装后高速链路信号质量更好。

图4 封装前后S 参数曲线对比

3.1.3 信号完整性-眼图分析

数字信号的眼图中包含了丰富的信息,可以体现数字信号的整体特征,能够很好地评估数字信号的质量,因而眼图分析是数字系统信号完整性分析的关键之一。根据RaPidIOTM Interconnect Specification Rev 2.2 协议制定的SerDes 眼图标准如图5 所示,眼宽参数RX1=0.3 UI(Unit Interval),眼高参数RY1=62.5 mV,RY2=375 mV,误码率(BER)要求为10-12。

图5 眼图标准

利用Sigrity 软件搭建高速链路模型,封装前链路如图6(a)所示,两个DSP 之间的通信链路模型为裸芯片→芯片封装1→PCB 链路→芯片封装2→裸芯片,导入封装前链路的S 参数,得到图6(b)中的链路眼图。从图中可以看出,封装前链路的眼高为140 mV,眼宽为0.59 UI,满足眼图标准,同时实际测试结果与之相符合。

图6 封装前后键路模型及仿真眼图和实测眼图

封装后链路如图6(c)所示,两个DSP 在封装内部的通信链路模型为裸芯片→基板链路→裸芯片,导入封装后链路的S 参数,得到图6(d)中的链路眼图。从图中可以看出,封装后链路的眼高为314 mV,眼宽为0.68 UI,满足眼图标准,同时实际测试结果与之相符合。

对比封装前后数据,可以清晰地看出,封装后眼图更高更宽,具有更好的信号质量。

3.2 热性能仿真分析

封装的热性能仿真分析是封装设计一个重要内容,因为封装大小、使用材料、散热措施与芯片最终能否正常工作、可靠性如何息息相关[9]。

本文采用Sigrity 软件模拟芯片实际工作的环境,在标准6U VPX 板卡(160 mm×233 mm)上安装3 片该模块,边缘放置电源芯片;热沉按照整板进行设计,散热器高度为10 mm(含翅片),风冷条件为风速3 m/s,环境温度为30 ℃。单个模块实际功耗按照25 W 进行估算,板卡上模块温度仿真结果如图7(a)所示,板卡上模块最高结温约为55.8 ℃。无任何散热措施下,模块温度如图7(b)所示,结温高达122.8 ℃。仿真结果表明,封装整体在添加散热器和风扇的情况下温度可控。

图7 模块封装热仿真结果

3.3 试验测试分析

在模块设计完成后,经过封装厂和基板厂加工,采用自主开发的软件和硬件测试平台,对生产的产品进行测试分析,依据GJB7705-2012《DSP 测试方法》,采取周期法测定DSP 核的频率f,如式(1)所示,其中t 为脉冲持续时间,N 为该持续时间内的指令数。

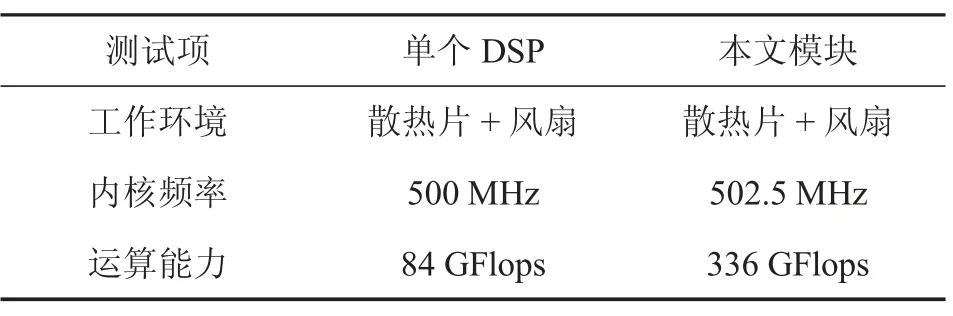

根据GJB7705,运行一个完成N1个操作的汇编程序,通过测量该汇编程序的运行时间t1,计算出DSP的峰值运算能力flop,如式(2)所示:

依据上述测试原理,编写不同的测试程序,N 和N1对应固定的值,t 和t1通过示波器测量计算可得,模块所测数据如图8 所示,代入式(1)~(2)可得内核频率为502.5 MHz,峰值运算能力为336 GFlops,与单个DSP 各项功能对比见表1,对比发现经过系统级封装后模块功能测试正常。

图8 模块测试数据

表1 电性能测试

4 实际应用

某型号雷达信号处理板使用系统级封装前后的实物如图9 所示,图9(a)为未选用系统级封装模块的板子,尺寸为175 mm×455 mm;图9(b)为使用系统级封装模块且优化系统架构之后的信号处理板,尺寸为350 mm×55 mm,对比可见信号处理板的尺寸缩减到原来的24%,满足了用户对处理板轻质化、小型化、系统化的要求[10]。

图9 信号处理板使用系统级封装前后实物

5 结束语

本文针对雷达信号处理系统应用场景,将4 片DSP 芯片通过系统级封装方式形成模块,该模块内部布线满足信号和电源完整性要求,热分析结果表明该模块在添加散热器和风扇的情况下可以正常工作,经功能测试验证,各项功能均能达到要求。某雷达处理系统采用该模块后应用板卡尺寸缩减到原尺寸的24%,同时通过实际测试该模块可以完成对应信息采集处理和传递的功能,使得该雷达系统国产化具有可行性。