基于FPGA 的自动测试设备信号延时误差测量

2022-08-31季振凯

季振凯,吴 镇

(无锡中微亿芯有限公司,江苏无锡 214072)

1 引言

自动测试设备(ATE)是一种集成多种测试功能,由电脑控制对待测芯片的功能与电特性进行测试的自动化设备。在芯片的封装测试领域,ATE 能根据操作人员的需求对封装芯片进行甄别,大大降低芯片的测试时间。ATE 可大致分为设备控制模块、物理操作模块和电气测试模块3 个部分。设备控制模块通常是一台集成在机器内部的PC 机,负责将操作员的指令转化为不同模块的调度指令,并将模块的运行数据和结果反馈给操作员。物理操作模块负责芯片在机台上的移动、固定以及芯片测试温度控制等。电气测试模块是设备中最关键的部分,负责对芯片的功能进行测试。测试项目一般可分为直流测试、交流测试与功能测试3 种,通过对待测芯片输出激励,采集待测芯片的反馈来测试芯片功能的好坏。在一个测试项中,通常需要对芯片的不同引脚同时发出激励,激励信号经过传输通道到达待测芯片时会形成一定延时,而不同通道间形成的延时不尽相同,因此会造成信号间的不同步,形成“竞争-冒险”现象,待测芯片反馈的输出信号亦有此问题。这种信号不同步而产生的测量错误概率将随着激励信号频率的提高而大幅度提升。因此,在ATE 的使用过程中,对设备激励源至待测器件(DUT)间所有信号通道的信号延时进行测量是十分必要的。本文提出一种基于FPGA 的ATE 信号延时测量方法,在测量信号延时量的同时利用FPGA 的特性,可以在一定范围内根据需求调整测量精度。

2 信号延时分析

在理想状态下,高速数字系统中的信号源点与信号终点应严格按照时序要求进行数据的发送与接收[1]。当传输信号的时序关系变差时,系统产生问题的概率随之变大。在印制电路板(PCB)传输系统中,造成信号发生时序问题的主要因素有信号延时、信号反射、信号串扰以及信号振铃等几种[2]。本文主要针对信号延时对高速信号系统的影响进行研究。

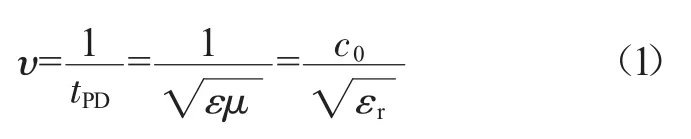

当系统中信号发生延时,且没有足够的时间实现稳定时,系统容易在运行过程中变得不稳定[3],这一问题在高速信号系统中尤为突出。通常将电信号通过整个传输路径所需的时间称为时延(TD),将电信号通过单位长度路径所需的时间称为传输延时(PD,tPD)。电信号在传输路径中的传输速度为:

式中c0为电信号在真空中的传播速度,可视为光速3×105km/s;ε 为介电常数;μ 为磁导率;εr为传输路径中传播介质的相对介电常数。常见PCB 材质及其参数如表1 所示,表中δ 为介质损耗角。市面上的电路板板材的介电常数在3.8~4.8 之间。若以4 进行简单计算,代入式(1)可以计算得知信号传播速度约为c0/2,通过单位换算可得约15 cm/ns 的经验值。

表1 常见PCB 材质及其参数

在多层电路板设计中,传输线可以根据走线的位置分为仅有一个参考平面的微带线与嵌入式微带线、有上下两个参考平面的对称带状线与不对称带状线。整体而言,微带线的介电常数较低且信号传输速率快,带状线的介电常数较高且信号传输慢[4]。多层电路板中的通孔将会对时延产生明显的影响,文献[4]的研究表明,通孔越长、通孔孔径越小,电信号的传输速率越低。通常一个标准通孔会造成24 ps 左右的延时[5-7]。因此在时序严格的高速信号传输系统中,仅通过走线长度不足以正确计算信号传输延时。

3 测试系统

3.1 信号传输系统结构

目前国内外主流的传输延时测量方法主要有两种,第一种是使用高精度采样仪器,以等长度探头同时采样信号源点与信号终点两处信号。在同一时钟下,两处信号会呈现出先后关系,而两处信号的间隔时间就是信号在两点间的传输延时。该方法虽精度较高,但需要外部高精度仪器辅助,且对于集成度较高的设备而言,外部探针无法接入理想检测点是十分常见的问题。第二种方法则是利用时域反射技术(TDR)计算出路径延时,TDR 利用的是信号传输路径上特征阻抗不连续时将会产生反射这一特性。通过目标反射的形态特性,计算信号在路径上的传输时间,从而达到计算延时的方法。目前主流NI、Advabtest 公司的ATE 均采用该方法。该方法需要在数据通道上连接至少一个模拟开关,用于切换TDR 通道与测试通道。传统TDR 的结果需要使用高速高精度的模数转换器(ADC)对其形成的信号进行采集,用于延时计算,由于高速高精度ADC 成本较高,常见ATE 通常使用1 个或几个ADC通过模拟开关在不同通道间进行切换,测试所需时间较长。

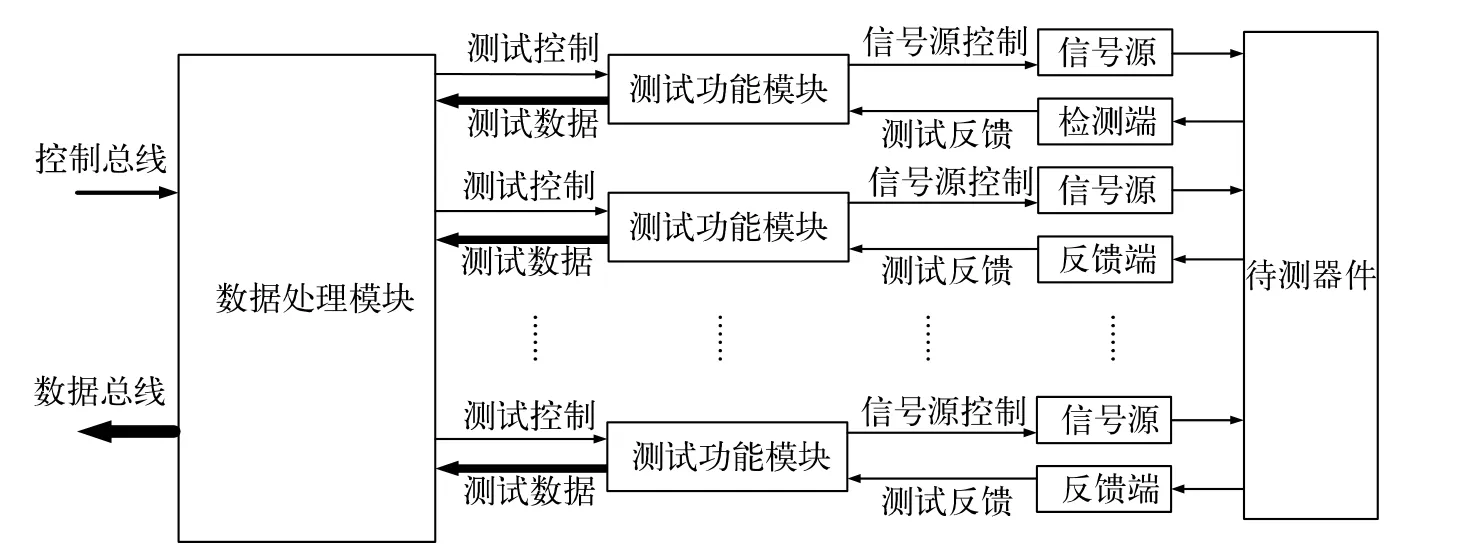

将本文提出的信号传输误差测量系统应用在国产ATE 上,设备产生的激励信号频率小于200 MHz,传输系统结构如图1 所示。

图1 本文提出的ATE 信号传输系统结构

本文所提出的方法将用于测量从FPGA 端对激励信号源发出控制信号到FPGA 接收到检测端反馈信号的时间差,作为传输路径的延时测量值。为了减少误差,在该系统中要求FPGA 至激励源和检测端至FPGA 的走线同层、严格等长且尽可能短。

3.2 测试系统

测试系统利用TDR 的基本原理,使用ATE 中的高速比较器代替高速高精度ADC 对反馈信号进行检测,相较于TDR 设备的测试方法,节约了高速高精度ADC 的成本,且可以实现多通道同时检测,节省了测试准备时间。根据信号反射原理,反射系数ρ 为:

式中R 为输入阻抗,Z 为传输线阻抗。当负载端为开路时,可以推算出:

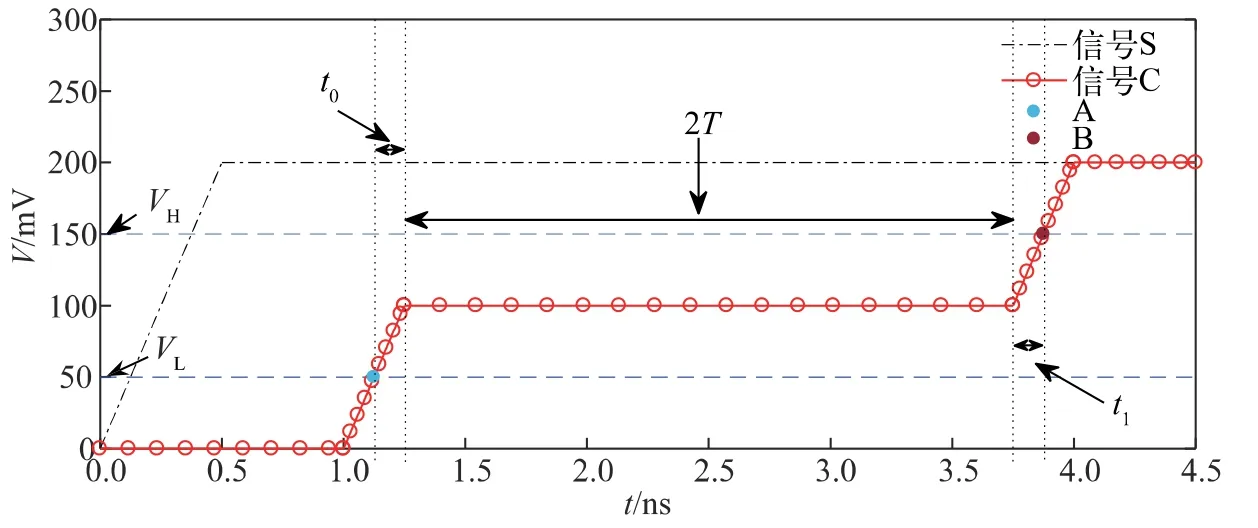

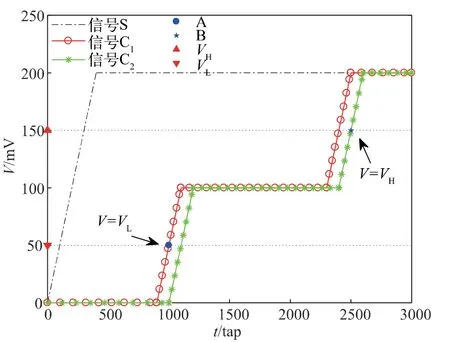

由式(3)可知,当负载开路电阻无穷大时,反射系数为1,反射波与入射波大小相等,相位相同。本文提出的测试系统使用比较器进行不同路径的延时误差计算,TDR 波形如图2 所示。根据文献[8]中所述,图2中T 可近似为信号源至开路点,即芯片引脚接触点的信号传输时间[9]。信号S 是信号源输出的激励信号,信号C 是接收的检测端反馈信号,VH、VL为2 个观测点电压,在不同路径中时长t0、t1一致。A 和B 点为以VL和VH为阈值时检测的有效点。因此,测量A、B 2 个观测点的时间差就能计算出不同路径中的传输时间差。

图2 TDR 波形

3.3 误差分析

本文采用FPGA 对信号源的输出与检测端反馈信号进行控制与采样,使用FPGA 对不同路径的A、B 2 点间信号的传输时间进行测量,并计算出不同路径下信号传输时间差,FPGA 内部程序结构如图3 所示。

图3 程序结构

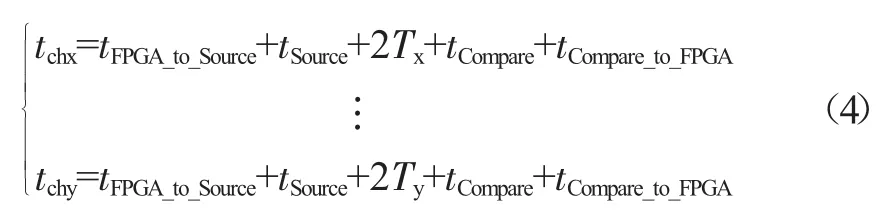

根据图1、3 可得该系统测量结果中的各个分量为

式中tchx表示通道x 的测量结果,tFPGA_to_Source表示FPGA信号至信号发生源的传递时间,tSource表示信号发生源的传递延时,tCompare表示检测端传递延时,tCompare_to_FPGA表示检测端至FPGA 的传递时间,Tx代表从信号发生源至检测端的信号传递时间。下标含y 的各变量定义可参照前面的定义。

不同路径中采用同一规格的激励源与检测端,且输入、输出信号类型一致,因此可以认为激励源与检测端响应时间一致。根据上文的要求,保证每一路径中tFPGA_to_Source与tCompare_to_FPGA各自相等。因此,通过对2 个路径间的测量结果求差,可以获得2 倍延时差值。将延时较短路径的信号进行延时补偿,则可以使不同路径的测试信号同时到达待测器件,完成误差补偿。

4 实验结果

4.1 实验步骤与方法

本文采用FPGA 中IOdelay 与时钟计数相结合的方式进行延迟时间测量,使用计数器的计数值作为时间的粗有效值,使用IOdelay 的设置值作为细有效值。IOdelay 模块位于FPGA 的I/O 模块中,拥有一定数量tap 的环绕延迟单元,可以根据编程输入对输入信号进行延时,延时精度取决于tap 的分辨率。本文采用Xilinx 的Kintex UltraScale 系列KU060 芯片进行计算处理。该芯片搭载IOdelay3 模块,固定延时为0.200 ns,tap 分 辨 率 为0.005 ns,tap 级 数 为512 个,在VAR_LOAD 模式下单一模块可以完成最大2.76 ns 的延时,模块的固定延时不影响信号的同步性。

使用IOdelay 模块将计时时钟分割为若干个区域,并使用IOdelay 的DEKAY_VALUE 与计时时钟计数值来描述测量结果。为保证在不同情况下测量结果的连续性,IOdelay 产生信号延时的最大值需要大于计时时钟周期。具体方法如下:

1)将IOdelay 的DELAY_VALUE 设置为0,发出激励信号的同时使用计时时钟开始计数,当VL检测端信号有效时,记录下当时的计数器数值做VL的粗有效时间,执行下一步;

2)按一定步进step 增大DELAY_VALUE 设置值,发出激励信号并使用计时时钟开始计数,当VL检测端信号有效时,记录下当时的计数器数值,执行下一步;

3)比较2 次记录结果,若第2 步的计数器数值大于第1 步的计数器数值,执行下一步,否则执行第2步;

4)减小step 值,得到step2,以step2 为步进减小DELAY_VALUE 设置值,发出激励信号,并使用计时时钟开始计数,当VL检测端信号有效时,记录下当时的计数器数值,执行下一步;

5)比较2 次记录结果,若第4 步的计时数值小于第3 步的计数器数值,执行下一步,否则执行第4 步;

6)进一步减小步进,重复第2~5 步,直到步进为1个tap 且DELAY_VALUE 设置为临界值时,将该DELAY_VALUE 值作为VL点的细有效时间,则该点的精确时间为[(粗有效时间+1)×计数时钟周期-(细有效时间×单个tap 延时)];

7)重复上述步骤,获得所有通道VL、VH点的有效时间;

8)用同一路径的VH时间减去VL时间,获得该路径的测量延时;

9)将不同路径下的延时数据进行排序,用最大延时值分别减去其余路径延时值,求得不同路径与最大延时路径延时的差值;

10)补偿延时短的路径,使得不同路径上的信号至DUT 时同步,本文中采用IOserdes+IOdelay 的方法进行补偿。

实验信号波形如图4 所示。图4(a)为步骤1 首次检测的波形图,图4(b)为以step 为步进向实际检测有效点靠近的情况,图4(c)为检测有效点低于实际有效点,按步骤4 缩小步进为step2 的情况,图4(d)为调转求解方向,向实际有效点靠近的情况。

图4 实验信号波形

最终检测波形如图5 所示。信号C1表示低检测点的最终波形,当达到该波形时,记录下此时的DELAY_VALUE 设置值。信号C2表示高检测点的最终波形,当达到该波形时,记录下此时的DELAY_VALUE 设置值。

图5 最终检测波形

4.2 实验条件与结果

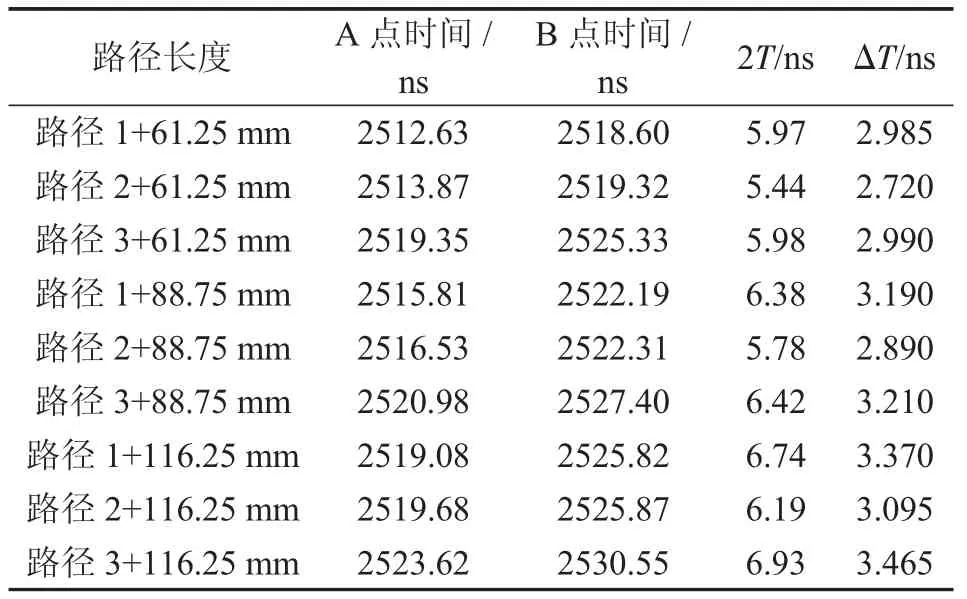

本文使用的FPGA 芯片为Kintex UltraScale 系列KU060 芯片。将Idelay 与Odelay 结合使用,可以形成5.52 ns 的最大延时,延时可调范围为0.400~5.52 ns。使用200 MHz 时钟作为计时时钟,用IOdelay 将每个周期时钟分隔为500 个区域,每个区域宽度为0.01 ns。激励信号为幅度1.2 V、频率200 kHz 的方波信号。检测端高阈值设为0.75 V,低阈值设为0.45 V。实验中使用标准走线板对不同路径信号进行标准长度延长,模拟不同长度路径对信号的影响,测量结果如表2 所示。

表2 不同路径测量结果

使用示波器检测来测试该系统准确性。检测示波器使用2 支同一规格探针,1 支连接激励源输出端,1支连接该路径对应的DUT 连接端。以激励源输出端的探针作为触发信号,抓取激励信号,比较两个信号间的时间差,即是传输延时,示波器检测结果如表3所示。

表3 不同路径示波器检测结果

经过多次对比示波器检测结果与该系统检测结果,发现两者测量结果差异范围小于0.2 ns,满足测试系统所需精度要求(小于200 MHz)[10-12]。

5 结论

本文提出的方法在国产ATE 中可以很好地完成路径延时差异检测工作,经多次测试发现,该系统测试结果的正确性与激励源和检测端的精度及稳定性息息相关。在实验过程中,为避免走线中其他阻抗非连续点带来的影响,需要在保证信号上升时间一致的前提下,尽可能加大激励信号幅度,减少非目标反射对检测结果的影响。