高速连接器插入损耗的影响因素

2022-08-31代秀云

刘 明,代秀云,何 洪

(四川华丰科技股份有限公司,四川绵阳,621000)

1 引言

在高速连接器传输链路中,以最常用的传输线为例,插入损耗(InsertionLoss)通常定义为输出端口所接受到的功率PI与输入端口的源功率Pi之比,常用dB表示。插入损耗通常是由于电路的失配引起,但电路设计时要达到理想状态下的匹配几乎是不可能的。在实际的电路中有很多方面的因素造成电路产生损耗,如电路设计及匹配,使用电路材料的损耗和加工等。对于微带传输线电路,插入损耗主要包括介质损耗、导体损耗、辐射损耗等几个部分,是各种损耗成分的总和。其中,介质损耗是指电场通过介质时,由于介质分子交替极化和晶格不断碰撞而产生的热损耗;导体损耗是由于导体不理想,存在损耗电阻,在电流通过时发热而引起的损耗;其主要影响因素是导体的电阻、电流分布(趋肤效应)和导体的表面粗糙度;辐射损耗是微带线场结构的半开放性所导致的电磁波辐射损耗。而在高速连接器结构中,对插入损耗影响比较大的因素包括传输线阻抗一致性、传输线表面镀层、传输线表面粗糙度等环节,降低这些因素对信号插入损耗的影响,对提高传输链路插入损耗有明显效果。

2 特性阻抗一致性对插入损耗的影响

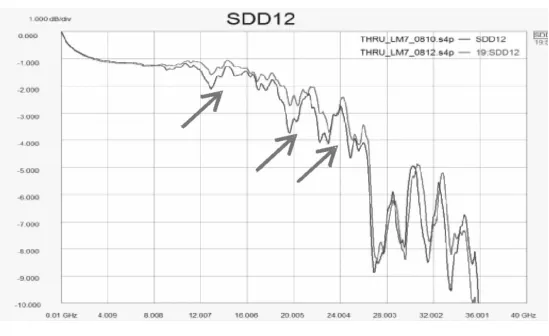

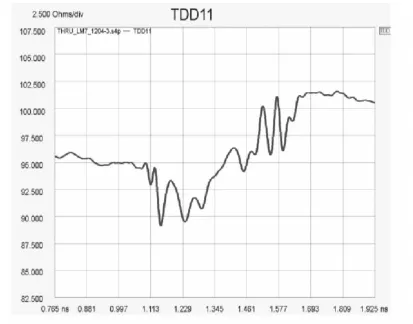

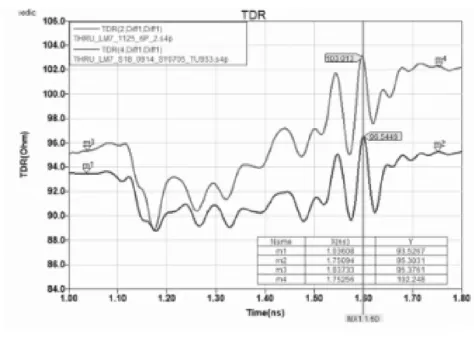

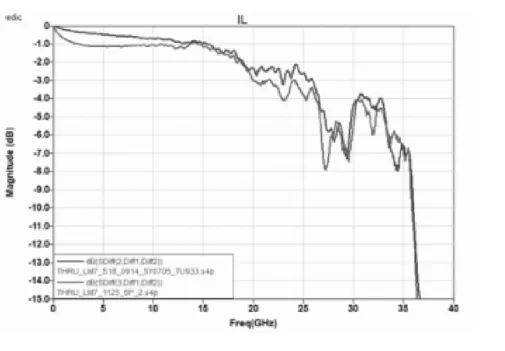

特性阻抗的定义为均匀传输线上各点的电压与电流的比值,它是解决信号完整性问题的核心。任何的阻抗突变都会引起信号的反射和失真,这会导致信号质量出现问题。高速连接器一般是弯母、直公配插使用,完成“连通”功能,传输差分信号的金属走线通过高分子材料注塑局部固定,屏蔽件、尾卡等零件通过热铆、过盈等方式组装成弯母或者直公,所以差分信号在连接器结构中的传输介质有空气,也有高分子材料;同时,高速连接器的弯母和直公对插位置为保证产品使用寿命,会设计弹性机构;高速连接器的这些结构特征决定了高速信号传输在连接器这一段传输路径必定存在阻抗变化,产品方案设计时,仿真模型设计尺寸通过信号完整性仿真尽量保证走线段阻抗波动不超过2欧姆,可由于零件加工公差、组装公差等会使设计尺寸会在公差范围变化,导致产品实际测试值和仿真设计值往往会出现偏差;而特性阻抗在某些特定频点的小幅变化(见图1),则会导致插入损耗出现红色箭头指向的谐振点(见图2),这些在高速背板连接器观测频段(20GHz)出现的谐振点是不可接受的。

图1 实测阻抗

图2 实测插入损耗

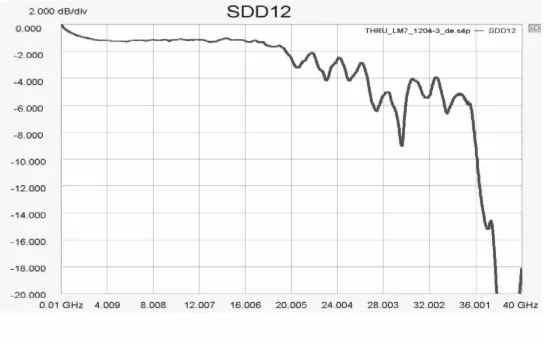

对该高速连接器走线段阻抗优化设计,走线段特性阻抗实测测试值变化范围控制在3欧姆以内,插入损耗得到明显改善,优化后的特性阻抗和插入损耗实测曲线见图3、图4,图4插入损耗测试图形可看出观测频段(20GHz)的谐振点均已消除;良好的阻抗一致性对控制插入损耗效果显著。

图3 改善后实测阻抗

图4 改善后实测插入损耗

3 传输线表面镀层对插入损耗的影响

3.1 趋肤效应

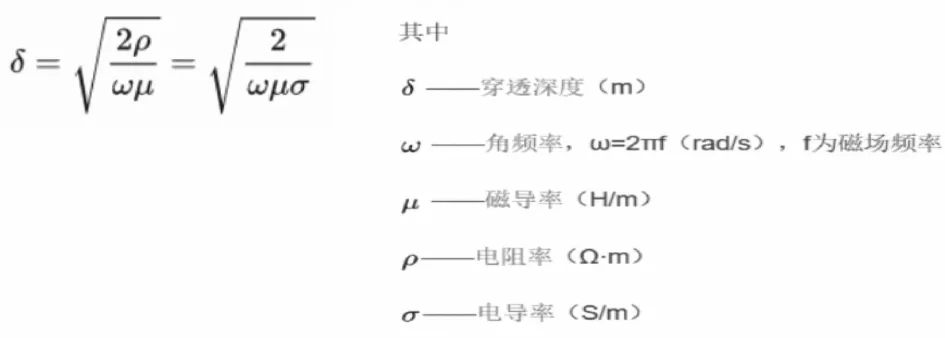

当导体中有交流电或者交变电磁场时,导体内部的电流分布不均匀,电流集中在导体的“皮肤”部分,也就是说电流集中在导体外表的薄层,越靠近导体表面,电流密度越大,导体内部实际上电流较小。结果使导体的电阻增加,使它的损耗功率也增加,这一现象称为趋肤效应。从电磁场的角度理解趋肤效应颇费周折,而从阻抗的角度分析,会让你豁然开朗;趋肤效应可以认为是电流寻求最低阻抗路径的趋势造成的。在高频时,路径阻抗主要由回路电感决定,为寻找回路电感最低路径,电流在导线上的分布会尽量伸展开以减少导线自感。同时,返回路径中的反向电流会尽量靠近信号路径表面以减少回路电感。趋肤效应导致电流分布于导体表面的厚度称为趋肤深度δ(skindepth),计算公式如下:

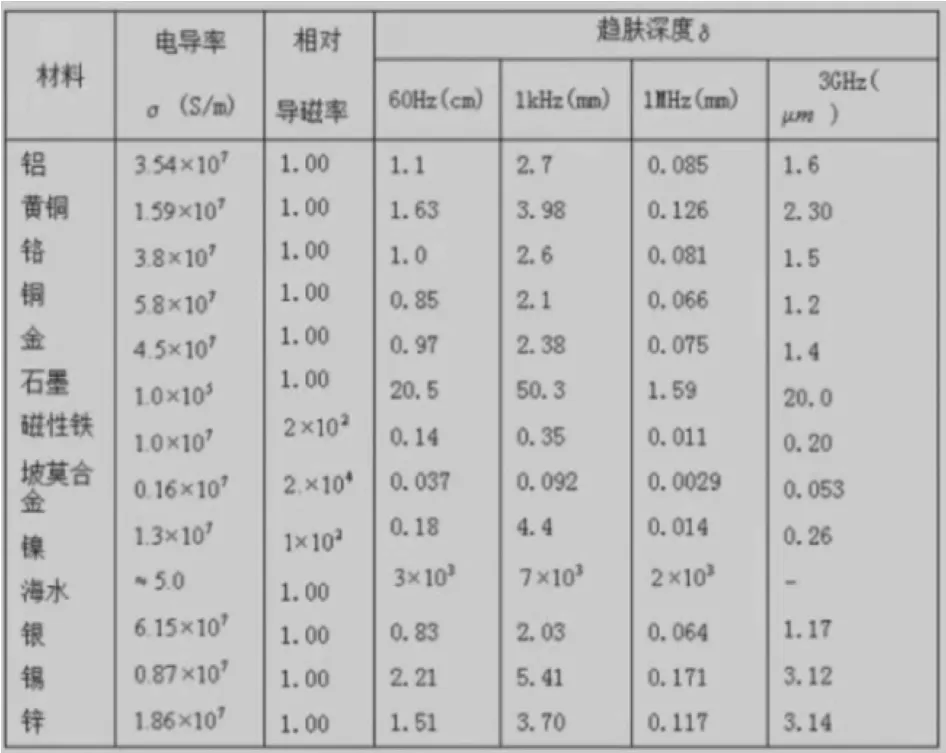

不同金属材料具有不同的磁导率、电阻率和电导率,所以不同金属材料的趋肤深度并不相同,数值见图5。

图5 不同金属的趋肤深度δ

图6对比可知,针对同一金属类型表层,随着频率升高,其趋肤深度也会发生变化,整体趋势是随着频率升高,其趋肤深度逐渐减小。

图6 铜在20℃时不同频率下的趋肤深度表

3.2 不同传输线镀层对插入损耗的影响

针对高速连接器,为提高其在应用场景的耐环境性,需要在铜合金冲压加工的金属传输线外表面增加电镀层,电镀层多选用镍、锡或者金等耐腐蚀性较强的金属,“鱼眼”压接区域金属表面一般电镀锡,簧片和插针接触区域金属表面则电镀金,其余走线区域考虑到产品成本金属表面一般电镀镍。当高速连接器运用在传输速率到20Gbps以上的传输环境中时,发现特性阻抗会出现奇怪的“上漂”现象(见图7),而插入损耗在低频段会出现明显的“鱼肚子”形状掉落(见图8),红色曲线为表面电镀镍走线测试曲线,蓝色曲线为表面不电镀走线的测试曲线。

图7 阻抗“上漂”现象

图8 插入损耗“鱼肚子”掉落

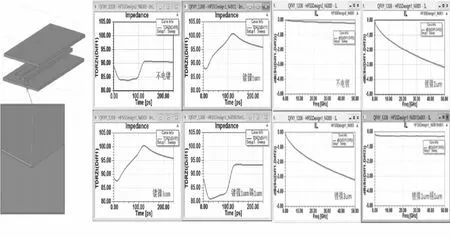

对比图5金属的趋肤深度可发现,金属镍的趋肤深度为0.26um@3GHz,金属铜的趋肤深度则为1.2um@3GHz。对比未电镀的信号走线,即为走线表面为铜,信号走线电镀金属镍的后趋肤深度明显变小,导致传输路径阻抗升高,信号的插入损耗也随之加大。按照该理论建立走线仿真模型,不同金属镀层特性阻抗和插入损耗对比见图9。

图9 不同镀层阻抗和插入损耗仿真对比

仿真结果对比来看,走线镀锡仿真结果特性阻抗不会出现“漂高”现象,同时,插入损耗和走线不电镀比较接近,但金属锡材料本身比较软,在高速连接器零件生产过程中,容易出现金属丝、金属屑,导致连接器出现性能不良,对零件生产制程要求较高。而走线镀镍的仿真结果中特性阻抗则出现明显的“漂高”现象,并且不会随镀镍层的厚度增加消失。

针对趋肤效应带来的插入损耗恶化,在制程金属丝、金属屑可控的前提下可考虑选用趋肤深度较大的金属,例如电镀锡。当然,除了常规的镀层金属,还可以考虑一些新镀层的使用,比如电镀铟、电镀石墨烯等。

4 传输线表面粗糙度对粗糙度的影响

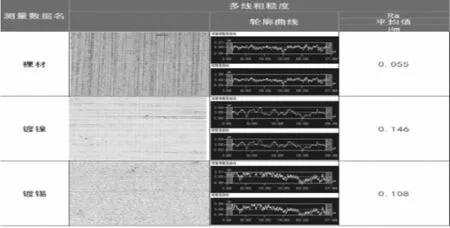

高速连接器用来传输差分信号的金属走线一般用铜带冲压加工,后续往往还需要对零件进行电镀、塑封工序。用来生产零件的铜带一般表面粗糙度状况良好,零件生产过程由于电镀夹具挂插、塑封模具挤压等因素影响,会导致粗糙度恶化,对金属走线裸材和电镀后的零件进行粗糙度测试具体数值见下表。

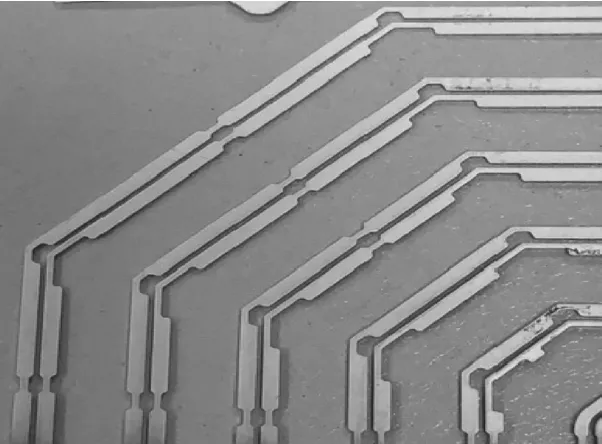

图10 测试区域示例

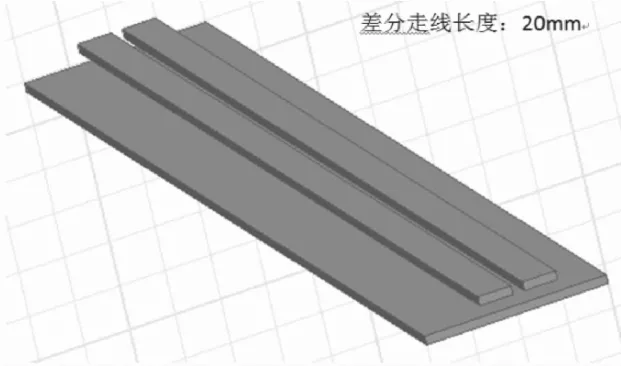

为确认粗糙度对差分信号传输插入损耗指标的影响,建立仿真三维模型,走线长度20mm。

图11 不同状态金属材料粗糙度测试值

图12 粗糙度仿真对比仿真模型

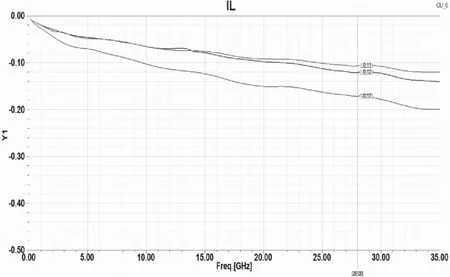

仿真模型设置粗糙度分别为0um、0.15um和1.5um,仿真结果见图13,在28Gbps,三种状态插入损耗差异仅为0.06db,高速连接器段走线的表面粗糙度导致的损耗针对整个链路的损耗要求来说,影响非常小。

图13 粗糙度仿真对比仿真结果

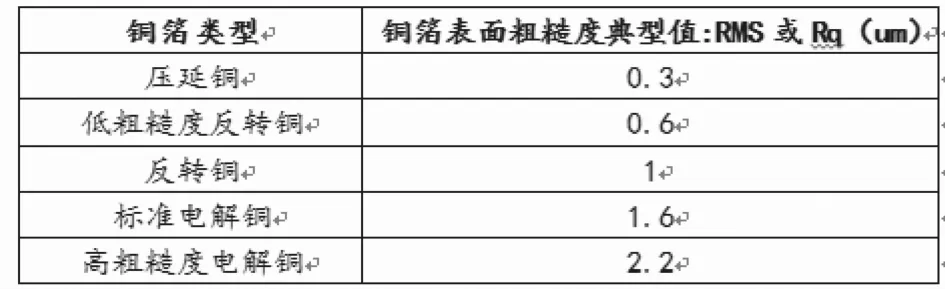

但针对高速连接器使用时压接的PCB板来说,铜箔的表面粗糙度影响则会有所不同。通常PCB基材加工过程中,为提高铜箔粘结后的稳固性,铜箔的表面会进行糙化处理。大多数的PCB基材都会压合几种形式的铜箔导体,包括标准电解铜、反转铜以及压延铜,不同的铜箔具有不一样的表面粗糙度,常用铜箔的粗糙度值见图14。

图14 不同类型铜箔粗糙度值

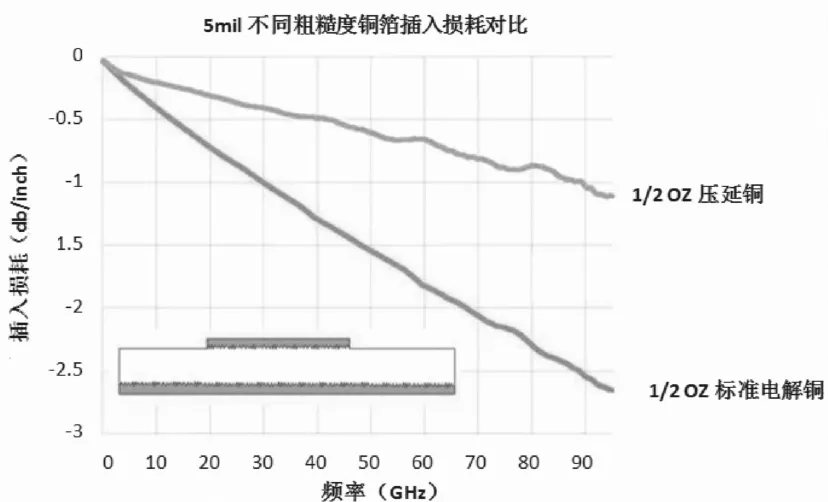

图15 两种铜箔插入损耗对比

不同铜箔表面粗糙度会产生不同的寄生电感,导致铜箔表面阻抗发生变化,从而产生不同的导体损耗。一般来说,当电路的工作频率对应的趋肤深度小于或者等于铜箔的表面粗糙度时,表面粗糙度的影响将会变得非常显著。

在频率<1GHz时,铜的趋肤深度2.09um,大于标准电解铜粗糙度1.6um和压延铜0.3um,两种铜箔的插入损耗并不明显,随着频率逐渐升高,此时标准电解铜和压延铜的损耗表现出显著的差异。这是由于随着频率升高,铜的趋肤深度呈现减小的趋势,标准电解铜的趋肤深度很快开始小于材料的表面粗糙度,导致插入损耗急剧恶化。