一种高速跳频MIMO无线通信系统设计*

2022-07-13王志军黄忠凡王建明

王志军,黄忠凡,申 翔,王建明,李 翔

(武汉中原电子集团有限公司研发中心,湖北 武汉 430205)

0 引言

射频芯片是现代小型化、低功耗无线通信设备系统中不可缺少的一部分,是影响系统通信性能的关键部件。随着通信技术的快速发展,高性能、高集成度、可灵活配置的射频收发芯片被广泛应用于现代无线通信设备中。目前,这一市场长期被国外产品所占据。在技术壁垒日益高企的今天,国产化应用正变得越来越迫切,尤其是在事关国家安全的国防通信领域[1],技术成熟稳定的自主可控芯片,逐渐成为国产替代的不二选择。

CX9261S是一款国产的宽带、高性能、多通道射频收发芯片,基于软件无线电设计理念[2],其芯片的可编程性使其可以灵活应用于多种需求场景。本文将对CX9261S性能做详细测试以证明其满足现代无线通信的需求,并将其应用在目前比较超前的、复杂的万跳MIMO无线通信系统当中。

1 CX9261S简介

1.1 参数与结构

CX9261S集成有独立的3个接收通道和两个发送通道,采用直接变频架构,每个通道都有单独的小数分频锁相环可用于提供本振,射频频段范围为70~2 700 MHz,这样的结构使其具有多种跳频配置方式,包含单点、多点以及万跳模式,可满足战术通信多样化的跳频抗干扰技术要求。高集成度的通道架构可灵活适配多种通信模式。

CX9261S的每个独立通道结构类似,包含有低噪声放大器、混频器、可编程增益放大器、宽带可变滤波器、高速高精度模数/数模转换器(Analog to Digital converter/Digital to Analog converter,AD/DA)和数字滤波系统,可实现射频信号的增益、混频、滤波和模数转换功能。接收增益动态范围达到64 dB,可实现多种模式自动增益控制(Auto Gain Control,AGC),发送功率增益范围为-30.0~11.5 dB。CX9261S具有20 kHz到60 MHz的可调谐通道带宽,具有16 bits的高性能宽带AD/DA,可兼容宽窄信号,具有直流(Direct Current,DC)校准、电阻电容(Resistance Capacitance,RC)校准和同相正交(In-phase Quadrature,IQ)校准功能,可抑制直流、本振、镜像及杂波等干扰,具有双工模式,可支持时分双工(Time Division Duplexing,TDD)和频分双工(Frequency Division Duplexing,FDD)。

1.2 与AD9361差异

国产CX9261S与国外主流射频芯片美国亚德诺半导体技术有限公司(ADI)的AD9361[3]对标,两者主要在通道数量和硬件结构以及性能参数两个方面有所不同。

1.2.1 通道数量及硬件结构

AD9361有独立的两个接收和两个发送通道,其中两个接收通道共用1个接收本振,两个发送通道共用1个发送本振,4个通道共用1个基带锁相环作为链路时钟。CX9261S有独立的3个接收通道和两个发送通道,每个通道都有自己独立的本振,TRX1、TRX2和RX3 3个通道都有自己独立的基带锁相环。

从应用层面来说,CX9261S的通道数量和锁相环更多,应用的灵活性更强,方式也更多样化,更适合多模并发的需求场景。

1.2.2 具体的性能参数

CX9261S的频段为70 MHz~2.7 GHz,相比AD9361的70 MHz~6 GHz较窄,但功耗略低,噪声性能更优,抗干扰能力更强。其他方面,例如带宽、双工方式、控制/数据接口、增益范围、编程驱动方式等,相差不大。

2 无线通信系统搭建

本文将搭建一整套万跳+MIMO的无线通信系统对CX9261S的性能进行验证,具体方案如下文所述。

2.1 硬件平台介绍

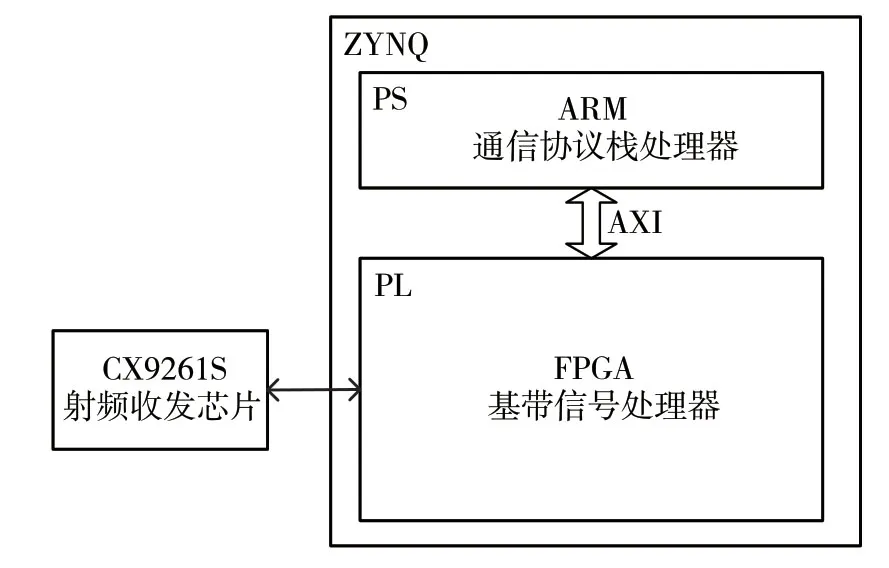

本文遵循软件无线电思想,采用目前比较成熟的零中频软件无线电方案[4]。数字部分采用片上系统(System on Chip,SoC)集成芯片ZYNQ-7100,该芯片集成有两个先进精简指令集微处理器(Advanced RISC Machines,ARM)与一个现场可编程逻辑门阵列(Field Programmable Gate Arrary,FPGA)[5],其中高性能且可并行处理数据的FPGA作为基带信号处理器件,逻辑运算强大的ARM作为通信协议栈处理器,整体组合搭建一套完整的软硬件协同设计的无线通信系统[6],在发挥各个部分硬件性能优势的同时,兼具灵活和可扩展升级的特点[7]。使用高集成度的射频收发芯片作为射频前端,CX9261S作为国产零中频的射频捷变收发器芯片,在技术自主可控的基础上,具有高灵活性和高性能,可适配无线通信的多种需求场景。

无线通信系统硬件平台的搭建方式及功能分布如图1所示。

图1 无线通信系统硬件平台

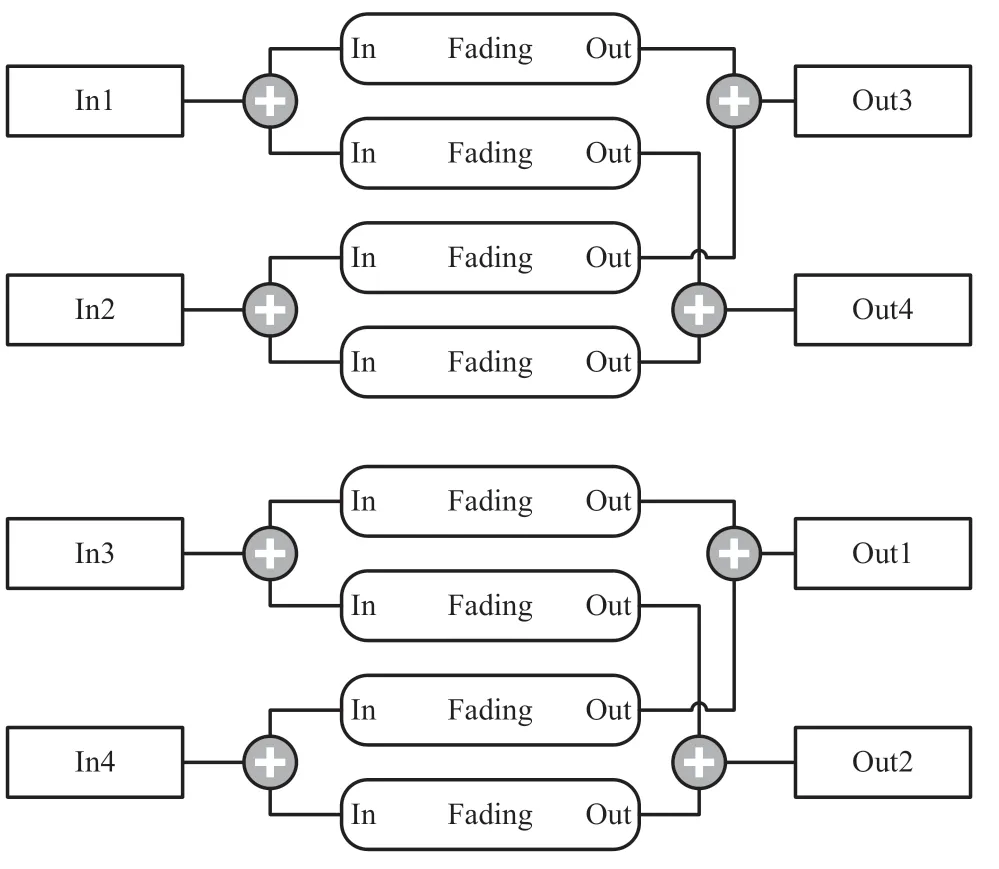

2.2 万跳MIMO无线通信系统

现代无线通信技术飞速发展,通信系统对传输速率的要求越来越高,传统的单天线收发模式,也越来越难以满足用户对高信道容量的需求[8]。此外,无线通信技术的蓬勃发展同样带来了异常复杂的无线通信环境,不同频段信号的相互干扰,以及应用在复杂地形带来的多径衰落等,都对无线通信系统的抗干扰性能提出了更严苛的要求。在现实需求下,MIMO和高速跳频相结合的技术逐渐成为无线通信系统的主流应用技术[9]。

2.2.1 MIMO设计

CX9261S集成有独立的3个接收通道和两个发射通道,支持通道1和通道2组合形式的两收两发MIMO,可满足在占用频段和带宽不变的情况下,实现信道容量提升或抗干扰能力加强的技术需求。

CX9261S的两收两发MIMO使用通道1和通道2,其中通道2为主控通道,当芯片被配置为2R2T时,将只识别通道2的收发控制信令及相关随路时钟,芯片使用通道2的基带时钟作为整个芯片的数据时钟。

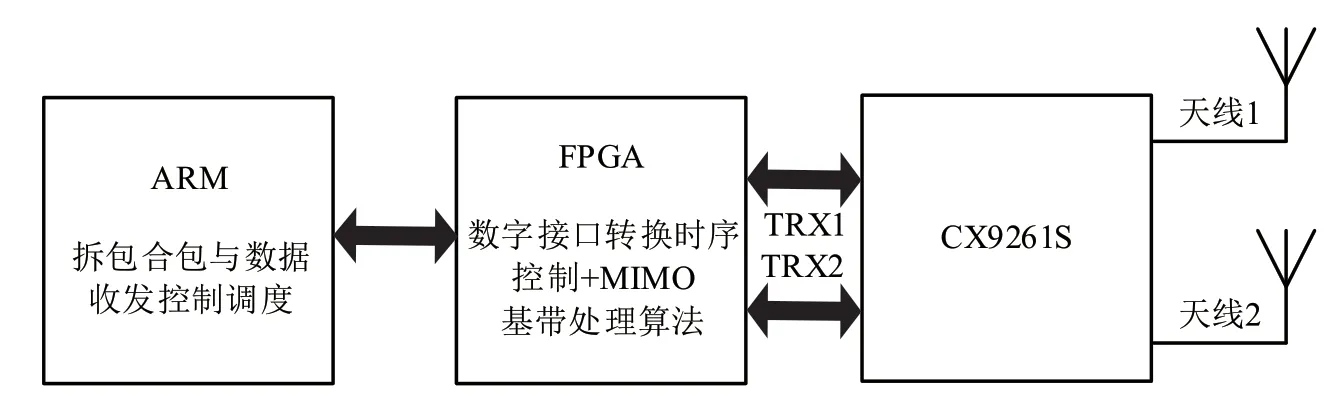

CX9261S应用在MIMO场景中时,最为关键的是数据流处理,由于其高时间精度要求和数据流并发性,因此把数字接口转换时序控制和MIMO基带处理算法放在FPGA上[10],而通信协议对逻辑性要求较强,因此把拆包合包与数据收发控制调度放在ARM上。通过这种设计方式,既能确保数据流的精准有序和高效处理,又能适配不同的传输协议要求和时隙结构。

MIMO驱动设计方案如图2所示。

图2 MIMO驱动设计方案

按上述设计方案编写代码实测,测得在该设计方案下,FPGA收到的两路接收数据流经过严格的时间处理后,可以做到在时间上精准对齐。在添加MIMO基带处理算法后,相比于单天线收发,通信系统对小信号的检测能力提升至少一倍。

因此,这样的MIMO驱动设计方案,既可以用来提升通信系统的信息速率,又可以用来增强通信系统的抗干扰能力。

2.2.2 万跳设计

CX9261S支持乒乓快速跳频模式,可实现万跳级别的跳频通信,减少频率的驻留时间,降低被干扰的可能性[11]。相较于AD9361,CX9261S可应用于跳频速率要求更高、频点要求更灵活的通信场景。

在TDD通信系统中,CX9261S通过乒乓的方式进行频率的预校准,即用户将两个锁相环(Phase Locked Loop,PLL)(TXPLL和RXPLL)模块分别锁定,在切换频率时,预先将当前未共用的PLL锁定到目标频点,跳频时,只需通过选择由当前共用PLL模块切至未共用PLL模块,即可实现频率的快速切换。

在具体的MIMO+跳频应用场景中,把跳频过程中多样化的用户配置放在ARM上,这样不仅能满足多条件逻辑运算的用户应用需求,同时也方便前期的开发与后期的调试。ZYNQ集成的FPGA时间性能强,因此把万跳驱动中对时间性能要求比较高的部分放在FPGA上。通过这种设计方式,既能满足多场景应用,又能适应数字通信系统的高时间精确性要求。

万跳驱动设计方案如图3所示。

图3 万跳驱动设计方案

按上述设计思路编写代码实测,测得预校准未共用锁相环,本振锁定耗时约16μs,但这段时间是不影响正在运行的收发的,因此,在做通信系统协议设计时,不需要为这段时间预留保护间隔。共用锁相环切换会影响信号,但实测耗时小于1μs。

因此,这样的万跳驱动设计方案,可以在完成应有功能的前提下,尽量减少占用通信协议的时间开销,提升通信系统整体设计的灵活性。

3 系统测试

使用ZYNQ+CX9261S作为通用硬件平台,按照上述程序设计思路构筑驱动层,结合具体设计的波形物理层和MAC协议栈,搭建出一套完整且实测可用的万跳MIMO无线通信系统,这里对波形部分不做具体介绍。针对该系统进行各项测试,以验证设计思路与硬件的合理匹配。

3.1 收发频谱

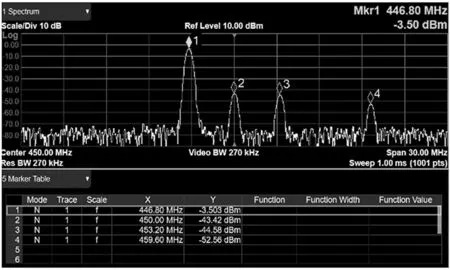

3.1.1 CX9261S发送单音

测试环境:常温下,射频本振为450 MHz,发送增益为0 dB,发送由直接数字频率合成(Direct Digital Synthesis,DDS)产生的基带频率为3.2 MHz的单音。

发送信号的频谱如图4所示。

图4 9261发送单音信号频谱

可以看到,发送频谱中,本振抑制大于40 dBc,镜像抑制大于41 dBc,本振附近其他杂波及噪声抑制大于49 dBc,在偏移100 MHz处,本底噪声的功率谱密度为-157 dBm/Hz。

3.1.2 CX9261S接收单音

测试环境:常温下,射频本振为450 MHz,接收增益为1 dB,接收由信号源发出的功率为0 dBm的451 MHz的单音信号。

MATLAB画出的接收信号的频谱如图5所示。

图5 9261接收单音信号频谱

可以看到,接收频谱中,本振抑制大于37 dBc,镜像抑制大于41 dBc,本振附近其他杂波及噪声抑制大于49 dBc。

3.1.3 CX9261S发送宽带信号

测试环境:常温下,射频本振为450 MHz,发送增益为0 dB,发送正交相移键控(Quadrature Phase Shift Keying,QPSK)宽带信号。QPSK信号自己产生,符号速率为8.53 Msym/s,成型滤波为根余弦,系数为0.25。

发送信号的频谱如图6所示。可以看到,噪声抑制大于40 dBc。

图6 9261发送QPSK信号频谱

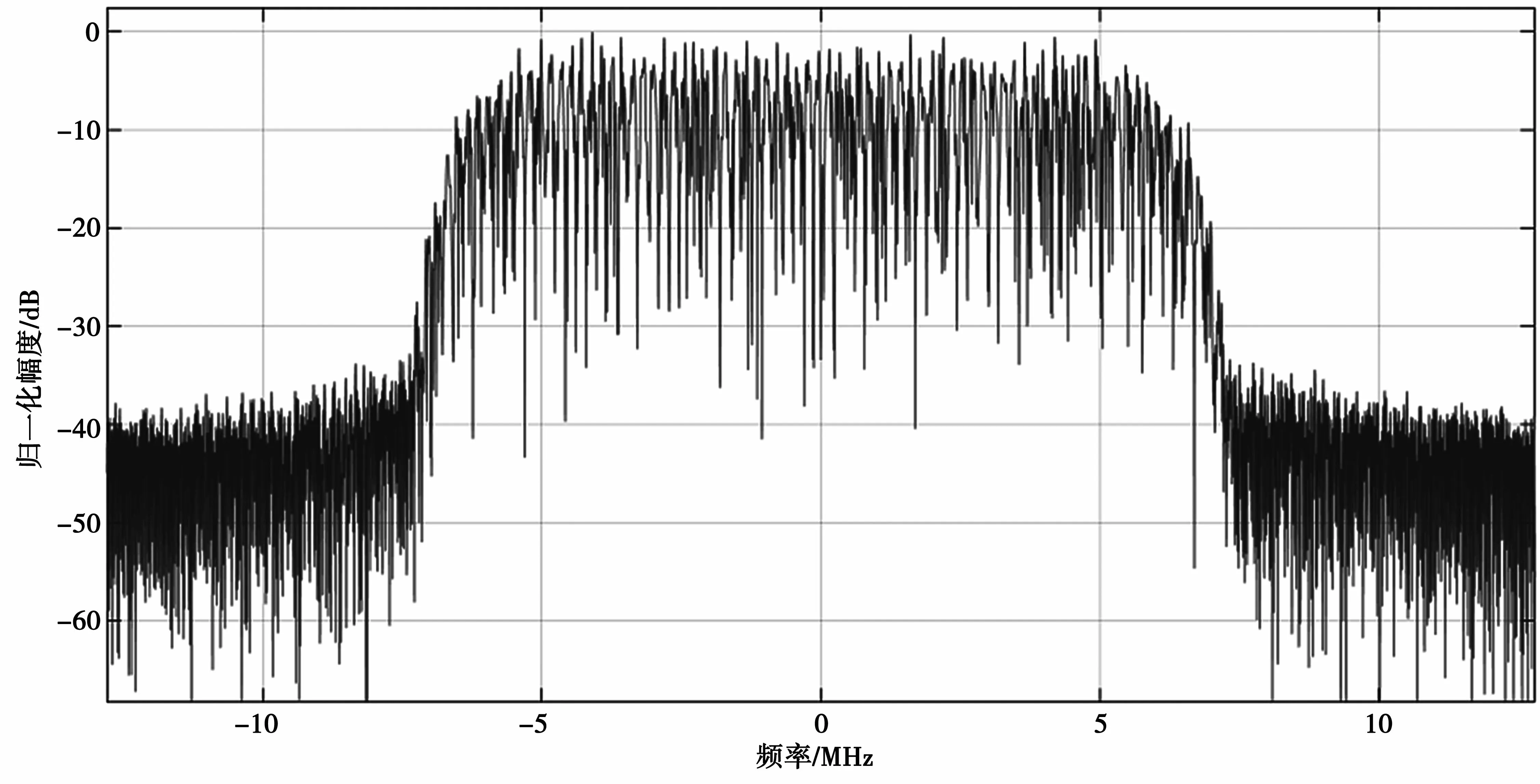

3.1.4 CX9261S接收宽带信号

测试环境:常温下,射频本振为450 MHz,接收增益为1 dB,接收QPSK宽带信号。QPSK信号由信号源发出,功率为0 dBm,频率为450 MHz,符号速率为12 Msym/s,采用根余弦成型滤波,系数为0.2。

MATLAB画出的接收信号的频谱如图7所示。可以看到,噪声抑制大于40 dBc。

图7 9261接收QPSK信号频谱

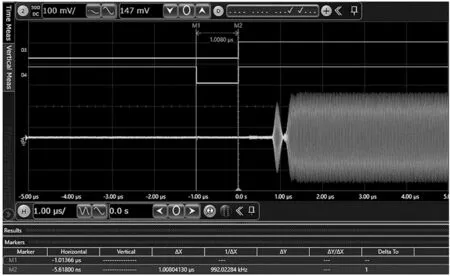

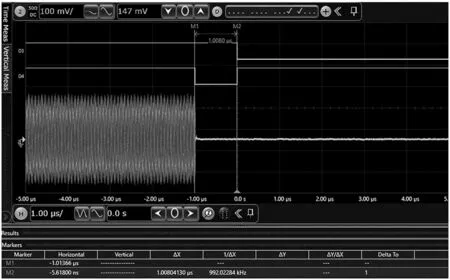

3.2 收发切换时间

控制CX9261S收发切换时,需先将enable信号拉低,控制使能状态机(ENable State Machine,ENSM)退出前一状态进入flush-alert状态,等待1μs后,再进行下一状态的收发控制。

测试环境:将CX9261S的收发控制信号enable和txnrx接到示波器,把射频信号也接到示波器,频繁进行收发切换控制,观测1μs是否足够CX9261S的ENSM进行收发状态的切换。CX9261S由接收切换到发送的示波器图如图8所示。图8中,数字管脚D3为txnrx信号,D4为enable信号。

图8 9261收转发

CX9261S由发送切换到接收的示波器图如图9所示。

图9 9261发转收

可以看到,退出前一状态后,等待1μs即足够CX9261S的ENSM进行收发状态的切换。

3.3 增益稳定时间

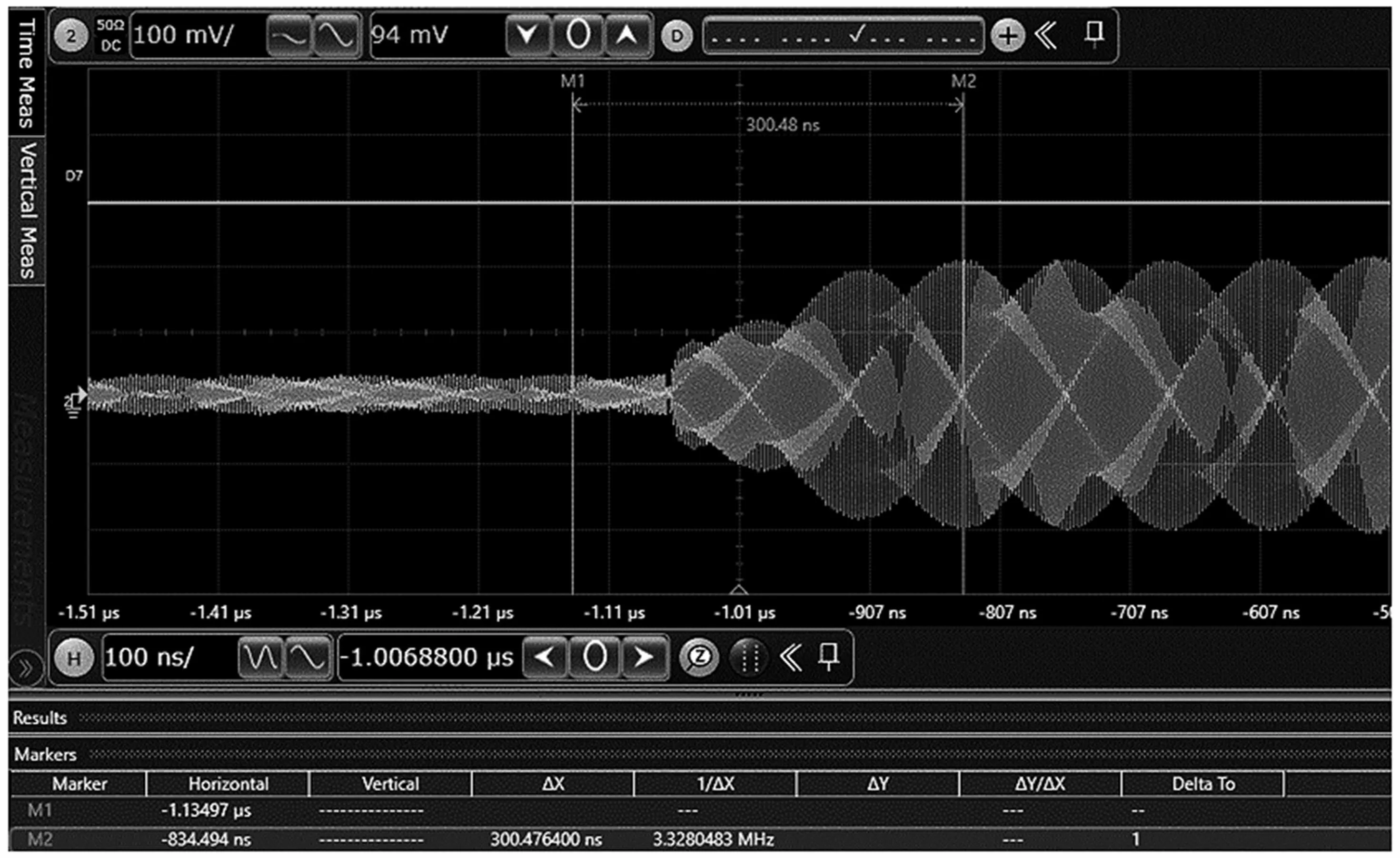

3.3.1 发送增益稳定时间

测试环境:CX9261S发送单音信号,发送增益在0 dB和-15 dB之间频繁切换,将发送信号接到示波器进行观测。

9261发送增益切换的示波器图如图10所示。

图10 9261发送增益切换

可以看到,修改CX9261S的发送增益后,发送信号的幅度稳定需耗时约300 ns。

3.3.2 接收增益稳定时间

测试环境:信号源发送-5 dBm的451 MHz单音信号,CX9261S本振为450 MHz,接收增益在1 dB与10 dB之间频繁切换,使用Vivado的ILA抓取接收到的基带数据,如图11所示。

图11 9261接收增益切换

可以看到,修改接收增益后,接收信号的幅度稳定需耗时56个采样点,ILA采样时钟为51.2 MHz,计算可以得出耗时约1.1μs。

3.4 通道时延

测试环境:CX9261S的数字滤波系统,只使用积分—梳状级联滤波器(Cascaded Integrator-Comb filter,CIC)、半带滤波器(Half Band filter,HB)和旁路非递归型滤波器(Finite Impulse Response filter,FIR)。将收发控制信号enable和txnrx连接到示波器,将射频信号也接到示波器。CX9261S进行收发切换,发送内置的测试单音(Built-In Self Test,BIST),观测控制信号与射频信号之间的时延。

9261发送通道时延的示波器图如图12所示。

图12 9261发送通道时延

可以看到,在此测试环境下,CX9261S的ENSM切换为发送到空口发出信号之间的时延约为840 ns。

3.5 EVM

将CX9261S配置为通道独立收发的模式,使用通道1接收信号源的标准调制信号,内部基带信号回环后,由通道2发送到频谱,解调后观察误差向量幅度(Error Vector Magnitude,EVM)。设置通道1的接收增益为1 dB,通道2的发送增益为0 dB,两个通道的本振均为450 MHz。

3.5.1 QPSK解调

测试环境:信号源调制方式为QPSK,符号速率为12 Msym/s,功率为-11 dBm,频率为450 MHz,成型滤波为根升余弦,系数为0.2。将信号经过CX9261S回环后,输出到频谱解调。

9261回环QPSK的典型EVM情况的仪器图如图13所示。

图13 9261回环QPSK的典型EVM情况

可以看到,QPSK信号经过CX9261S的接收通道和发送通道后,总的EVM为2.16%rms。

3.5.2 16QAM解调

测试环境:信号源调制方式为16QAM,符号速率为16 Msym/s,功率为-11 dBm,频率为450 MHz,成型滤波为根升余弦,系数为0.2。将信号经过CS9261S回环后,输出到频谱解调。

9261回环16QAM的典型EVM情况的仪器图如图14所示。

图14 9261回环16QAM的典型EVM情况

可以看到,16QAM信号经过CX9261S的接收通道和发送通道后,总的EVM为2.71% rms。

3.6 万跳频率切换时间

测试环境:CX9261S发送单音,本振频率在450 MHz和2 GHz之间频繁切换,将空口发送信号接到示波器,观测切频前后发送信号的变化。

9261万跳的示波器图如图15所示。

图15 9261万跳

其中,M3和M4标识变频前,频率为450 MHz,M5和M6标识变频后,频率为2 GHz,M1和M2标识变频需要的时间。可以看到,CX9261S进行万跳时,切频需要的保护时间小于1μs。

3.7 MIMO性能测试

测试环境:使用两套万跳MIMO通信设备+信道仿真仪互联互通,在跳频速度为万跳的环境下,测试满足数据接收成功率大于90%的最小接收功率,分别测试单天线收发与MIMO情况,对比两者的测试结果。通信系统的传输速率为512 kbit/s,使用信道仿真仪,信道模型为Rayleigh多径模型。

信道仿真仪搭建的拓扑图如图16所示。

图16 多天线技术测试环境

测试结果:测得单天线下,满足接收成功率大于90%的最小接收功率为-99 dBm,相同环境下,使用多天线,该值为-103 dBm。

可以看到,具备MIMO硬件条件的通信系统,结合优化算法,在多径信道下,通信系统对小信号的检测能力提升了至少一倍。

4 结语

本文基于国产化射频芯片CX9261S设计了一种无线通信硬件平台,并重点说明了将该平台应用在较为超前和复杂的万跳MIMO无线通信系统中的驱动设计的思想。实测结果表明,国产化的CX9261S是可以满足小型化、低功耗的通信设备要求的,并且在有高速率跳频和MIMO应用需求的场景,CX9261S是有其优势的。