高压达林顿晶体管FHD1071的热稳定性设计

2022-07-04张小平高广亮伏思燕

张小平,高广亮,陈 浩,刘 帅,伏思燕,苏 舟

(锦州辽晶电子科技有限公司,锦州 121011)

1 引言

达林顿晶体管具有很高的放大倍数,这一特征会导致前级管的漏电流逐级放大,对器件稳定性造成影响。特别是当温度升高时,反向漏电流将随温度增加而增加,同时器件放大倍数也会增加,就有可能使器件因为高温下功耗增加而发生热击穿甚至烧毁。高耐压达林顿晶体管在制作过程中选用高电阻率的原材料,并且原材料的厚度较厚,容易造成饱和压降偏大,热稳定性不够理想。针对这一问题,在此对常规设计方案进行改进。采用带缓冲层的穿通设计,一方面可减小饱和压降,另一方面可提高抗二次击穿能力[1]。对电阻进行优化设计,减小温度对电阻的影响,以此提高产品的热稳定性。

2 热稳定性分析

晶体管的热稳定性含义是在工作过程中,在经受热循环时器件的抗热击穿能力以及壳温在较大温度范围内变化时,晶体管主要参数的稳定性。热击穿一般表现为当器件温度升高到特定温度时,功率晶体管突然损坏。由于达林顿功率晶体管的放大倍数可达几百到几千甚至上万倍,当处于放大状态时发射极电流和集电极电流随温度的增加而迅速上升,会使器件的工作状态超出安全工作区,更容易在内部出现电流集中,形成过热点。当过热点温度超过半导体的熔点(硅的熔点1415℃)或该处接触的金属熔点(铝硅熔点577℃)时,器件将永久性失效[2]。另外的情况是,即使过热点的温度不足以引起金属或半导体熔化,由于各点温度不同,所产生的应力也足以导致晶格的严重损伤,终致器件失效。

大功率晶体管本身消耗功率很大,会使晶体管的结温度升高,电参数也随着温度的变化而变化;高耐压达林顿器件的放大倍数本身偏大,这样就会形成恶性循环。在生产过程中,由于扩散浓度的不均匀和工艺制程带来的表面和内部缺陷,会造成局部热击穿。制程中过大的饱和压降也会导致较大的热功率损耗,造成过热,影响器件的正常使用。所以高耐压达林顿晶体管的热稳定性设计极为重要,是此处改进设计的关键[3]。

3 热稳定性优化设计

选用FHD1071型高压达林顿晶体管产品进行改进设计。以优化热稳定性为目的,需要对产品的横、纵向参数进行优化。在满足产品耗散功率PCM与电流容量ICM指标的前提下,将击穿电压设计为穿通型击穿,以减少器件的饱和压降,并增加缓冲层以提高器件的抗二次击穿能力;通过对泄流电阻的设计,减少温度变化对器件放大倍数的影响;在工艺过程控制方面,增加表面钝化工艺提高器件的可靠性,采用背面金属微合金工艺、真空烧结工艺减少器件的热阻[4]。

3.1 器件结构设计

3.1.1 横向参数设计

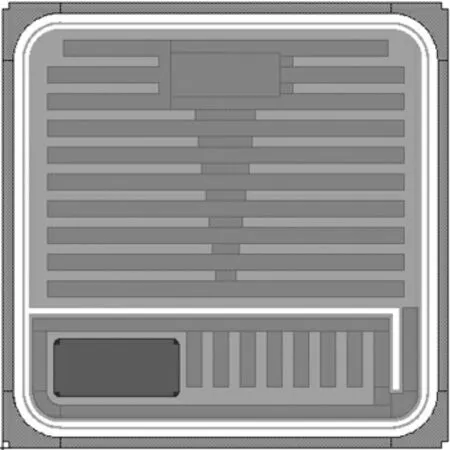

在改进设计中,为保证器件集电极电流ICM正常,同时减少发射极电流集边效应,要对低频功率晶体管的发射区周长LE进行设计。在版图设计上采用梳状发射极的结构,以此增加发射极周长,兼有均流的作用。设计版图如图1所示。

图1 产品芯片改进设计版图

发射极面积由设计指标所要求的最大集电极电流ICM和实际允许的最大集电极电流密度决定。ICM的定义通常是指随着集电极电流增加,放大倍数降低到峰值1/2或1/3时对应的集电极电流值。实际的最大电流密度不仅与发射极周长有关,也与发射极面积有关。材料的电阻率不同,晶体管的最大线电流密度和面电流密度也有所不同[5]。

晶体管发射区的面积由面电流密度JCR和最大集电极电流ICM来确定;发射极周长则由线电流密度JCM和最大集电极电流ICM确定。根据实际产生经验,此处应取JCM=0.4A/cm,JCR=50A/cm2。

经计算,发射极面积为AE=0.05cm2,实际设计选取0.05cm2;发射极周长为LE=6.25cm,实际设计选取6.8cm。

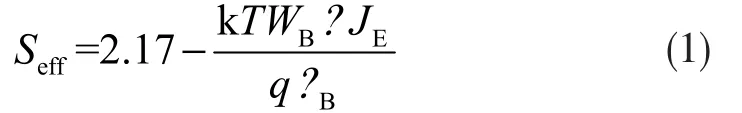

考虑到电流集边效应与均流措施,如下式:

式中,WB为基区宽度;β为放大倍数,ρB为基区电阻率。计算得到发射极有效半宽度Seff=75μm。

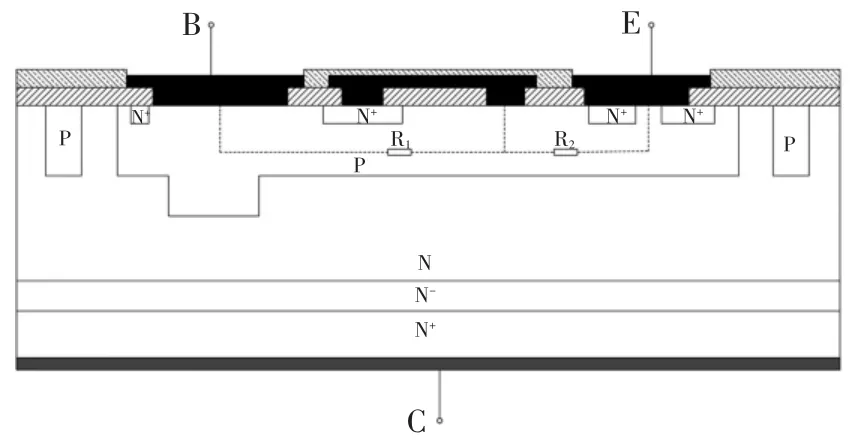

3.1.2 纵向参数设计

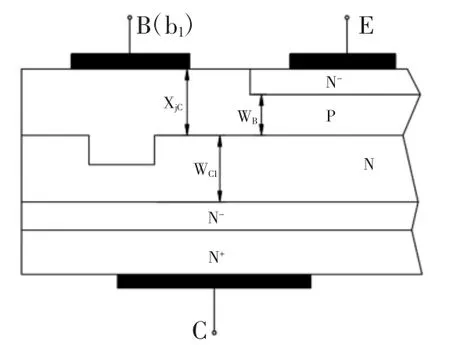

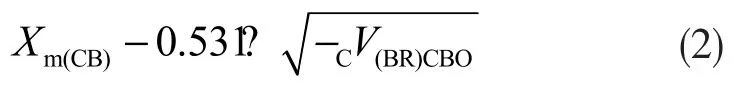

器件结构的纵向结构如图2所示。高反压器件在最大耗尽层厚度不限制的情况下,高阻层厚度比较厚。然而高阻层太厚对大电流特性及饱和压降都是不利的。为了兼顾工艺水平、耐压能力、大电流特性及饱和压降等多方面的要求,采用穿通型击穿设计,即取较小的高阻层厚度,以改善电流特性、关断速度及饱和压降等参数[6]。高阻层厚度由CB结击穿的最大空间电荷区决定,即:

图2 芯片纵向结构图

将ρC=30Ω·cm、V(BR)CBO=1320代入式(2),可计算得出Xm(CB)=101μm。

因为产品的集电结击穿电压V(BR)CBO>450V,取集电极穿通击穿电压V(BR)CBO穿通=600V,穿通击穿电压与雪崩击穿电压关系如下:

将V(BR)CBO=1320V、Xm(CB)=101μm代入式(3),计算得到:WC1=30μm。

从改善雪崩注入二次击穿的角度考虑,要求集电区厚度WC≥V(BR)CEO/Em,Em为最大电场强度。选择WC为50μm的集电区外延层厚度,同时采用双层外延工艺来提高器件的反向二次击穿耐量。集电结XjC为20μm。考虑到工艺过程中衬底的反扩散,外延层厚度为WC、XjC和反扩距离相加,约75~80μm。

基区宽度WB是一个极其重要的几何参数,它的大小直接影响到最高击穿电压V(BR)CBO、V(BR)CEO、电流放大系数β等电参数,同时也影响双极型大功率器件的二次击穿耐量。为了提高抗二次击穿耐量、提高热稳定性、增加基区结深即增加基区宽度,采取的方法是减小基区的自偏压效应,避免电流过于集中,从而改善热稳定性[7]。在改进设计中,基区宽度选取10μm。

3.1.3 泄流电阻设计

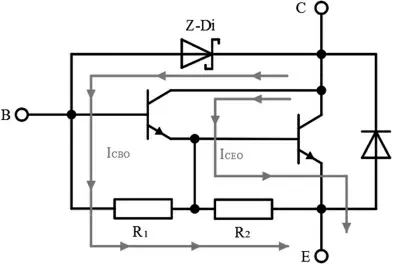

FHD1071型达林顿晶体管由两个三极管、一个保护二极管与泄流电阻组成,结构示意图如图3所示。其中,ICEO是三极管本身固有的穿透电流,只取决于少数载流子的浓度和温度,其值随着温度的升高而增大。前级三极管的穿透电流被后级三极管进一步放大后,会导致达林顿管热稳定性变差,电阻R1和R2提供了穿透电流的释放回路,使穿透电流通过电阻释放到外面,而不会被后级三极管进一步放大,从而提高器件的温度稳定性。

图3 FHD1071型达林顿晶体管原理图

泄流电阻R1、R2的阻值由四个因素确定:热稳定性、输出特性曲线线性要求、双结的击穿电压与开关速度。对于高压大功率达林顿器件,热稳定性和线性是主要因素,R1、R2越小达林顿管的热稳定性越好。但由于R1、R2的分流作用,使得小电流放大倍数下降严重,输出特性曲线线性会变差[8]。一般情况下,R1比较大时有利于提高放大系数线性,R2比较小有利于提高器件的热稳定性。

达林顿晶体管的放大倍数随温度升高而变大是由两个因素导致的:一是双极型器件固有的电流放大系数的正温度系数特性;二是泄流电阻阻值的正温度系数。由于泄流电阻阻值随温度升高而变大,这就使得其对基极电流的分流作用随温度升高而减弱,导致前级三极管的注入电流增加,使达林顿晶体管总体放大倍数增加。

半导体扩散电阻随温度的变化率与扩散方块电阻(R□)大小有关,方块电阻值比较小时,温度变化率也较小。硼扩散情况下,方块电阻对应温度系数变化规律如表1所示。

综上可知,采用硼扩散薄层电阻值较小的扩散电阻设计对器件稳定性有改善作用,但R□不能设计得太小,它会影响器件的开启速度,又影响器件放大倍数的调整。改进设计中,选用R□=90~100Ω/□;基区的表面浓度为8×1017~1×1018cm-3,使得在150℃时的电阻值只增加20%,对放大倍数的影响减到最轻。R1的取值为1.5~2 kΩ,采用发射区下方夹层电阻和基区电阻并联的方式,使温度对电阻的影响变小;对R2的取值为150~200Ω,为发射区下的基区横向电阻。电阻分布具体结构示意图如图4。

图4 电阻分布示意图

3.2 器件工艺设计

3.2.1 掺氯氧化与表面氮化硅低温淀积

产品在制作工艺中,在基区氧化和基区硼再扩散的氧化过程采用掺氯氧化,具体工艺过程为:

当炉温升到1050~1100℃时,将携带三氯乙烯、流量为100 mL/min的氧气通入炉管中,反应时间30~40min。在高温下氯离子与钠离子反应生成气态氯化钠,随保护气体被带出炉管,可有效减少二氧化硅薄膜中钠离子沾污,提高氧化层质量,减少器件表面漏电,从而减小ICBO和ICEO。

在芯片的表面采用PECVD氮化硅工艺。这一步属于制成芯片的最后一道工艺,除了压焊区以外的有源区均被氮化硅膜覆盖。氮化硅膜介质特性优于二氧化硅膜,对可动离子阻挡能力强,化学稳定性好,通常不需要太厚就可起到表面钝化的作用。本产品选用膜厚为200 nm的氮化硅,作为最后的保护膜,可有效减少表面沾污对器件的影响,也可防止意外的损伤,提高器件的可靠性,也包括器件的高温稳定性。

3.2.2 管芯背金工艺改进

芯片背面经过气体喷砂或背面减薄工艺处理后,需要进行背面电极集电极的制作。管芯背面金属电极采用多层金属(钛、镍、银三层)的结构。为了提高背面金属的焊接强度,在蒸发工艺过程结束后采用升高蒸发台的腔体温度至300℃的方法,实现钛层金属与硅的微合金化,从而提高牢固性,减小接触热阻[9]。

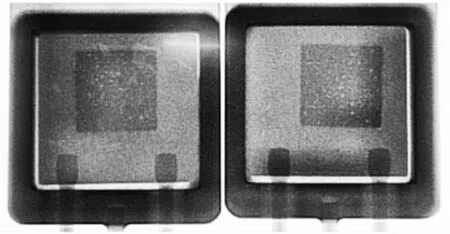

另外,增加银层的厚度至1.5μm,以提高芯片与管座的粘润质量,增加焊接的强度。采用真空烧结工艺,减少空洞的产生。实际测试表明,空洞率可控制在5%以内,芯片表面实际外观如图5所示。

图5 X射线下的空洞照片

4 测试结果

结合产品横/纵向参数、热稳定及可靠性的设计改进,采用不同的基区方阻,分R□=90~100Ω/□和190~200Ω/□两个条件投产了两个批次,每批次10片,共计20片,具体工艺过程如下:

硅材料一次氧化→箝位二极管光刻→硼扩散→基区光刻→基区扩散→发射区扩散→电极孔光刻→正面蒸铝→铝反刻→合金→PECVD氮化硅→压焊点光刻→刻蚀→背面处理→背面金属化→划片→测试→焊接→键合→封帽→测试→筛选→入库。

在封装工艺中,采用TO-257封装形式,对其中的20只样品进行产品一致性检验。分别取3只进行了高低温和热阻测试,测试结果详见表2~表4。

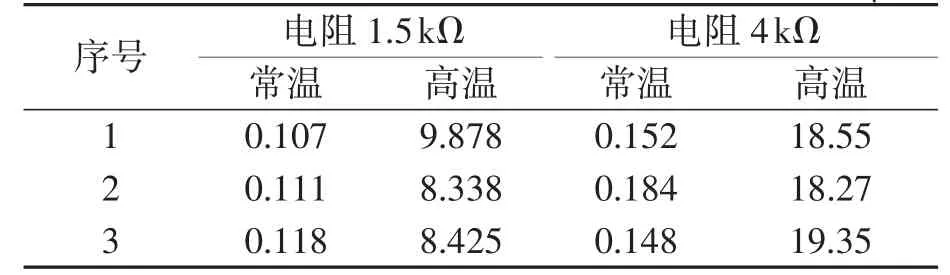

表2 漏电流I CEO测试结果单位/μA

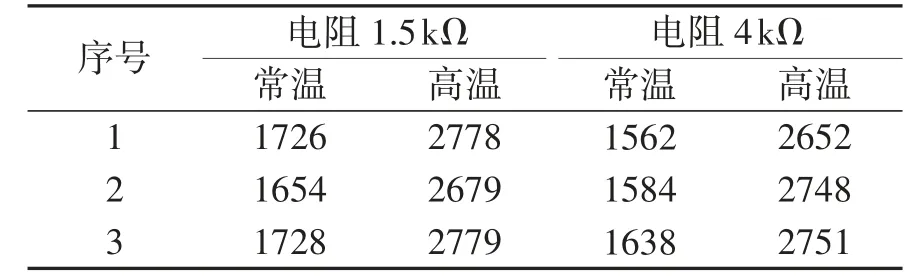

表3 放大倍数测试结果

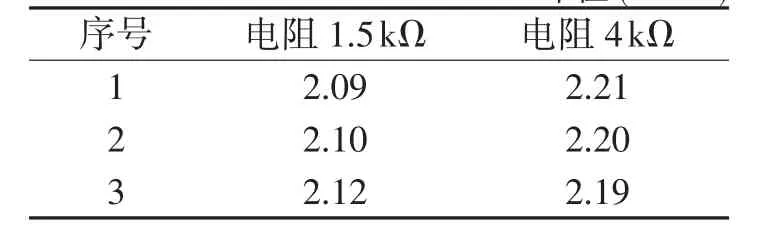

表4 热阻值测试结果单位/(℃·W-1)

从测试数据来看,各参数合格,热阻值能够达到改进设计的目标。通过合理的设计与工艺调整,改善了达林顿晶体管的热稳定性及产品的可靠性。

5 结束语

根据产品主要电参数的要求,在满足基本电参数的同时,重点优化了产品工作的热稳定性。通过合理的器件的横/纵向设计,在常规击穿电压中引入穿通型电压设计,采用合适的基区表面浓度和基区宽度,保证了器件的饱和压降。通过电阻合理的设计,减小放大倍数受到的影响,得到了较小的高低温变化率,增加了器件的工作稳定性。通过芯片表面的钝化工艺和掺氯氧化,有助于减小表面漏电,提高器件的可靠性。通过合适的金属化、烧结工艺和封装形式,减小了热阻,提高了产品的热稳定性。