基于高肖特基势垒的高导通电流隧穿场效应晶体管

2022-07-04赵瑞英靳晓诗

赵瑞英,靳晓诗

(沈阳工业大学信息科学与工程学院,沈阳 110870)

1 引言

多栅MOSFET[1]在小于30 nm技术节点中有出色的表现,它需要使用昂贵的毫秒退火技术来实现纳米尺度的突变结。SB-MOSFET形成浅肖特基势垒而不是MOSFET的PN结势垒[2]。金属源漏(S/D)架构的优势在于放松传统植入S/D的严格限制[3],对于P型SB-MOSFET,价带空穴的肖特基势垒高度远小于导带电子。对于较浅的肖特基势垒高度,热电子发射电流总是小于理想的0 eV势垒高度,此外SB-MOSFET的亚阈值摆幅大于60 mV/dec,用简单的势映射方法可证明亚阈值摆幅不能通过肖特基势垒而不考虑其他物理机制,如带带隧穿[4]。尽管SBMOSFET在纳米级工艺中比传统MOSFET更容易制造,但这些物理机制也会导致性能下降,如较低的开关电流比和正反向电流比。在新开发的器件中,TFET最具代表性,它利用带带隧穿作为电流传导机制,可以实现低亚阈值摆幅[5],但要实现更小的亚阈值摆幅,TFET中也必须形成与MOSFET类似的突变结[6]。其电流驱动能力也比MOSFET差很多,在反向偏置状态下,带带遂穿诱导的漏电流会明显增大,甚至比正向电流大。为此,提出一种基于高肖特基势垒辅助栅的隧穿场效应晶体管:HSB-BTFET[7]。然而,由于带带隧穿是HSB-BTFET的主要电流产生机制,与其他类型的TFET类似,形成了高的源漏阻抗,正向导通电流受到严重限制。在不引起集成退化的情况下显著提高正向导通电流,进而提出一种高导通电流垂直源漏接触高肖特基势垒H型栅和辅助栅控制双向隧道场效应晶体管:HOSC-HSBBTFET。

2 HOSC-HSB-BTFET器件结构

为了在不增加任何额外芯片面积的情况下有效增加源漏接触面积,源和漏接触被深深插入硅体,从而最大限度扩大接触面积。通过带带隧穿现象,接触面积的最大化,增加了在相同电压下产生的电子-空穴对的数量,并且可以产生更高的开态电流。与HSB-TFET相比,HOSC-HSB-BTFET可以实现更高的集成度、更低的亚阈值摆幅、更小的反向偏置漏电流、更高的开态电流和开关电流比。

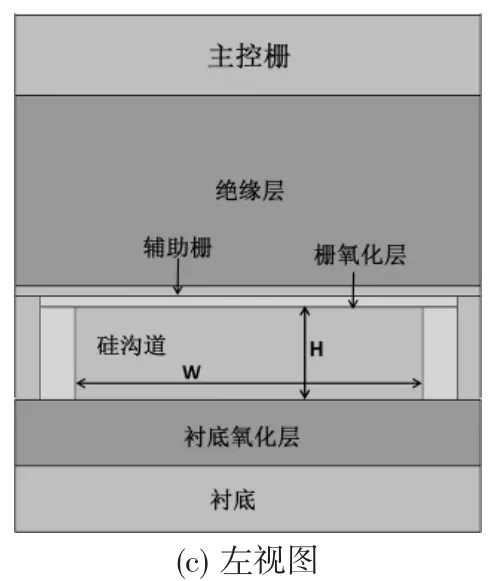

HOSC-HSB-BTFET器件结构如图1所示。如图1(a)和图1(b)所示,器件结构对称,源漏区可互换。主控栅呈H型,从三个方向控制源漏附近的硅,加强了对源漏的控制。硅被刻蚀成U型结构,通过再次对硅体两侧进行刻蚀,将源极和漏极插入U型硅两侧垂直部分的一定高度。辅助栅呈现倒U型结构,类似于自对准双栅场效应晶体管的栅结构,控制U型硅体底部水平部分的三面。

图1 新设计HOSC-HSB-BTFET结构示意图

图中,L和Lh分别为U型硅沿源-漏方向垂直和水平部分的长度;W是U型硅横向部分的宽度;LSD和WSD分别为源漏接触的长度和宽度;hsd为源漏接触的高度;H和hc是U型硅的水平和垂直部分的高度;tox是栅氧化层的厚度;tag是辅助栅的厚度;Lag为辅助栅宽度;hMG为主控栅高度;tsp为主控栅与辅助栅的间距。

考虑到亚阈值摆幅可以通过在尖锐金属结上的带带隧穿获得,因此在源区和漏区都形成了基于金属结的高肖特基势垒。一般来说,SB-MOSFET产生热电子发射电流通过一个相对较低的肖特基势垒作为正向电流供应的物理机制。HOSC-HSB-BTFET在带隙中心附近形成较高的高肖特基势垒。这在很大程度上阻断肖特基势垒热离子发射电流。它增加了带带遂穿电流的产生,作为设备的开启机制。考虑到隧穿电流的总量与可发生隧穿效应的硅区的总体积以及隧穿区电场的大小有关,隧穿区应设计得尽可能大。通道部分采用凹槽结构,为U型通道。针对HOSC-HSB-BTFET,设计了插入式源漏接触,通过增大隧穿区域的有效面积,实现载流子最大化,保证源漏距离相对较大,有效防止反向漏电流。

通过增加U型硅区垂直部分的高度,在不增加器件占用总芯片面积的情况下,可以大幅度增加隧道层的总体积。倒U型辅助栅控制了载流子在器件中心通道的流动。U型硅区域的水平部分允许电子通过并阻止空穴流过。

3 与HSB-BTFET特性比较

所提出的HOSC-HSB-BTFET的特性已通过SILVACO Tools的器件模拟[8]进行了验证。为验证器件的性能,对新提出的HOSC-HSB-BTFET和HSBBTFET进行比较。HSB-BTFET结构示意图如图2所示。

图2 HSB-BTFET结构示意图

在相同的仿真环境下比较两者IDS-VGS转移特性,比较结果如图3所示。

图3 转移特性曲线比较

由图3可见,HSB-BTFET的沟道高度为5 nm,HOSC-HSB-BTFET硅沟道垂直部分的高度为1μm。与HSB-BTFET相比,HOSC-HSB-BTFET在低栅压区和反向栅压区具有更低的电流,从而导致了更低的静态功耗和更低的反向漏电流。同时,在正向栅偏置区,HOSC-HSB-BTFET产生了更高的开态电流,从1×10-7A增加到8×10-6A以上。开态电流增加约80倍,亚阈值摆幅降低到30 mV/dec。与HSBBTFET相比,HOSC-HSB-BTFET具有更低的亚阈值摆幅和更高的开关电流比。

两种器件在关态下硅体内的一维电流密度分布曲线的比较结果如图4所示。由图中可见,HSBBTFET的电流密度最大值比HOSC-HSB-BTFET的电流密度低近3个数量级。在相同VGS电压下,与HSB-BTFET相比,HOSC-HSB-BTFET更容易导通。

图4 一维电流密度分布曲线比较

4 关键参数影响分析

图5给出了不同垂直沟道高度的HOSC-HSBBTFET的转移特性曲线。垂直沟道高度从50 nm到1μm不等。随着垂直沟道高度的增加,同一栅偏压下正向导通电流变大,由于垂直沟道高度增加,源漏与硅的接触面积增大,发生隧穿效应的硅区总体积增大,总隧穿电流增大,导致源漏与硅界面处正向导通电流增大。此处,反向漏电流变化不明显,由于源漏接触没有直接插入到硅体底部,因此在主控栅和辅助栅之间保持一定距离,有效降低了反向栅偏置状态下硅体内最大电场强度,防止主控栅和辅助栅之间区域由带带隧穿产生漏电流。随着垂直高度的增加,有效沟道长度增加,越来越多的载流子通过,电流密度增大,但不是无限的。当垂直沟道高度在510 nm以上时,正向电流无明显增加,此后存在一个最优的垂直沟道高度值,建议在1μm左右。

图5 不同垂直沟道高度的转移特性曲线

5 结束语

新提出的HOSC-HSB-BTFET,与HSB-BTFET相比,表现出更高的开态电流和更低的反向漏电流,传输特性要好得多。通过比较HOSC-HSB-BTFET在不同垂直沟道高度下的传输特性,并分析在不同垂直沟道高度下的电流密度,可以得知随着垂直沟道高度的增加,器件具有更高的开态电流。HOSCHSB-BTFET可以实现较高的开态电流、较低的反向偏压栅致漏电流、较低的亚阈值摆幅和较高的开关电流比,具有优越的性能表现和较高的应用价值。