龙芯处理器服务器芯片组的适配与实现

2022-06-16郑臣明姚宣霞郑雪峰杨晓君

郑臣明,姚宣霞✉,周 芳,郑雪峰,杨晓君,戴 荣

1) 北京科技大学计算机与通信工程学院,北京 100083 2) 海光信息技术股份有限公司,北京 100193 3) 中科曙光信息产业成都有限公司,成都 610213

集成电路是国家信息产业发展的核心领域,而CPU(中央处理器)则是集成电路中的核心元器件.目前国家对信息安全有着迫切的要求,如果没有CPU的国产化与自主化,国家安全将无从谈起[1−2].龙芯CPU、飞腾CPU、申威CPU是目前被国家认可的、应用领域比较广的三款自主可控CPU[3−5].“龙芯”处理器是龙芯中科技术有限公司自主研发的通用CPU.“飞腾”处理器是飞腾信息技术有限公司开发的飞腾系列高性能通用CPU.“申威”处理器由国家高性能集成电路(上海)设计中心自主研发,具体由江南计算所研制实施.上述处理器都得到了国家“863”、国家科技重大专项“核高基”(核心电子器件、高端通用芯片及基础软件产品)等项目[6]的支持,在党政、关键基础设施、高性能计算等领域已得到了大量的应用,从应用的结果来看,飞腾[7−8]、申威[9−10]、龙芯[11]性能表现不错,可以胜任目前绝大部分应用[12].

这三款CPU性能不错,如以申威CPU研发的神威·太湖之光超级计算机在2021年中国高性能计算机(HPC)TOP100排行榜中位列第 2 名[13],但存在一个较大的短板,即缺乏与其配套的高性能芯片组,特别是在服务器领域,虽有强大的大脑,但无强壮的躯干和四肢,严重地限制了CPU高性能的发挥、应用领域的拓展和产业化进程.在服务器产品上,飞腾和申威CPU采用PLX公司的PCIE(Peripheral component interconnect express) 交换芯片作为北桥,例如飞腾的腾云S2500 CPU推荐的参考设计采用型号为PEX8764的PCIE交换芯片,申威的1621 CPU推荐的参考设计采用型号为PEX8748的PCIE交换芯片,利用这些PCIE交换芯片转换出更多的PCIE总线,再外接具有PCIE接口的SAS(Serial attached SCSI,其 中SCSI:Small computer system interface) /SATA(Serial advanced technology attachment)控制器 (例如 Marvell公司的88SE9215)生成硬盘接口;再外接具有PCIE接口的显卡芯片产生显示器接口等.此种芯片组的方案是迫不得已的拼凑方案,缺点是为了得到所要的 IO(Input output)接口而需要通过多级串联不同种类芯片的方式来实现,稳定性和兼容性很差,信号延迟增大,性能变差.

与龙芯CPU相配套的芯片组,最初有PCI(Peripheral component interconnect)接口桥片方案[14],但PCI总线速度太低,已逐渐被淘汰,然后有龙芯2H方案[15],但龙芯2H桥片性能太弱,只有4 对PCIE信号线和2个SATA接口,而且龙芯2H其实是一款嵌入式CPU,在龙芯CPU无桥片可用的情况下把它作为桥片是不得已而为之.在2017年底,龙芯中科技术有限公司又推出了龙芯7A1000桥片[16]作为龙芯处理器的配套芯片组.龙芯7A1000桥片通过 HT(Hyper transport)总线接口与龙芯 CPU相连,接口包括32个PCIE2.0通道、3个SATA2.0通道、6个USB(Universal serial bus)2.0 接口,可以满足桌面领域对IO接口的应用需求.但龙芯7A1000桥片在IO数量、RAS(Reliability可靠性、Availability可用性、Serviceability可维护性)和IOMMU(Input/output memory management unit,输入输出内存管理单元)等方面的不足难以满足服务器芯片组的苛刻要求.

本文针对龙芯CPU的特点,基于目前市场上现有的芯片组,筛选适配出一套高性能的芯片组来满足龙芯CPU在服务器级别上应用.由于所要筛选的芯片组不是专为龙芯CPU设计的,所以在龙芯CPU和芯片组适配嫁接过程中,需要解决在物理信号定义、上下电时序、信号协议、BIOS(Basic input output system)层等方面的差异.本文为此设计了一套筛选芯片组的架构,提供CPU和芯片组两者之间在物理信号连接、上下电时序、规避信号协议差异方面的设计方法,增加调试的灵活性和信号裕度,能够简单、反复地调整参数和设计,求证芯片组的可用性和兼容性,为龙芯CPU很便捷地找到服务器级别的芯片组.

本文的主要内容如下:

(1)基于目前市场上现有的芯片组,提出了一种为龙芯CPU筛选适配芯片组的架构,此架构同样适用于其他缺少配套芯片组的国产CPU.

(2)提出了一种CPU和芯片组两者之间在物理信号连接、规避信号协议差异方面的设计方法,为在适配过程中暂时不知如何处理的物理信号找到正确的连接方法或者处理方式.

(3)提供了一种灵活调试主板上下电时序的方法,在不修改硬件的条件下,可以随意调整CPU、芯片组、电源之间的时序,直到找到正确的上下电时序为止,节省了大量研发时间和成本.

(4)为龙芯CPU找到了一组高性能的服务器级别的芯片组,改变了一直采用低性能、嵌入式/桌面级芯片组充当服务器芯片组的局面,更好地发挥龙芯CPU性能,拓宽龙芯CPU的应用领域,进一步促进龙芯CPU生态环境的发展.

1 龙芯 CPU 和芯片组适配的架构设计

CPU和芯片组适配的常规方法[17−18]是做一块主板把两者直接连接起来进行调试,但这种调试方法存在明显的缺点.在适配不成功时很难判断是由于芯片组和CPU两者之间的不兼容引起的,或者本来两者兼容只是没有正确连接处理引起的,还是由于CPU或芯片组的缺陷引起的,原因不容易定位.即使原因定位了,由于主板不能修改,特别是由CPU或芯片组的设计缺陷造成的适配成功,在不可更改硬件的情况下不得不重新设计主板、修改CPU或者芯片组的设计,浪费了大量时间和成本.

在芯片研发设计中,为了降低研发风险,缩短研发周期,避免多次流片产生的高额成本,通常都会在芯片流片加工之前进行充分的仿真模拟.目前常用的仿真模拟方法有三种,基于软件仿真模拟验证的传统方法[19],基于硬件仿真加速器的仿真模拟验证方法[20],以及基于现场可编程门阵列(FPGA)的原型验证方法[21].基于软件仿真模拟验证的传统方法,灵活性强,使用简单,但随着逻辑单元规模的增大模拟验证速度下降明显,一般只能达到几十赫兹(Hz),与现在达到上吉赫兹(GHz)系统相差甚远,并且软件模拟仿真与真实的物理环境有差距,存在许多难于发现的问题.基于硬件仿真加速器的仿真模拟验证方法,运行速度能达到几兆赫兹(MHz),其运行速度比基于软件仿真模拟验证的传统方法提升了上千倍,但仍然达不到上吉赫兹的要求,并且此方法专用性强,维护成本高[22−24].基于FPGA的原型验证方法相对于其他两种方法,FPGA的运行速度可以达到百兆级别,而且逻辑资源、IO资源比较丰富,能够更加真实地模拟真实芯片的行为,一旦系统模拟成功,可以采用硬件拷贝(Hardcopy)方式直接快速地固化为ASIC(Application specific integrated circuit)芯 片.FPGA具有非常灵活的在线编程特点[25−26],在不改变硬件的情况下能够反复地修改代码改变硬件行为[27−28],能模拟出目前常见的IO接口和复杂的总线[29−31]、能灵活地变换不同时钟频率、能调节改变信号的电平,并内含在线逻辑分析仪功能[32].本文利用FPGA这些优势,在龙芯处理器和芯片组之间串联一颗FPGA芯片,每组芯片组通过FPGA芯片后再和龙芯处理器相连,如图1所示,这样可以在一块主板上实现多组芯片组和龙芯处理器的适配,既增加了适配成功的几率又节省了成本.

图1 龙芯 CPU 和芯片组之间的适配架构Fig.1 Adaptation architecture between Loongson CPU and chipsets

基于FPGA的原型验证方法,传统的使用方法是只模拟验证单一架构/单一功能,如果模拟多架构/多功能需要使用多块FPGA互联来实现.本文对其进行了改进,在FPGA内部模拟划分了三个不同的功能模块,利用一块FPGA芯片来实现,并且通过设计带宽匹配模块(Bandwidth matching module)实现不同频率、不同带宽总线的自协商、自适应,内嵌逻辑分析仪(Logic analyzer)可以做到实时调试分析,加快研发调试进度.

FPGA内部分为三个功能域:HT总线[33−34]处理域、重要暂不确定控制信号线处理域和CPLD(Complex programmable logic device)功能域,如图2所示.

图2 FPGA 内部总体架构图Fig.2 Overall architecture of the FPGA

HT总线处理域用于处理龙芯CPU和芯片组之间HT总线的适配.通过采用第三方或者按照HT总线协议自行编写HT总线的IP核,在FPGA上实例化HT总线接口,用来分别连接龙芯CPU和芯片组的HT总线.由于FPGA的运行速度一般在几百兆赫兹,而HT总线频率可达上吉赫兹,所以在FPGA内设计协议转化模块(Protocol converting module)把HT总线的高速串行信号线转化为较为低速的并行内部总线,然后连接到交叉开关总线(Crossbar bus)上.交叉开关总线可以通过软件控制选择切换任意一组芯片组和龙芯CPU建立HT总线互联,实现在一块主板上能同时调试适配多款芯片组,十分灵活.由于芯片组和龙芯CPU有可能存在HT总线差异,例如有的是HT 2.0总线协议(最高工作频率可达 1.4 GHz),或者HT 3.0 总线协议(最高工作频率可达 2.6 GHz),需要在FPGA内部设计一个带宽匹配模块,自动协商解决两者之间带宽差异问题.

龙芯CPU有一些独属于自己的信号线,在即将要适配的芯片组里也有一些特殊的信号线,由于芯片组不是专门为龙芯CPU配套而设计的,在未适配成功前,有些信号是不知道如何连接或者处理的.本文把这些信号线命名为“重要暂不确定控制信号线”,将其全部引入FPGA内部设置的“重要暂不确定控制信号线处理域”,借助于FPGA灵活编程的特性,可以在FPGA内部把两者的信号连接起来,或者单独地做上拉、下拉、悬空等处理.通过反复地实验和调试,总能找出“重要暂不确定控制信号线”的处理方式,给出到底能否兼容的结论.

龙芯CPU和芯片组都有自己的上下电控制时序,彼此之间怎样配合也是未知的.上下电时序信号主要包括三部分:CPU上下电控制信号,芯片组上下电控制信号、电源模块上下电控制信号.这三部分信号都需要引入FPGA内部设置CPLD功能域.在主板设计中,常采用CPLD芯片来控制整个主板的上下电时序,本文采用在FPGA内部分离出一部分逻辑资源实现一个CPLD功能域,依靠CPLD来调整三部分的上下电时序来达到CPU和芯片组协调工作的目的.通过反复地实验和调试,找出相互配合工作的最佳时序或者给出无法兼容的结论.

在龙芯CPU和芯片组适配的过程中,通过本架构可以实现如下功能或优点:

(1)一块主板可以适配多款芯片组(同一时间只能实现一款芯片组和CPU互联),不用再为每种芯片组单独研发一种主板,节省了研发不同主板的时间和成本.

(2)通过FPGA的隔离,能有效地屏蔽CPU和芯片组在HT总线方面的差异,例如协议版本的不同、信号线差异,甚至HT设计的缺陷.通过FPGA补偿龙芯CPU和芯片组的HT总线差异或缺陷,使两者无缝地连接起来,而不会因为HT总线的差异使适配过程半途而废,所以此架构具有很大的灵活性,节省了时间和成本.

(3)无论龙芯CPU还是芯片组在未适配成功前,那些无法确定怎样连接或者处理的信号线通过FPGA可以实现任意连接或处理,增加了调试的手段,当找出确定的处理方式后,可指导下一版龙芯CPU、芯片组或者主板的改进.

(4)CPU和芯片组两者的上下电时序配合通过FPGA编程来灵活的调节时序和时间间隔,可以实现任意的组合尝试,增强了调试的灵活性.

2 龙芯 CPU 和芯片组适配的实现过程

2.1 芯片组的选择

根据龙芯CPU的特点,在理论上推断目前市场上有如下的芯片组可与龙芯CPU进行适配实验:

(1)矽统科技(SiS)公司的芯片组,北桥芯片型号SiS761GX,南桥芯片型号SiS968;

(2)英伟达(NVIDIA)公司的芯片组,型号MCP68;

(3)AMD公司的芯片组,北桥芯片型号M690T,南桥芯片型号SB600;

(4)AMD公司的芯片组,北桥芯片型号RS780E,南桥芯片型号SB710;

(5)AMD公司的芯片组,北桥芯片型号SR5690,南桥芯片型号SP5100.

龙芯CPU和即将要适配的芯片组按照图1的架构设计一块主板试验品,龙芯CPU采用子板的方式与芯片组主板互联,试验品实物图如图3所示.主板上包含了如上五种芯片组和FPGA,并把PCIE、USB、GPIO(General purpose input/output)、控制线等信号线引入到相应的连接器上.

图3 包含 FPGA 和各种芯片组的主板Fig.3 Motherboard sample containing the FPGA various chipsets

FPGA 采用 Intel Stratix 10 GX 2800 系列(简称GX 2800),具体型号为 1SG280HU2F50E2LG.FPGA选型主要从“可编程IO单元”和“可编程逻辑单元”两个方面考虑.在可编程IO单元方面,龙芯CPU和五种芯片组共有6组HT总线,其中芯片组1和芯片组2的HT总线速率最高为1 GHz,龙芯CPU和芯片组3、芯片组4、芯片组5的HT总线速率最高为2.6 GHz,每个HT总线有20对差分信号线,所以FPGA需要提供40对可达1 GHz高速串行信号线和80对可达2.6 GHz高速串行信号线.因为 GX 2800 具有 576 对可达 1.6 GHz高速串行总线和96对可达17.4 GHz高速串行总线,所以满足本设计要求.另外GX 2800可提供1160个其他类型的IO针脚,足以满足本设计的要求.在可编程逻辑单元方面,每种芯片组的HT总线和协议转换模块大约需要9万个可编程逻辑单元,龙芯CPU和五种芯片组大约共需54万个;交叉开关总线和带宽匹配模块大约需要12万个可编程逻辑单元;重要暂不确定控制信号线处理域大约需要4000个可编程逻辑单元;CPLD功能域大约需要3000个可编程逻辑单元,所以共需大约67万个可编程逻辑单元.GX 2800具有93.3万个可编程逻辑单元,本设计资源利用率大约在72%,所以完全满足本设计的资源需求.

2.2 信号线的设计处理

2.2.1 HT 总线的设计处理

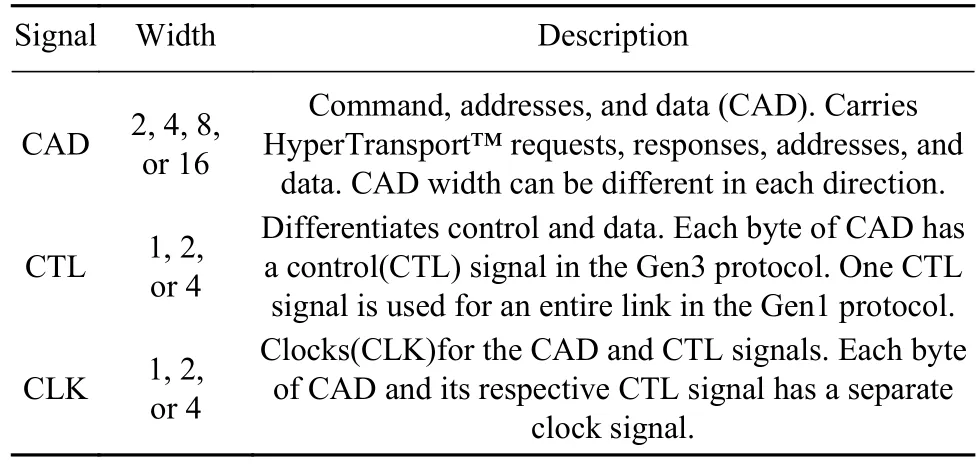

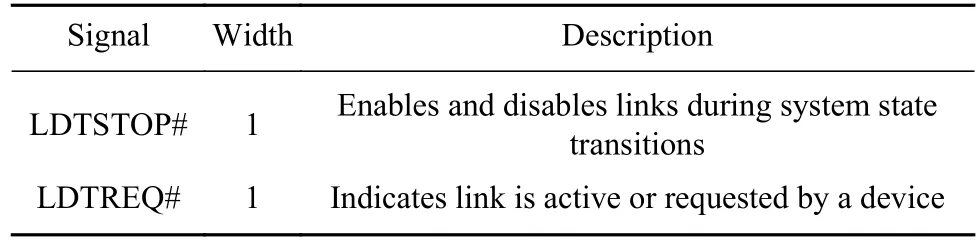

标准的HT总线协议包括三类信号线:连接信号线(数据、地址、控制和时钟)(表1)、复位和初始化信号线(表2)和电源管理信号线(表3).

表1 HT 总线的连接信号线Table 1 Hyper transport bus link signals

表2 HT 总线的复位/初始化信号线Table 2 Reset/Initialization signals of the HT bus

表3 HT 总线的电源管理信号线Table 3 Power management signals

对于连接信号线,龙芯CPU和上面所提到的芯片组(或北桥)都有16对接收差分信号线,16对发送差分信号线;2对接收信号时钟差分对,2对发送信号时钟差分对;2对接收控制信号差分对,2对发送控制信号差分对.两者的HT总线连接信号线都直接引入FPGA内部的HT总线域进行处理,需要注意的是不同型号的龙芯CPU和所选择的芯片组遵循HT协议版本不同,有的是HT2.0协议,有的是HT3.0协议,即使都支持HT3.0协议,也存在 1.8、2.0、2.4、2.6 GHz四种频率等级,所以在适配的过程中需要采用带宽匹配模块进行调整.

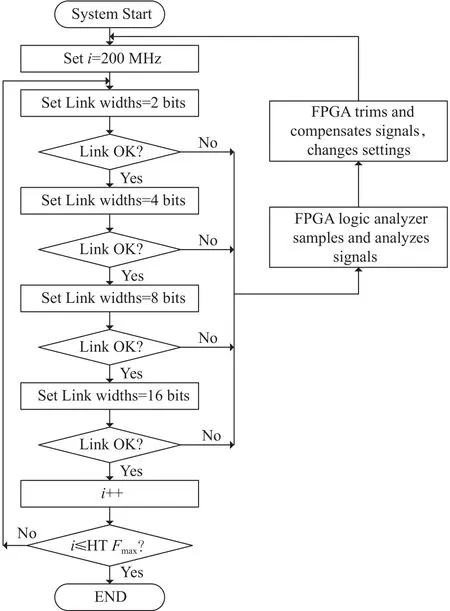

在实际的适配中,利用FPGA内部设置的交叉开关只需连接龙芯CPU和所要适配芯片组的HT总线,而断开其他芯片组连接.HT总线调试采取频率、通道数从低到高逐步增加的步进调节方法.HT 可支持 2、4、8和16 位(bit)四种通道模式,HT协议的最低工作频率可低至200 MHz,HT2.0协议支持最高频率为1.4 GHz,HT3.0协议支持的最高频率为 2.6 GHz.

HT调试流程如图4所示,在HT调试过程中,先固定工作频率,从最低的2位通道数进行调试,如果适配成功,就依次增加通道数继续调试,即按照2位、4位、8位、16位顺序调试.如果适配不成功,就利用FPGA内部的逻辑分析仪采样信号进行分析,修正补偿相应的信号线后,再重新进行适配.HT总线频率调试顺序依次为200、400和800 MHz,一直到芯片工作最高频率(Fmax).

图4 HT 总线调试流程Fig.4 Flow of the HT bus debug

通过如上HT总线的适配,可以确定信号的正确连接方式或者处理方法,能够定量地找出CPU和芯片组的 HT总线在主板 PCB(Printed circuit board)设计中信号线的最佳分组方式、长度限制、线宽限制、相邻信号线的间距限制,能够找出两者之间HT总线的最佳工作频率甚至下一版芯片设计中需要修改的错误或者改进之处.

利用如上的HT调试流程分别对如上五种芯片组进行调试,结果表明,第一种和第三种芯片组可以调试成功的最高频率是800 MHz,第二种芯片组在达到HT总线400 MHz时出现不稳定的现象,第四种和第五种可以达到2.0 GHz HT总线频率.第四种芯片组,即 RS780E + SB710 组合,PCIE 总线有22对信号线,不支持服务器领域要求的RAS特性,但成本低,所以非常适合作为龙芯的桌面芯片组.第五种芯片组 SR5690 + SP5100,拥有42 对PCIE信号线、14个USB接口,具有强大的IO能力,并支持RAS特性,所以可以得出在服务器领域与龙芯CPU适配成功的最高端、最适合的芯片组为 SR5690 + SP5100.在本文后面的其他章节中,在阐述芯片组适配与实现的通用原理和方法后,为了文章的简洁,主要以 SR5690 + SP5100芯片组进行阐述.

2.2.2 重要暂不确定控制信号线的设计处理

龙芯CPU的HT总线由于其独特的设计比标准的HT总线协议多出了一些额外的、特殊的信号,所以在硬件层和协议层需要正确地处理这些特殊信号.既不能影响龙芯CPU自身正常工作,又能和芯片组无缝的兼容,这是一个比较关键的技术点.在标准的HT总线协议中,信号PWROK、RESET#、LDTSTOP#、LDTREQ#(表2和表3)只有一组,而龙芯HT 总线接口信号有两组,一组是HT_HI_POWEROK、HT_HI_RSTn、HT_HI_LDT_STOPn、HT_HI_LDT_REQn,另一组是HT_LO_POWEROK,HT_LO_RSTn、HT_LO_LDT_STOPn、HT_LO_LDT_REQn.龙芯CPU和芯片组还有其他各自特殊的信号线,无法直接确定两者之间的对应关系.以上这些重要暂不确定控制信号线都引入FPGA,如图1和图2所示.

这些信号如何处理,怎样和北桥、南桥互连在未适配成功前是不清楚的,但可以依靠FPGA在其内部灵活地处理,例如连接、断开或者采用某种终端方式来反复地实验调试,直到找到某种确定的处理方式或者结论为止.经过本文的实验,对于适配成功的芯片组SR5690 + SP5100和龙芯CPU在HT总线上可以找到如下正确的连接方式,如图5所示.

图5 HT重要暂不确定控制信号线经适配证明后找到的正确连接方式Fig.5 Appropriate connection of the important but temporarily indeterminate HT signals after effective adaptation

2.2.3 上下电控制信号线的设计处理

在无法得知龙芯CPU和芯片组的上下电时序如何配合的情况下,需要把CPU上下电控制信号、芯片组的上下电控制信号、电源模块的控制信号线都引入FPGA.这些信号线主要包括:(1)龙芯CPU的系统复位信号线SYSRESETN,PCI总线的复位信号线PCI_RESETN;(2)南桥的上电完成信号线PWR_GOOD,北桥的上电完成信号线NB_PWRGD;(3)各个供电模块的上电使能信号线和电源完成信号线PWRGOOD;(4)龙芯CPU的GPIO配置信号线,内存时钟频率的设置信号线,HT总线时钟频率的设置信号线等.

用FPGA使能或者关闭电源模块的使能信号、龙芯CPU和芯片组的电源完成信号、复位信号线,并调整各个电源控制信号的先后顺序和时间间隔进行反复实验,一直尝试到得到确定的答案为止,或者能找到最佳的电源时序适配方案,或者证明两者无法兼容.

芯片组 SR5690 + SP5100 是本文适配成功的芯片组,图6是为其找到的已经验证成功的上下电时序,包含的信号有正 5 V standby 电源+5VSB,正 3.3 V standby电源+3.3V_DUAL,FPGA的开机信号线FPGA_SB_RSMRST#,南桥的上电信号线SB_PWRON,系统唤醒信号线 SLP_S3#_R,12 V供电信号线 12V_SLP_S3#,ATX(Advanced technology extended)电源上电正常指示信号线ATX_PWRGD,北桥 1.8 V电源 NB_1V8,CPU的 1.2 V 电源 CPU_NB_SB_1.2V,北桥 1.1 V 电源 NB_1V1,CPU 的 1.1 V电源 CPU0/1_VCCINT_1V1,CPU内存的 1.5 V电源CPU0/1_1.5V_LS3_DDR3,系统上电正常指示信号线SYS_PWRGD,北桥上电正常指示信号线NB_PWRGD,FPGA的复位信号线 FPGA_KBRST_L,龙芯HT总线上电正常指示信号线LS3_HT1_LO_POWEROK,南桥复位信号线SB_A-RST_L,南桥PCI总线复位信号线SB_PCI_RST_SR_L,系统复位信号线SYSTEM_RST,以及CPU HT的复位信号线CPU_LDT_RST.为了进一步验证上下电时序的正确性和可靠性,采用两种方法进行验证.

图6 经适配证明后找到的正确电源时序Fig.6 Correct power sequence after effective adaptation

在 ACPI(Advanced configuration and power interface)规范中规定了计算机系统的7种状态:G3(Mechanical off,即彻底切断所有电源,包括外置电源),S0(工作状态,即所有设备都运行),S1(CPU关闭工作状态,其他的部件仍然正常工作),S2(CPU停止工作状态,其他的部件仍然正常工作),S3(除了内存外的部件都停止工作),S4(内存数据写入硬盘后所有部件都停止工作状态)和S5(关机状态,只有standby电源存在).对于服务器系统来说,其中必然经历三种状态,即G3、S5、S0.鉴于此,龙芯 CPU 和芯片组 SR5690 + SP5100组成的服务器系统从启动到运行过程中,通过调试工具在G3、S5和S0状态读取龙芯CPU和芯片组的寄存器值,和产品文档中标准值进行对比从而验证上下电时序的正确性.测试表明,图6设计的上下电时序是正确的.

另一种方法是采用服务器产品化过程中常用的电源循环压力测试方法:AC Power on/off cycle test和DC Power on/off cycle test.AC Power on/off cycle test,是交流电循环上下电测试,从G3到S0再到G3再到S0不间断循环1000次,如顺利完成则表明系统设计的正确性和可靠性.DC Power on/off cycle test,是直流电循环上下电测试,从S0到S5再到S0再到S5不间断循环1000次,如顺利完成则表明系统设计的正确性和可靠性.压力测试表明,图6所示的上下电时序顺利完成了1000次循环压力测试,达到了产品化的目标.

2.3 龙芯服务器产品的设计

当找到能够正确适配龙芯CPU的芯片组后,在实际的龙芯服务器产品设计中,去掉中间FPGA,按照适配好的规则直接把龙芯CPU和适配成功的芯片组连接起来.

在适配过程中已经总结出物理信号线的正确连接或者处理方式、正确的上下电时序、最佳的HT工作频率、确定的PCB布线规则(如线长、线宽、线距)和信号完整性的正确处理方式等设计要点.在龙芯服务器产品设计中只需遵循已总结出的这些设计要点按照常规主板设计的方法进行设计就可以了.

图7是根据以上总结得出的设计规则去掉FPGA后设计的龙芯服务器主板实物图.此龙芯服务器主板采用龙芯双路SMP(Symmetrical multiprocessing)架构设计,芯片组是 SR5690 + SP5100,已经实现了产品化,稳定性好,性能高.

图7 SR5690+SP5100 龙芯双路服务器产品主板Fig.7 Loongson two-way SMP motherboard product using SR5690 + SP5100 chipsets

3 讨论

本文设计的筛选芯片组的架构和方法具有很强的通用性,不但从如上五种芯片组中筛选出服务器级别的 SR5690 + SP5100 芯片组,能够完全适配龙芯CPU,而且利用此架构和方法在其他的研究项目中也成功筛选出多种适用于龙芯CPU的桌面级别芯片组和服务器级别芯片组,对于桌面级别芯片组,例如北桥芯片型号有RX781、RS785G、RD790,南桥芯片型号有SB700;对于服务器级别芯片组,例如北桥芯片型号有SR5650、SR5670,南桥芯片型号有SB750.对于这些已经成功筛选出的芯片组,用户可以根据其功能、性能、成本等综合因素选择高性价比的芯片组来使用,极大地拓宽了龙芯CPU的使用领域,促进了龙芯的产业化.

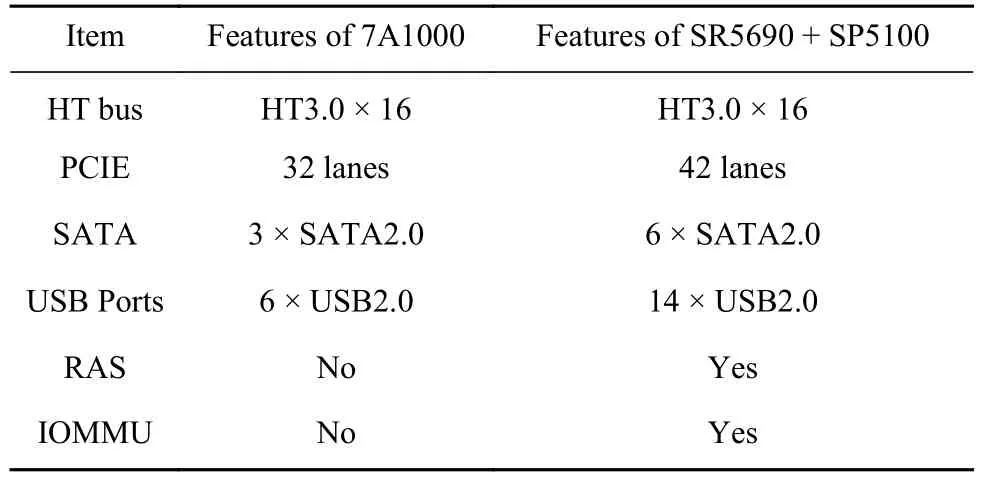

SR5690 + SP5100芯片组功能丰富、性能强大,完全可以作为龙芯CPU服务器级别的芯片组使用,其和目前龙芯中科技术有限公司推出的龙芯7A1000桥片在规格参数上的对比如表4所示.

表4 芯片组规格对比Table 4 Comparison of different chipset specifications

高IO带宽、支持IO虚拟化的IOMMU功能和支持RAS功能是目前服务器所应具备的基本要求.从这三种芯片组规格的对比来看,芯片组SR5690 + SP5100的IO带宽特别是 PCIE数量远大于龙芯7A1000桥片,SATA和USB数量也远大于龙芯7A1000桥片,而且还支持IOMMU和RAS功能.所以,芯片组 SR5690 + SP5100 在规格参数上完全可以作为龙芯CPU的服务器芯片组.

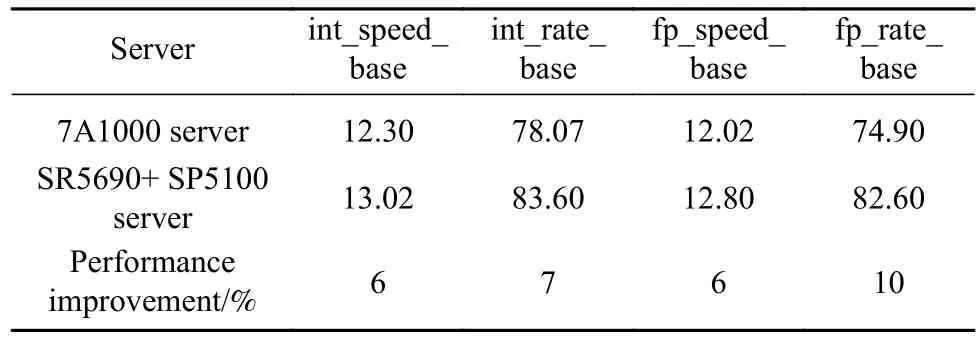

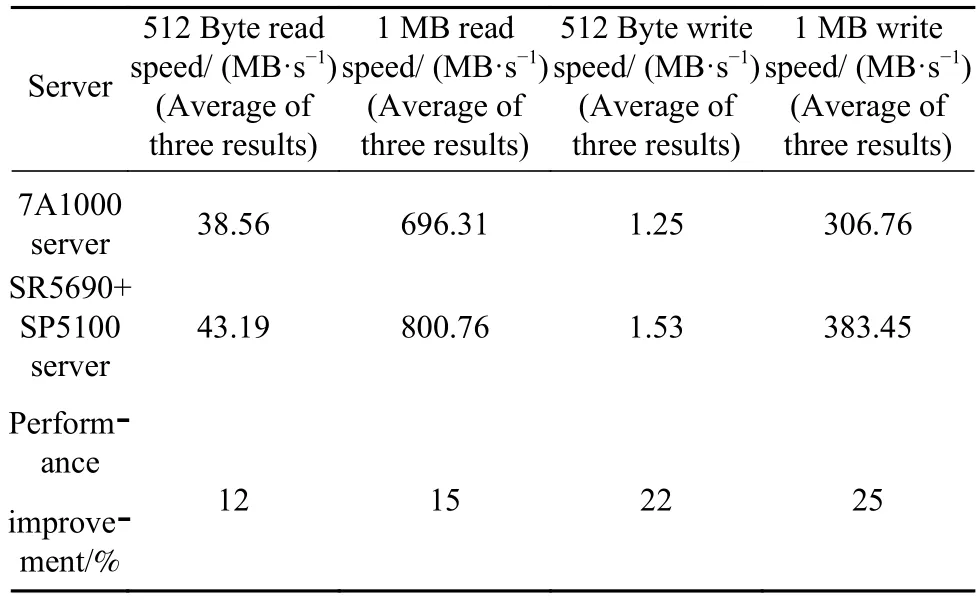

在性能方面,本文设计的 SR5690 + SP5100 双路龙芯3B4000服务器与市场上已有的双路龙芯3B4000 + 7A1000 服务器进行了实际测试对比.两种服务器都采用相同的硬件配置,即两路龙芯3B4000 CPU(主频 1.8 GHz,4 核),4 条紫光国芯 16 GB DDR4 内存(型号:SCC16GP02H1F1C-26V),4 块东芝 2 TB的 SATA硬盘(型号 MG04ACA200N),网卡采用Intel I350千兆网卡.采用国际上公认的benchmark程序进行测试,用 SPEC CPU 2006测试了CPU计算性能,单核整型性能(int_speed_base)、多核整型性能(int_rate_base)、单核浮点性能(fp_speed_base)和多核浮点性能(fp_rate_base),如表5所示;用IOzone V4.3.0测试了SATA硬盘性能,512 Byte读写性能和1 MB读写性能,如表6所示;用Netperf V2.7.0 测试了网络性能,TCP(Transmission control protocol)吞吐率、TCP 传输速度、UDP(User datagram protocol)吞吐率和UDP传输速度,如表7所示.从性能对比的数据来看,采用SR5690 +SP5100作为龙芯3B4000配套的芯片组可以较大幅度地提高龙芯CPU的性能,特别是IO方面性能,可以提高到10%以上.

表5 SPEC CPU2006 性能对比Table 5 Analysis of SPEC CPU2006 performance

表6 IOZone 性能对比Table 6 Analysis of IOzone performance

表7 Netperf性能对比Table 7 Analysis of Netperf performance

4 结论

本文为龙芯CPU设计了一种筛选芯片组的架构,给出了龙芯CPU和芯片组之间适配的方法,并设计了筛选用的容纳多套芯片组的主板,对筛选出的芯片组进行了产品化,测试了真实的运行性能.

本文筛选出的芯片组 SR5690 + SP5100 无论在 PCIE、SATA、USB、IOMMU和RAS等参数方面,还是在实际运行性能上都高于目前龙芯CPU所用的芯片组,所以非常适合作为龙芯CPU在服务器领域的芯片组,有力地开拓了龙芯CPU更多的适用领域.