弱电网下采用电容电压前馈的LCL并网逆变器谐振频率偏移抑制策略

2022-05-09杨明杨杰赵铁英郑晨韦延方

杨明, 杨杰, 赵铁英, 郑晨, 韦延方

(1.河南理工大学 电气工程与自动化学院,河南 焦作 454003;2.国网河南省电力公司电力科学研究院,河南 郑州 450052)

0 引 言

LCL型并网逆变器作为可再生能源发电单元与电网之间的关键接口设备,广泛应用于可再生能源的分布式发电系统(RE-DPGS)。LCL型输出滤波器具有较好的高频开关次谐波衰减能力,然而其固有的谐振峰将会引发并网逆变器的稳定性问题[1]。在谐振频率fres处,幅值增益为无穷大,且相频特性穿越-180°线,导致系统产生两个不稳定的正实部极点[2-3]。目前对于LCL型滤波器谐振尖峰的抑制方法主要包括无源阻尼和有源阻尼两类。其中,无源阻尼通过电路器件实现简单,却造成较大的功率损耗无法得到广泛应用[4];有源阻尼是在无源阻尼的基础上通过阻尼实现算法进行滤波器谐振尖峰的抑制,且不会产生功率损耗得到大范围推广[5-7]。文献[8-9]研究表明,通过滤波电容电流比例有源阻尼进行谐振尖峰的抑制,不会改变滤波器对开关谐波的衰减能力,该有源阻尼方法等效于在滤波电容两端并联一个虚拟电阻。

当电网呈现弱电网特性时,电网等效阻抗Zg对并网逆变器将会造成不利影响。一般来说,Zg主要表现为阻感特性,阻性分量相当于在滤波器网侧电感串联一个电阻,有利于谐振尖峰的阻尼[10];感性分量可等效于滤波器网侧电感的改变量,会引发谐振频率fres向低频偏移,降低并网逆变器的相对稳定性,且减小控制系统的带宽[11]。此外,电网中含有较多的低频次背景谐波电压,导致并网逆变器的并网电流出现明显畸变。文献[12]通过并网逆变器与电网的互联系统等效阻抗模型分析表明,电网阻抗与并网逆变器输出阻抗存在谐振极点,该谐振极点会对电网背景谐波产生放大作用,即互联系统发生谐波谐振,此时并网逆变器无法正常并网。

针对弱电网下电网阻抗与电网背景谐波对并网逆变器稳定性的影响,已有诸多学者做出研究。文献[13-14]在耦合点串并联整流设备,通过产生与电网背景谐波大小相同、相位相反的谐波源用以抵消电网阻抗与背景谐波,然而需要对整流设备附加额外的控制环路,且由于产生功率损耗而无法大规模应用于DPGS。在文献[15]中,提出一种在耦合点并联RC支路的电网阻抗调节方法,保证并网逆变器的输出阻抗始终满足基于阻抗的稳定性判据,但是降低了并网逆变器输出阻抗的大小,不利于电网背景谐波的抑制。

相较于上述改善并网逆变器性能的无源控制策略,人们更倾向于采用有源控制策略实现并网逆变器的稳定性控制。文献[16-17]通过并网逆变器系统控制框图等效变换,提出电网电压全前馈控制策略,该方法能够完全消除电网背景谐波对并网逆变器的影响,但是,当电网阻抗较大时可能导致并网逆变器无法稳定工作。在文献[18]中,提出了电网电压比例加权前馈和附加相角补偿的谐波准谐振电流控制策略,可有效提升并网逆变器的稳定性并有效抑制电网低频次背景谐波,但是会引起谐振陷阱现象,不利于系统稳定性判定。文献[19-21]通过在并网逆变器控制环路中添加相位补偿环节,可显著提升并网逆变器的相对稳定性,然而相位补偿环节大多为超前环节,对环路中的高频次谐波会产生放大作用。

因此,现有的控制方案尚存在一定的局限性,同时兼顾并网逆变器的稳定性及高质量的并网电流仍需进一步深入研究。本文通过对弱电网下并网逆变器的稳定性机理进行分析,明确了电网阻抗的宽范围变化会导致系统环路谐振频率偏移,进而造成LCL并网逆变器的稳定性下降。提出一种采用电容电压比例微分前馈的LCL并网逆变器环路谐振频率偏移抑制策略,同时采用电容电压锁相并对非单位功率因数进行相位补偿。此外,考虑数字控制延时对所提策略的影响,理论分析表明,在阻尼环为零拍延时条件下所提策略对弱电网仍具有很好的适用性。该方案可显著改善并网逆变器的相对稳定性,最后通过仿真分析和实验对所提策略的有效性进行了验证。

1 光伏并网逆变器的模型建立

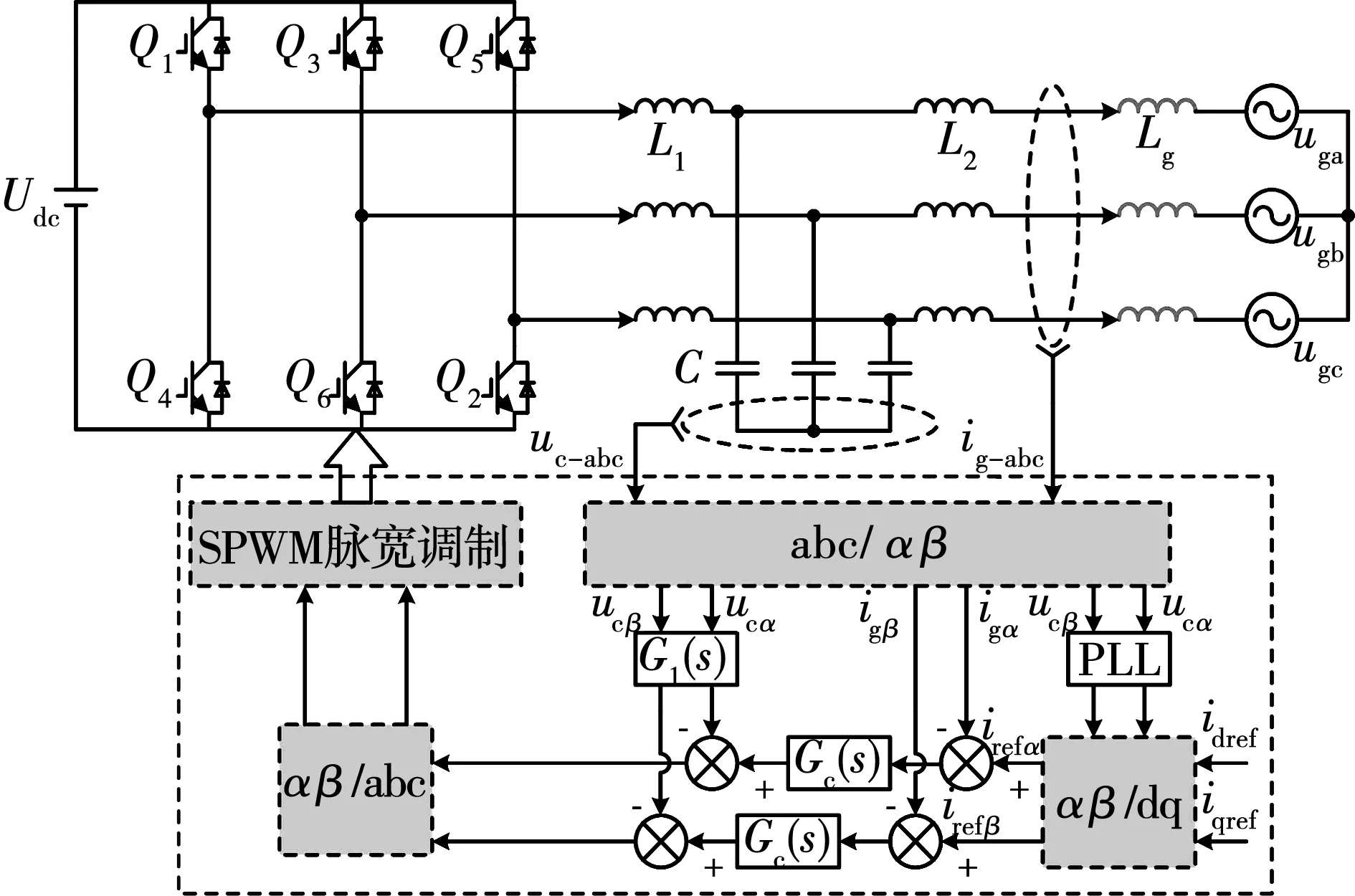

光伏并网逆变器作为发电单元与电网互联的能量传输关键接口设备,其性能优劣对入网电能质量具有较大的影响。图1为三相LCL型并网逆变器及其控制结构图,其中:LCL滤波器由逆变侧电感L1、网侧电感L2及滤波电容C组成;Udc是直流侧母线电压;Lg和ug分别为电网电感和电网电压;参考电流iref通过锁相环(phase locked-loop,PLL)获得与公共耦合点(point of common coupling,PCC)电压upcc同相位实现单位功率因数并网,idqref为给定参考电流幅值;ic和ig分别为滤波电容电流和网侧电流。

图1 三相LCL型并网逆变器结构示意图Fig.1 Structure diagram of three-phase LCL grid-connected inverter

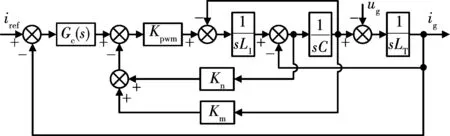

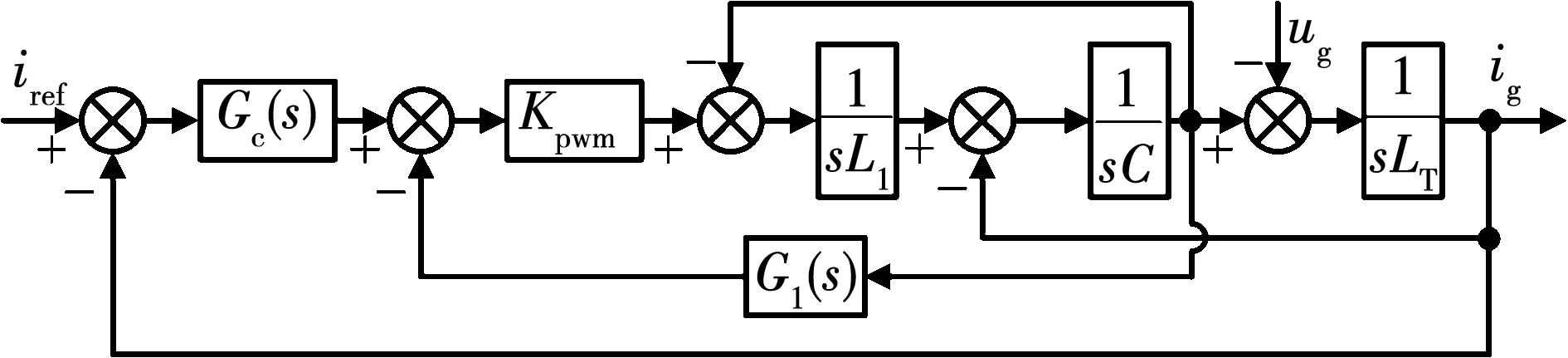

并网逆变器的系统等效控制框图,如图2所示。图2中,各状态变量均已转换至s域。Kd代表电容电流有源阻尼系数;Kpwm为三相逆变桥脉宽调制增益,且有Kpwm=Udc/Utri(Utri为三角载波幅值);LT=L2+Lg;Gc(s)代表并网电流控制器,考虑到电网电压中含有的低频奇次背景谐波会造成逆变器网侧电流发生畸变,本文采用准比例谐振(quasi-proportional resonance,QPR)控制器,以添加5、7、9次谐波补偿项为例,传递函数Gc(s)的表达式为

(1)

式中:Kp为比例系数;Krn为谐振系数,n为谐波补偿项次数;Kc为谐振宽度;ω0代表电网基波角频率,一般为314 rad/s。

根据图2可得并网逆变器的环路增益表达式,即iref(s)到ig(s)的开环传递函数为:

(2)

2 并网逆变器稳定性机理分析

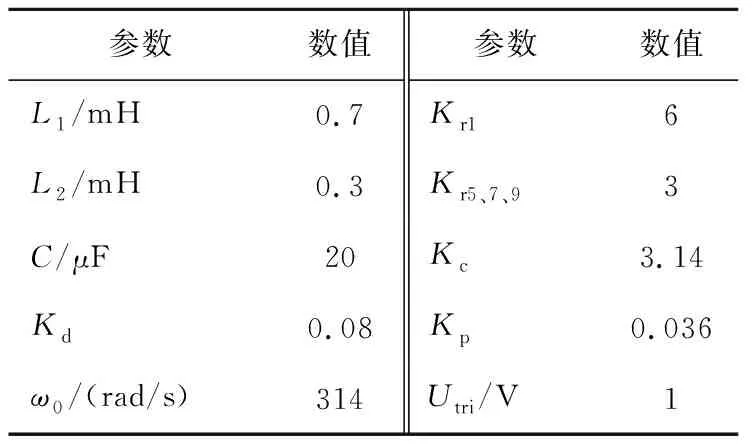

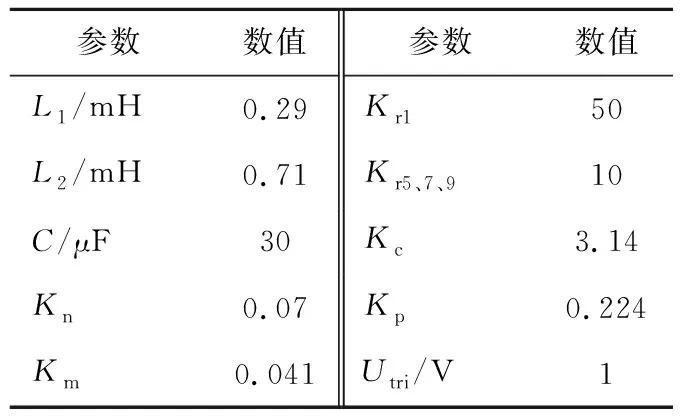

为便于后续分析,给出三相并网逆变器的相关参数:三相额定输出功率Pout=10 kW,电网相电压有效值Ugrms=110 V,直流侧母线电压Udc=350 V,开关频率fsw=10 kHz,采样频率fs=20 kHz。本节分析所用逆变器参数如表1[22]所示。

表1 并网逆变器的模型参数

当逆变器接入电网时,电网的强弱情况可以根据交流系统短路容量比(short circuit ratio,SCR)来评价。通常情况下,当SCR≤3时称为弱电网,当SCR<2时称为极弱电网。根据RE-DPGS发电标准,三相并网逆变器接入电网时,需要在SCR≥3的工况下稳定运行[11],因此本文考虑最大电网电感Lg=3.9 mH,此时SCR=3。

2.1 并网逆变器控制系统相对稳定性分析

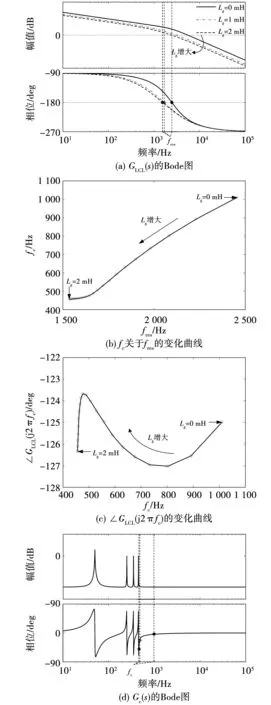

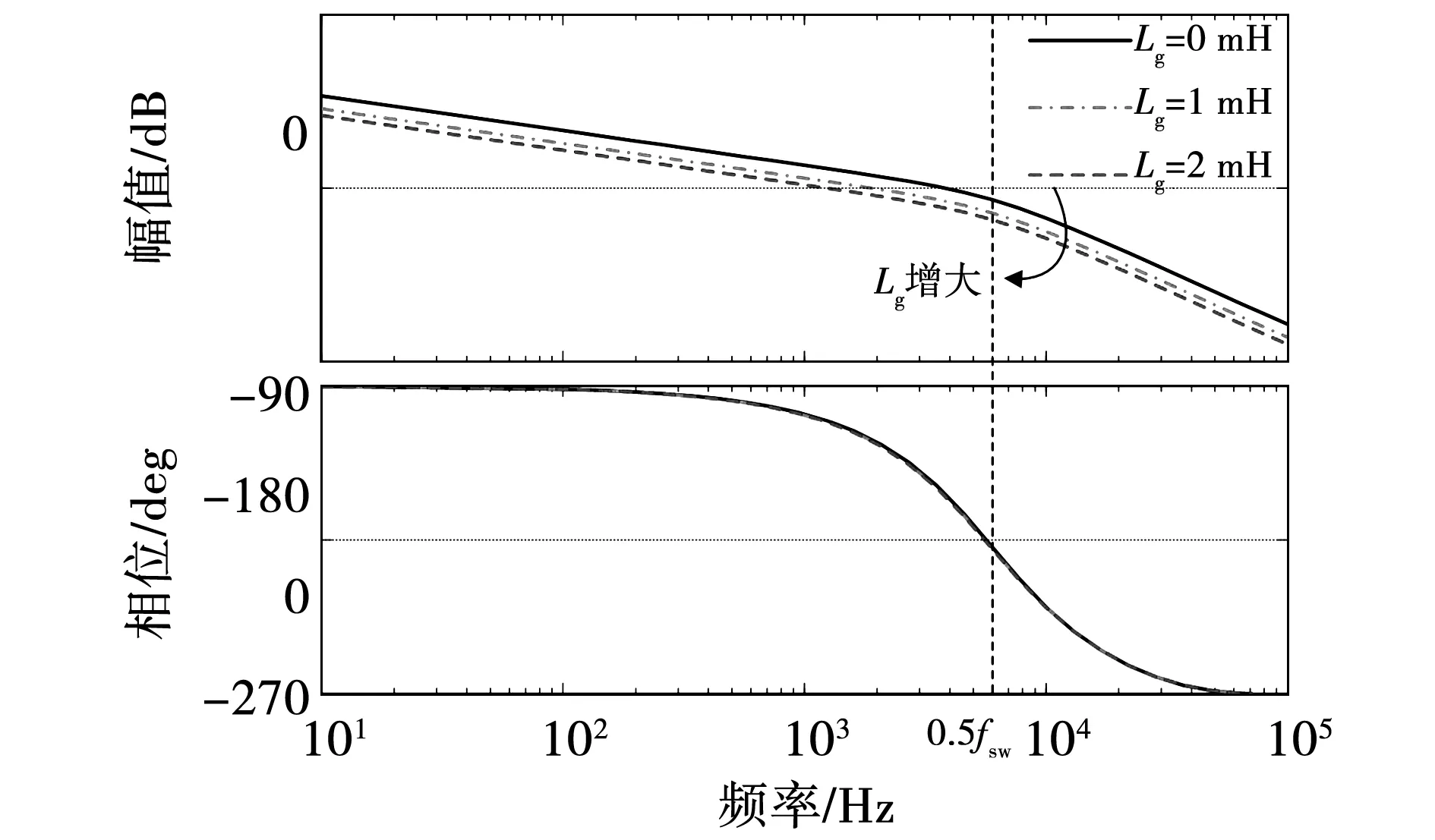

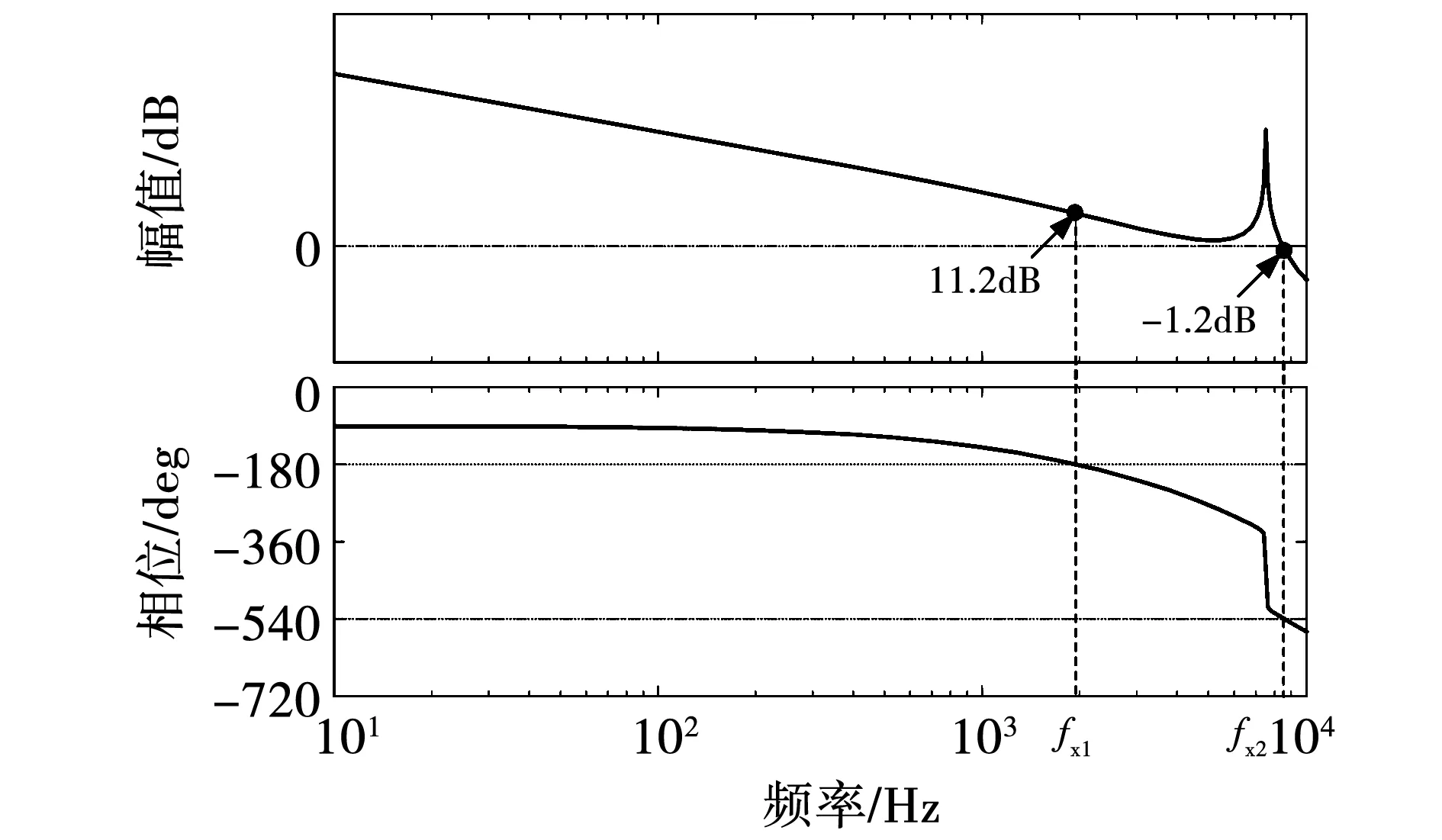

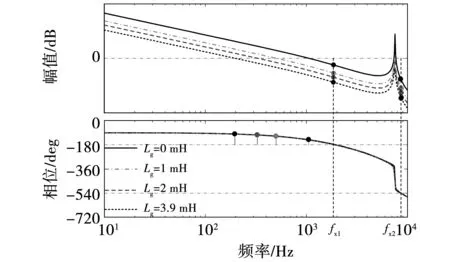

并网逆变器控制系统的环路增益表达式如式(2)所示,通过式(2)利用环路增益的幅值裕度或相位裕度指标可以判断控制系统的相对稳定性。图3为T0(s)在Lg变化时的Bode图。

图3 环路增益T0(s)的Bode图Fig.3 Bode diagrams of open-loop gain T0(s)

由图3可以看出,当Lg=0 mH时,环路增益具有PM=51°的相位裕度和fc=1 kHz的环路截止频率,均满足工程设计要求;随着Lg增加,当Lg=1 mH和2 mH时,环路增益的相位裕度逐渐减小,分别为PM=38.7°和6.56°。由此可知,随着Lg增加,环路增益相位裕度逐渐减小,弱电网下Lg的变化会降低并网逆变器控制系统的相对稳定性。

根据图2可得并网逆变器有源阻尼回路的环路增益为

(3)

其中fres代表环路谐振频率,表达式为:

(4)

由于T0(s)=Gc(s)GLCL(s),根据式(3)可知,弱电网下fres的变化会对GLCL(s)与T0(s)的频率特性造成直接或间接的影响。观察式(4)可以发现,fres是关于Lg的减函数,当Lg=0 mH时,fres具有最大值为fres0,当Lg→∞时,fres具有极小值为fres1,环路谐振频率偏移可记为

Δfres=fres0-fres。

(5)

最大环路谐振频率偏移为

Δfrmax=fres0-fres1。

(6)

图4(a)给出了GLCL(s)的Bode图。可以看出,随着Lg的增加,GLCL(s)的幅频特性曲线向中低频段偏移,导致T0(s)的环路截止频率fc减小,fc关于fres的变化曲线如图4(b)所示,并网逆变器闭环带宽降低,系统动态性能较差。

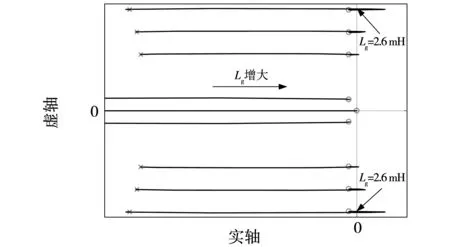

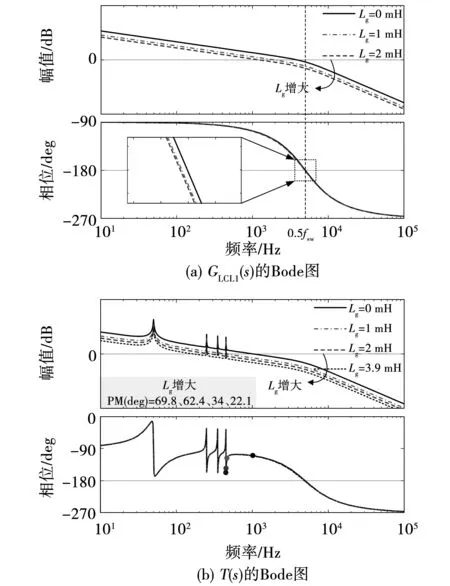

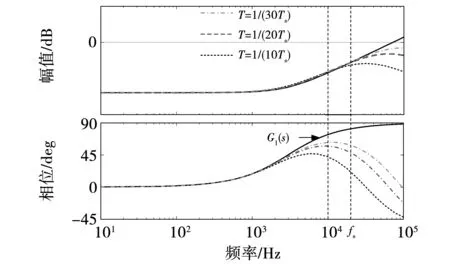

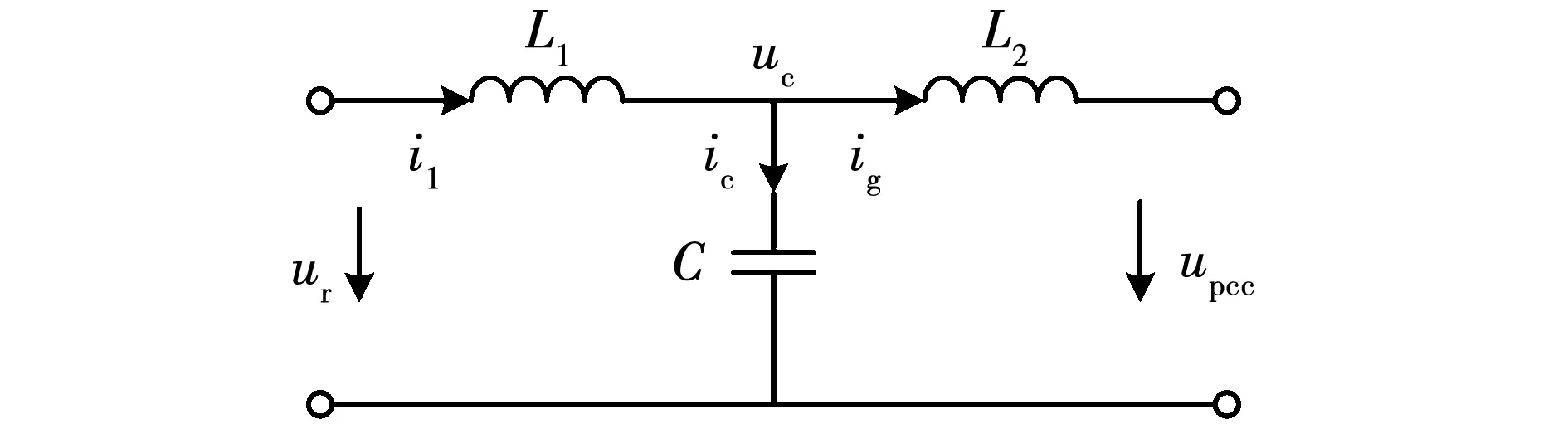

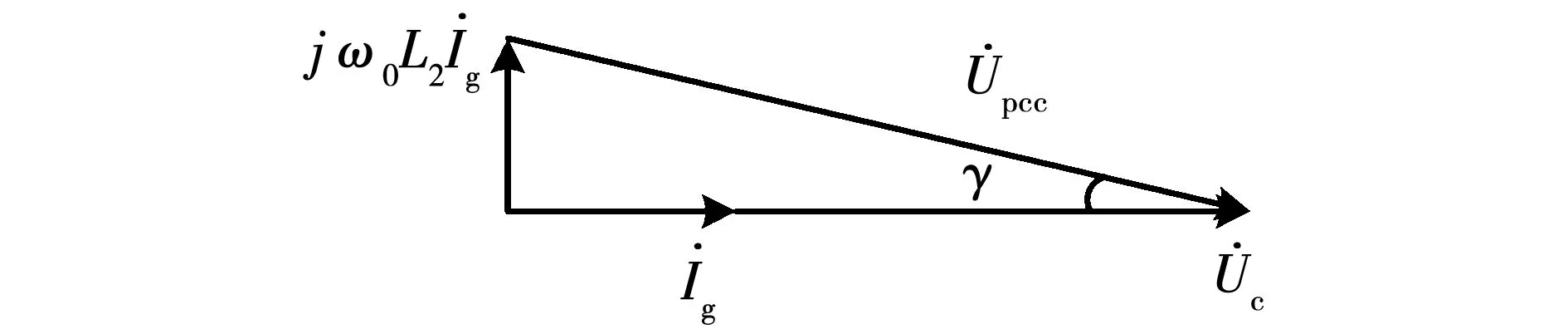

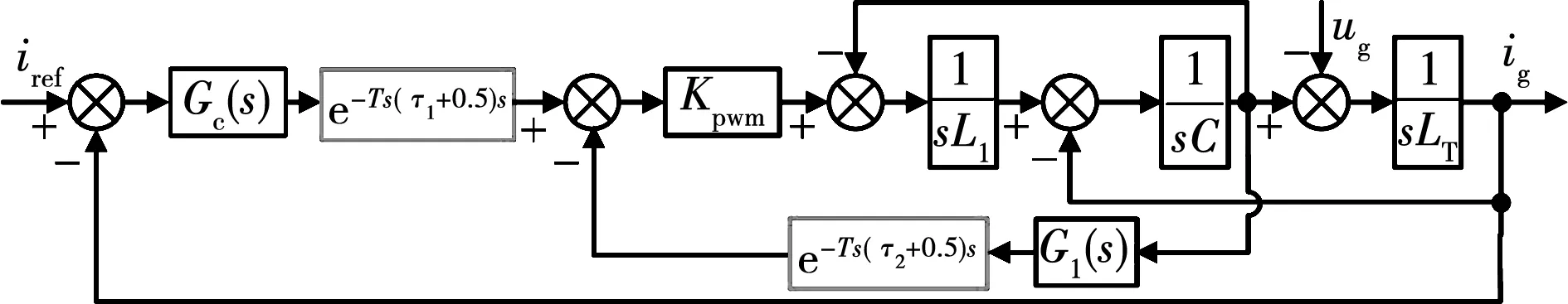

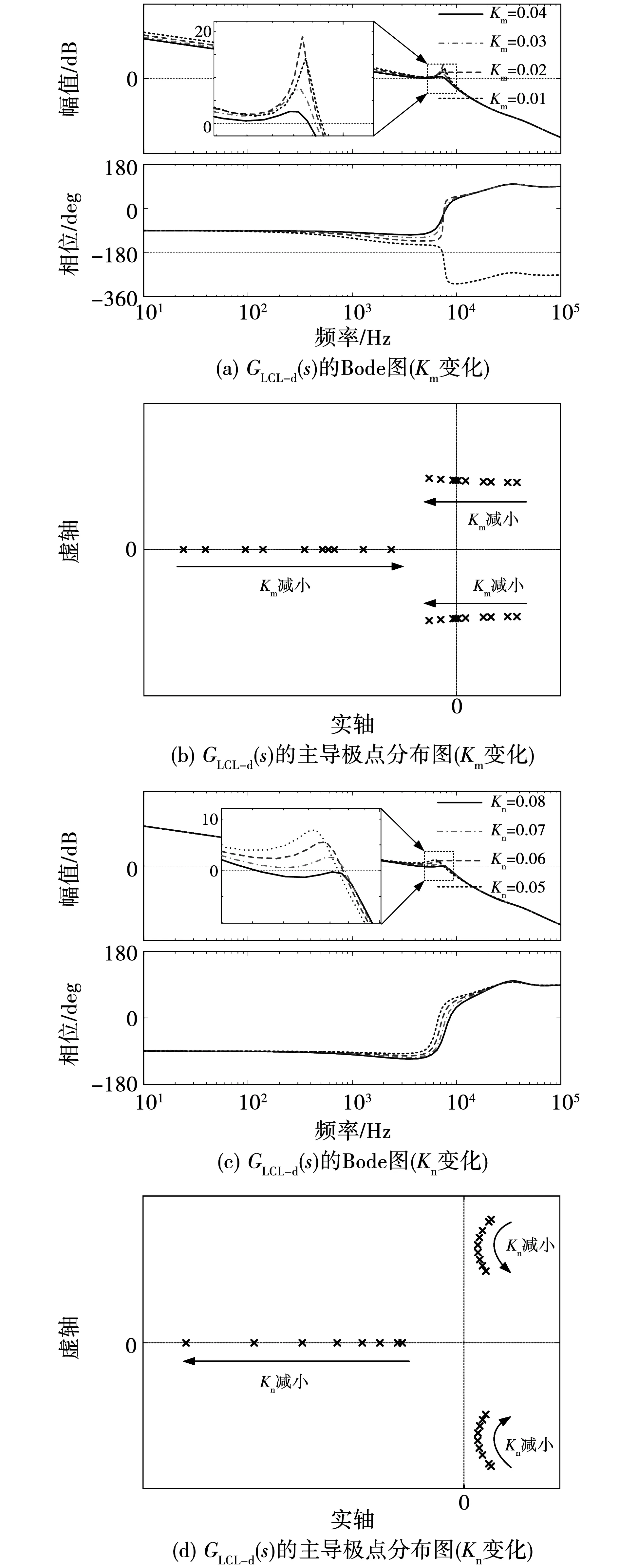

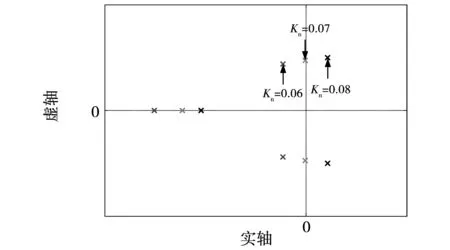

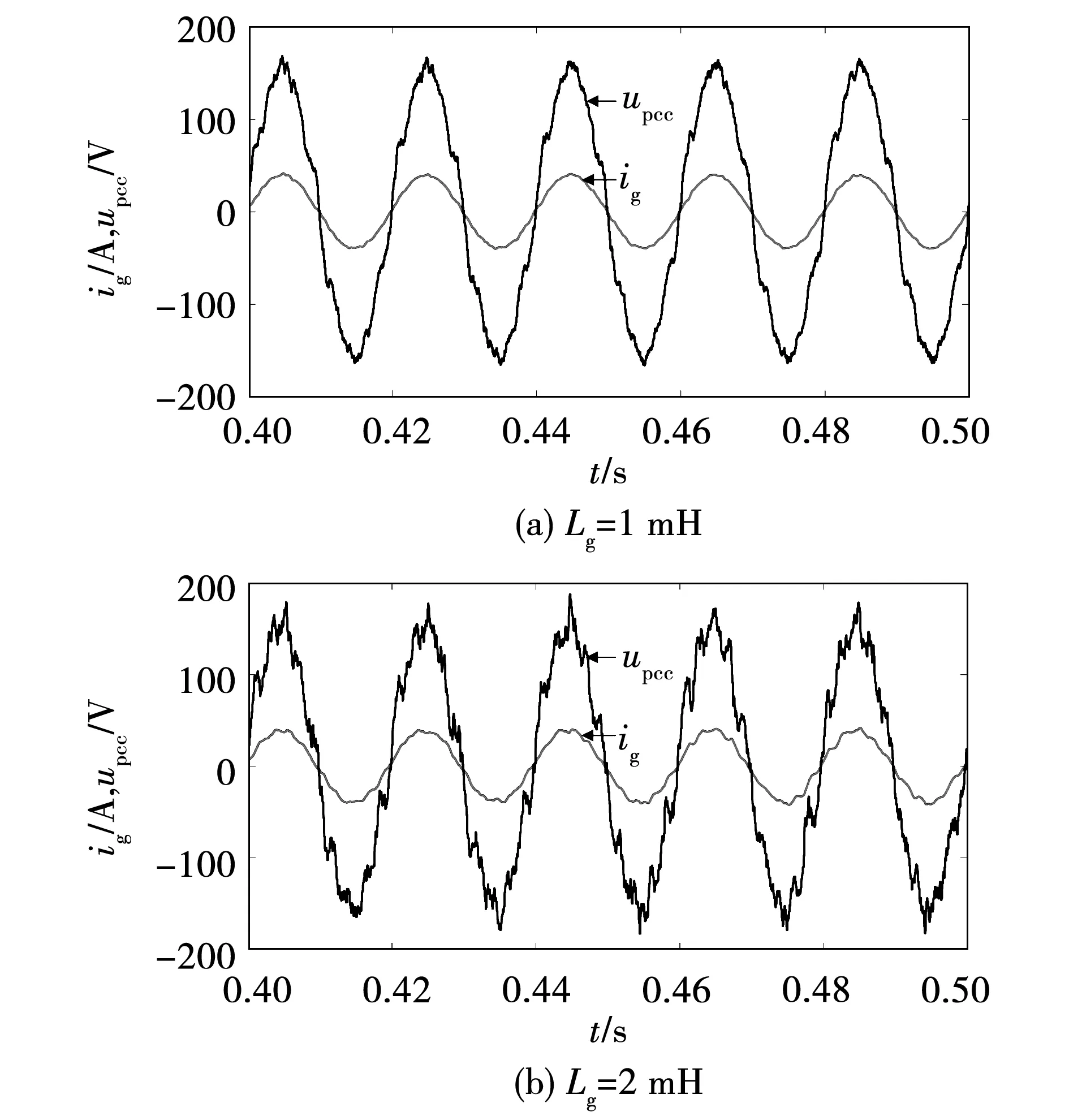

此外,GLCL(s)的相频特性曲线亦随Lg的增加逐渐向中低频段偏移,在远低于fres的频段内,GLCL(s)≈Kpwm/[(L1+LT)s],其相位近似为-90°,随着fres逐渐减小,且fc 电流控制器Gc(s)的Bode图如图4(d)所示。由于本文采用附加5、7、9次谐波补偿项的QPR控制器,当fc接近于9f0(f0为电网基波频率)时,QPR控制器的9次附加谐振项将在fc处产生较大的负相位,进一步降低环路增益T0(s)的相位裕度,并网逆变器控制系统相对稳定性较差。 图4 控制系统的相对稳定性分析Fig.4 Relative stability analysis of control system 根据图2可推导出并网逆变器的闭环增益表达式为 (7) 并网逆变器的闭环特征方程为D(s)=1+T0(s),令D(s)=0,可得关于Lg的等效环路增益表达式为 T0-eq(s)= (8) 根据式(8)绘制T(s)关于Lg的主导极点根轨迹,如图5所示。从图5可以明显看出,随着Lg增加,闭环极点逐渐靠近虚轴,当Lg=2.6 mH时,并网逆变器闭环控制系统达到临界稳定状态,意味着此时环路增益T0(s)的相位裕度PM=0°。当Lg继续增大,闭环系统将产生正实部的闭环极点,并网逆变器已然失去稳定性。 图5 T(s)关于Lg的主导极点根轨迹Fig.5 Dominant pole root locus of T(s) 当并网逆变器处于临界稳定状态时,T0(s)的相位裕度等于零,即有下式成立[23]: T0(s)|s=j2πfcritical=-1。 (9) 式中fcritical为临界稳定状态时的环路截止频率。 根据图2可得ug(s)到ig(s)的闭环增益Y(s)的表达式为 (10) 式中,G(s)=(L1Cs2+KpwmKdCs+1)/[L1LTCs3+KpwmKdLTCs2+(L1+LT)s]。 畸变的电网电压会在网侧电流中产生对应的谐波电流,为 (11) 式中:igh为网侧电流中的第h次谐波电流;ugh为电网电压中的第h次谐波电压。 当并网逆变器处于临界稳定状态时,即有下式成立: (12) 电网中频率为fcritical的谐波电压被放大,网侧电流ig中将含有频率fcritical的谐波电流,且幅值无穷大,并网逆变器出现谐振现象。 综上所述,弱电网下并网逆变器的稳定性受到严峻地挑战,电网电感Lg会降低环路增益的相位裕度和闭环带宽,Lg在SCR≥3的范围内变化时,可能导致闭环增益产生正实部的不稳定闭环极点,更严重的是,当控制系统处于临界稳定状态时,并网逆变器出现谐振现象,危害逆变器设备的稳定运行,对网侧电流产生谐波污染。因此,为了提高网侧电流质量,需保证并网逆变器控制系统的环路增益在SCR≥3的范围内具有足够的相位裕度。 为了保证并网逆变器在Lg影响下具有较高质量的网侧电流,当Lg发生变化时,环路增益应始终具有足够的相位裕度。前述分析已知,环路谐振频率fres的偏移是导致并网逆变器控制系统稳定性下降和引发谐振现象的主要原因。因此,为了提高控制系统的相对稳定性,应使fres0和fres1均远大于环路截止频率fc,且Δfrmax最小。 所提降低环路谐振频率偏移方法的系统等效控制框图如图6所示,其中Kn和Km分别为电容电流比例系数与电容电压比例系数。根据图6可推导出并网逆变器控制系统环路增益T1(s)表达式为: T1(s)= Gc(s)GLCL1(s), (13) (14) 式中fr代表所提方法下的环路谐振频率,其表达式为: (15) 图6 系统等效控制框图Fig.6 System block diagram 根据式(15)可求得Lg=0 mH和Lg趋近于无穷大时,环路谐振频率fr分别为 (16) 此时系统环路谐振频率偏移为 Δfr=fr0-fr。 (17) 根据(15)可知,fr是关于Lg的减函数,则最大环路谐振频率偏移为 Δfrmax=fr0-fr1。 (18) 对式(17)求取Δfr关于系数Km的导数可得: (19) 通过式(19)可以看出,环路谐振频率偏移Δfr是关于Km的减函数,若选取较大的Km值,GLCL1(s)受Lg的影响将被极大地削弱。特别地,当Km为无穷大时,fr0和fr1均趋近于无穷大,此时最大环路谐振频率偏移Δfrmax≈0。 然而,为了滤除并网逆变器高频次开关谐波,环路谐振频率fr0通常不高于0.5fsw[22],即fr0≤0.5fsw,根据式(16)可求得Km的最大值为 (20) 进一步观察式(17)可知,环路谐振频率偏移与逆变侧电感L1和网侧电感L2的感值分配有关。LCL滤波器在低于fr0频段内可等效为单L滤波器,其总电感量如表1所示,即L1+L2=1 mH。保持滤波器总电感量不变,令L2=βL1,将其代入式(17)并求取Δfr关于β的导数,为 (21) 由此可知,Δfr亦是β的减函数,考虑逆变侧电流对开关器件的电流应力及开关损耗,逆变侧电流纹波系数应小于30%[1],本文选取β=2.5,即L1=0.29 mH,L2=0.71 mH。此外,根据式(18)可知,通过适当调整C的取值,可进一步降低环路谐振频率偏移。通常C的取值与其引入的无功功率密切相关,且引入的无功功率不得高于0.05Pout,可得C≤44 μF,本文选取C=30μF[22]。将L1、L2和C代入式(20)可求得Kmx=0.041。令Km=Kmx,代入式(16)可得fr0= 0.5fsw。随着Lg的增加,最大环路谐振频率偏移为Δfrmax=120 Hz,此时fr0和fr1均远高于环路截止频率(设置Lg=0 mH时的环路截止频率fc=1 kHz)。 电容电流比例系数Kn起到阻尼滤波器谐振尖峰的作用,由于GLCL1(s)含有一个原点处极点和两个共轭极点,因此Kn的取值可根据传统二阶谐振环节进行设计,表达式为 (22) 式中ξ为二阶谐振环节的固有阻尼系数,一般为0.707。 表2给出了所提降低环路谐振频率偏移方法下的并网逆变器控制系统各参数取值(后续分析参数依照表2),图7给出了GLCL1(s)与T1(s)的Bode图。对于GLCL1(s),由图7(a)可以明显地看出,环路谐振频率在Lg增加过程中并无明显偏移,相比较于图4(a),GLCL1(s)的相频特性受Lg变化的影响较弱,且fr0和fr1均远高于fc=1 kHz,GLCL1(s)为环路增益在中低频段提供的负相移近似为-90°;对于T1(s),由图7(b)可以看出,Lg在SCR≥3的范围内变化时,环路增益始终具有足够的相位裕度,避免了并网逆变器谐振现象的发生,其对Lg具有很强的适应性。 表2 并网逆变器的模型参数 图7 传递函数GLCL1(s)与T1(s)的Bode图Fig.7 Bode diagram of GLCL1(s) and T1(s) 从图6可以看出,阻尼环中需要采集电容电流和电容电压两组状态变量,将Kn的输入端由电容电流后移至电容电压,此时仅需采集电容电压即可,减少了一组传感器的使用。然而,电容电压前馈通道中将含有纯微分环节,即G1(s)=KnCs+Km。实际中纯微分环节无法实现,为了消除或减弱微分环节对噪声的放大效应,这里采用二阶线性微分跟踪器近似实现微分环节,此时电容电压前馈通道增益为 (23) 式中T1和T2为时间常数。 并网逆变器的系统等效控制框图如图8所示。 图8 阻尼环单传感器系统等效控制框图Fig.8 Equivalent control block diagram of damping ring single sensor system 当T1=T2=T时,G1(s)处于临界阻尼状态,即有 (24) 微分信号中所包含的噪声由n(t)Ts/T2决定,n(t)为增益G1cd(s)输入电容电压信号中的噪声,Ts为采样周期。图9给出了G1cd(s)在不同时间常数时的Bode图,可以看出,当T远低于Ts时,G1cd(s)与G1(s)具有极高的近似度。为了保证G1(s)在采样频率fs范围内具有较好的近似,且简化时间常数设计,这里选取T1=T2=2.5 μs,此时G1(s)处于临界阻尼,即G1(s)=G1cd(s),G1cd(s)可对电容电压输入信号进行无超调过渡。 此时,阻尼环的环路增益表达式为 (25) 图9 G1cd(s)的Bode图Fig.9 Bode diagrams of G1cd(s) GLCL1-cd(s)的Bode图如图10所示,与图7(a)进行比较,可见采用电容电压单传感器控制,并对G1(s)进行二阶线性微分近似,不会对所提降低环路谐振频率偏移方法造成影响。且阻尼环仅使用一组电压传感器,节省了并网逆变器的成本。 图10 GLCL1-cd(s)的Bode图Fig.10 Bode diagrams of GLCL1-cd(s) 本文采用电容电压锁相并进行功率因数(power factor,PF)校正,保证逆变器能够单位功率因数并网。需要指出的是,逆变器的并网功率因数测定是在公共耦合点进行的,因此在分析系统PF时可以忽略电网阻抗的存在。 图11为LCL滤波器的单相拓扑结构,使用基尔霍夫定律对图11进行分析,可以得到LCL滤波器中状态变量uc和upcc的向量图如图12所示。由于本文使用电容电压uc锁相并对网侧电流ig进行电流反馈控制,因此uc与ig同相位。 图11 单相LCL滤波器Fig.11 Single phase LCL filter 图12 LCL滤波器向量图Fig.12 Vector diagram of LCL filter 由图12结合三角函数关系式可以求得 (26) 式中:基波角频率ω0、网侧电感L2均为已知量;电容电压基波有效值Uc和网侧电流基波有效值Ig可由电流、电压传感器采集的uc和ig求取。 γ即为网侧电流反馈控制的PCC电压与电流的相位差,此相位差就是造成逆变器非单位功率因数并网的原因。进一步可计算出由于系统相位差而造成的无功功率为 Q=Soutsinγ=3IgUgsinγ。 (27) 式中Sout为系统视在功率。 为了实现单位功率因数并网,可令系统产生一个与无功功率Q大小相等、符号相反的无功补偿功率。此时,应给定系统的无功参考电流值为 (28) 当光伏并网逆变器采用数字控制时,控制系统不可避免的存在调制延时和计算延时,等效延时环节在s域中构成的传递函数为 (29) 式中τ表示延迟时间拍数。 考虑数字控制延时的并网逆变器系统等效控制框图如图13所示。图中,τ1代表电流控制器的延迟时间拍数,τ2代表阻尼环的延迟时间拍数,文献[24]表明,减小阻尼环延迟时间可提高并网逆变器在弱电网下的稳定性。由于本文侧重于Lg对控制系统环路谐振频率偏移的影响及降低环路谐振频率偏移的方法研究,这里选取电流控制器输出延时为一拍,阻尼环输出为零延时的理想情况,即τ1=1,τ2=0。零延时的理想情况在实际中难以实现,这里采用文献[25]提出的工程近似方法替代。 图13 考虑数字延时的系统等效控制框图Fig.13 Equivalent control block diagram of system considering digital delay 由于等效延时环节中含有超越函数,不利于控制系统在s域内分析,通常对Gd(s)进行Pàde近似,这里采用三阶近似延时,表达式为 (30) 式中a0=(τ+0.5)Ts。 对于QPR控制器,在环路截止频率处近似为常数,即Gc(s)≈Kp,根据图13可得考虑数字控制延时的环路增益为 Td(s)= (31) 阻尼环的环路增益表达式为 GLCL-d(s)= (32) 可见,阻尼环的等效延时环节Gd2(s)会对控制系统的稳定性产生影响,而电流控制器的等效延时环节Gd1(s)仅会降低环路增益的相频特性。为了保证并网逆变器闭环控制系统稳定,需对参数Kn和Km进行优化设计。 图14分别给出了GLCL-d(s)在Km和Kn变化时的Bode图和主导极点分布图。Km变化时GLCL-d(s)的Bode图和主导极点分布图分别为图14(a)和图14(b),此时Kn=0.07,可以看到,考虑数字控制延时后,阻尼环的环路增益将会产生一个谐振尖峰,且在谐振尖峰附近具有一次负穿越,随着Km的减小,该谐振尖峰幅值逐渐增大,阻尼环的主导极点向虚轴靠近,当Km<0.016 3时,GLCL-d(s)无正实部极点;Kn变化时GLCL-d(s)的Bode图和主导极点分布图分别为图14(c)和图14(d),此时Km=0.041,可以看出,Kn有利于对该谐振尖峰的抑制,随着Kn的增大,该谐振尖峰幅值逐渐减小,然而在Kn变化过程中,GLCL-d(s)始终含有正实部极点。 图14 GLCL-d(s)在Km和Kn变化时的Bode图和主导极点Fig.14 Bode diagram and dominant pole distribution of GLCL-d(s) with Km and Kn 根据奈奎斯特稳定判据可知,并网逆变器闭环系统稳定的充要条件为P=2(N+-N-) ,P为环路增益Td(s)的正实部极点数,N+和N-分别为Td(s)的相频曲线的正穿越和负穿越次数。由于Gd1(s)不会产生正实部极点,且当Km<0.016 3时GLCL-d(s)无正实部极点,因此Km的取值范围可取为(0,0.0163)。根据第三节分析可知,环路谐振频率偏移关于Km为减函数,为降低环路谐振频率偏移,此处选取Km=0.016,将其代入式(18)可得Δfrmax=174 Hz。可见,引入数字控制延时后不会对所提降低环路谐振频率偏移的方法造成影响。 此外,为保证并网逆变器闭环系统稳定,需使负穿越失效。使负穿越失效有两种途径:第一种途径是通过调节电流控制器Kp的大小,使环路截止频率fc处的幅值大于谐振尖峰幅值,令负穿越失效,然而,当谐振尖峰幅值较大时,为满足奈奎斯特稳定判据,意味着fc较低,闭环带宽较小;第二种途径是增大比例系数Kn,通过抑制该谐振尖峰的幅值,令负穿越失效,并能够保证足够的闭环带宽。 分别令Kn=0.08、0.07和0.06,Km=0.016,如图15为GLCL-d(s)的主导极点分布图。根据图15可知,增大Kn进行谐振尖峰抑制的同时,会使系统产生正实部极点,Td(s)无法满足奈奎斯特稳定判据。因此,为使负穿越失效,应采取第一种途径,且选取参数Kn=0.07、Km=0.016。 图15 GLCL-d(s)的主导极点(Km=0.016)Fig.15 Dominant pole of GLCL-d(s)(Km=0.016) 未补偿前(Gc(s)=1)Td(s)的Bode图如图16所示。可以看出,电流控制器等效延时环节Gd1(s)的引入使Td(s)在奈奎斯特频率(fs/2)范围内的相频曲线分别穿过-180°和-540°线,包含两次负穿越,且穿越频率分别为fx1和fx2,分别记为一次穿越和二次穿越。一次穿越对应的幅值为11.2 dB,二次穿越对应的幅值为-1.2 dB,因此二次穿越是失效的,此时仅需使一次穿越失效即可满足奈奎斯特稳定判据。从数字控制延时角度来看,由于Gd1(s)的引入导致Td(s)相频特性曲线滞后,且前述分析已知数字控制延时不会对所提降低环路谐振频率偏移的方法造成影响,可认为在Lg变化过程中Td(s)的相频特性不会发生改变,二次穿越始终失效,这有利于电流控制器参数的设计,且能够保证控制系统具有足够的带宽。 图16 未补偿前Td(s)的Bode图Fig.16 Bode diagram of Td(s) before compensation 设置环路截止频率fc=1 kHz,在fc处环路增益的幅值为|Td(j2πfc)|=0 dB,根据式(31)可求得电流控制器的比例系数Kp=0.126。Td(s)在Lg变化时的Bode图如图17所示。可以看到,考虑数字控制延时后,所提降低谐振频率偏移的方法在SCR≥3的范围内仍适用,并且具有足够的相位裕度。 图17 补偿后Td(s)的Bode图Fig.17 Bode diagram of Td(s) after compensation 根据图1所示三相LCL型并网逆变器控制结构示意图,在Simulink中搭建仿真模型验证不同控制策略下并网逆变器的稳定性。同时,为模拟电网背景谐波的影响,在电网电压中分别注入4%的5次、7次和9次背景谐波。值得说明的是,在RE-DPGS系统中,升降压变压器多采用星三角的联接方式,该联接方式可有效削弱三次谐波对系统的影响,故此处不再对电网中的三次背景谐波进行赘述。 5.1.1 不存在数字控制延时 对于传统电容电流有源阻尼及并网点电压锁相的并网逆变器控制策略,在电网电感分别为Lg=1、2 mH时网侧电流ig和PCC电压的仿真波形如图18所示(以A相为例)。可以看出,在Lg=1 mH时,由于系统具有较好的稳定裕度,并网逆变器输出的网侧电流波形质量较好,且ig和upcc的总谐波失真数分别为THD=2.73%和7.64%,电网电压中的低频次背景谐波均得到较好的抑制。随着电网阻抗的增大,当Lg=2 mH时并网逆变器输出的网侧电流波形质量较差,ig和upcc的总谐波失真数分别为THD=5.93%和11.62%,无法满足相应的并网要求(THD<5%)。 图18 传统控制策略下ig和upcc的输出波形Fig.18 Output waveform of ig and upcc 本文所提采用电容电压比例微分前馈控制策略在电网电感分别为Lg=2、3.9 mH时的网侧电流ig和PCC电压仿真波形如图19所示(以A相为例)。由图19可以看出,并网逆变器在所提策略下进行并网运行下,网侧电流在Lg宽范围变化时均具有较高的电流质量,且ig的总谐波失真数分别为THD=0.51、0.39%。可见,所提控制策略显著改善了并网逆变器对弱电网的鲁棒性。 图19 所提控制策略下ig和upcc的输出波形Fig.19 Output waveform of ig and upcc 为检验电容电压锁相造成的非单位功率因数并网及所提功率因数校正方案的有效性,在理想电网条件下(以A相为例),进行PF校正前的网侧电流ig、滤波电容uc及PCC电压的输出波形如图20所示。根据图20可以明显看出,PF校正前ig与uPCC未同时过零点,并网逆变器无法单位功率因数并网,PCC点处的无功功率较大;进行PF校正后的ig与upcc同时过零点,PCC点处的有功功率增大,无功功率减少,并网逆变器可近似实现单位功率因数并网运行。 图20 功率因数校正Fig.20 Correction of power factor 5.1.2 存在数字控制延时 当考虑数字控制延时对所提策略的影响时,电流控制器的谐振系数分别为Kr1=30、Kr5、7、9=10,阻尼环延时为零拍条件下的网侧电流ig和PCC电压仿真波形如图21所示(以A相为例)。从图21可以看出,数字控制延时的存在并未对所提控制策略造成显著影响,在SCR≥3范围内并网逆变器仍可以输出较高质量的网侧电流。 仿真分析表明,本文所提采用电容电压比例微分前馈控制策略不仅提高了并网逆变器对电网阻抗宽范围变化时的鲁棒性,当采用电容电压进行锁相控制时,对功率因数进行校正亦可保证并网逆变器实现单位功率因数并网。 图21 所提控制策略下ig和upcc的输出波形(考虑延时)Fig.21 Output waveform of ig and upcc 本文采用南京Rtunit公司开发的实时数字控制器RTU-BOX204控制平台,搭建了如图1所示的10kW三相LCL型并网逆变器实验样机。由于实验样机中将不可避免的引入数字控制延时,本节仅给出考虑数字控制延时后,并网逆变器在所提控制策略下运行时的网侧电流ig和PCC电压实验波形。 对于阻尼环的零拍延时而言,在实际中无法理想获得,这里采用文献[25]所提采样方式进行近似实现。网侧电流ig和PCC电压实验波形如图22所示,可以看出,并网逆变器在本文所提控制策略下运行时,电网电感分别为Lg=1、2和3.9 mH的网侧电流波形畸变较小;此外,当并网逆变器由满载跳变至半载时,网侧电流如图22(d)所示,系统的动态调节时间较短,并无明显超调,所提控制策略具有优良的动态性能。 图22 所提控制策略下ig和upcc的实验波形Fig.22 Output waveform of ig and upcc 对并网逆变器进行功率因数校正前后的网侧电流ig和PCC电压实验波形如图22(e)所示。从图22(e)可以看出,PF校正前的网侧电流ig和PCC电压并未同时过零点,并网逆变器非单位功率因数并网;PF校正后的网侧电流ig和PCC电压同时过零点,此时并网逆变器单位功率因数并网,提高了直流母线侧的能量利用率,减小PCC处无功功率对并网点电压的影响。 仿真分析和实验结果验证了上述理论分析的正确性,本文所提基于电容电压比例微分前馈的谐振频率偏移抑制控制策略,不仅提升了并网逆变器在弱电网下的稳定性,通过PF校正还可使逆变器实现单位功率因数并网。在考虑数字控制延时的影响下,该控制策略仍能够适应宽范围变化的电网电感,避免了逆变器与电网互联系统的谐振发生,控制系统具有足够的稳定裕度。 本文基于系统开环增益的Bode图研究了弱电网下并网逆变器稳定性下降机理,主要得出以下结论: 1)对于传统电容电流有源阻尼的直接电流控制策略,在弱电网条件下并网逆变器的稳定运行受到严峻挑战,电网电感的变化导致环路谐振频率偏移是造成控制系统稳定性下降及互联系统谐振发生的主要原因。 2)为抑制环路谐振频率偏移,本文提出采用电容电压比例微分前馈的谐振频率偏移抑制控制策略,不仅能够节省一组传感器,对弱电网下环路谐振偏移亦有极大的抑制作用,使控制系统在SCR≥3的范围内具有足够的稳定裕度,避免了互联系统谐振的发生。 3)通过使用电容电压锁相进行网侧电流的直接控制,对并网逆变器进行功率因数校正,可保证逆变器实现单位功率因数并网。 4)考虑数字控制延时对所提控制策略的影响,当阻尼环采用零拍延时的方式进行采样时,所提控制策略对系统环路谐振频率偏移的抑制作用并未发生明显变化,并网逆变器在弱电网下仍具有足够的稳定裕度。

2.2 并网逆变器控制系统闭环极点分析

2.3 并网逆变器的谐振现象

3 降低环路谐振频率偏移的方法

3.1 电容电流和电容电压双比例前馈设计

3.2 阻尼环单传感器控制

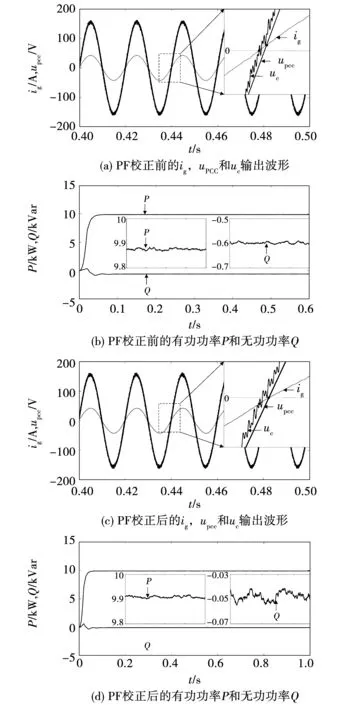

3.3 电容电压锁相功率因数校正

4 考虑数字控制延时的参数优化

5 仿真分析与实验验证

5.1 仿真分析

5.2 实验验证

6 结 论