基于预充电逻辑与掩码技术的功耗恒定性电路设计

2022-04-06姚茂群李聪辉

姚茂群,李聪辉

(杭州师范大学信息科学与技术学院,浙江 杭州 311121)

0 引言

自P. Kocher提出简单功耗分析(simple power analysis, SPA)攻击和差分功耗分析(differential power analysis,DPA)攻击方法以来,研究者们的注意力不再仅集中于加强密码算法协议的安全性方面,而且开始关注密码元器件在运行时不可避免会产生的侧信道信息方面.功耗分析攻击作为侧信道攻击中有效且易操作的攻击方法,近年来已受到较多的关注[1-4].功耗分析攻击利用密码元器件在运行时所产生的运算结果进行与功耗之间的相关性分析,攻击者利用这种相关性可以分析出密码元器件中的敏感数据或者秘密数据,从而造成数据泄露.当前,防范功耗分析攻击的方法主要分为算法级和电路级两种层次.算法级的防护方法主要有动态重构技术[5-7]、算法级掩码技术[8-11]等.算法级的防护方法忽略了电路本身所具有的功耗特性,在密码协议的算法上进行改进;电路级的防护技术关注于密码元器件底部的电路结构而不是密码算法本身,通常需要设计新型的电路逻辑单元,因而更具有通用性.电路级的防护技术又可以分为功耗恒定技术和功耗随机化技术.功耗恒定技术主要采用双轨预充电逻辑结构,可以使电路的功耗不随运算结果的变化而变化.功耗随机化技术主要利用电路级掩码技术[12-13],通过在逻辑单元中加入随机掩码,使每个单元的瞬态功耗服从均衡分布.

近年来,国际上已经提出了多种电路逻辑来抵抗功耗分析攻击,例如基于双轨预充电逻辑结构(dual rail pre-charge logic,DRP Logic), Tiri 等提出的行波动态差分逻辑(wave dynamic differential logic,WDDL)电路[14],乐大珩提出的基于查找表差分逻辑(LUT-based differential logic, LBDL)[15],王晨旭提出的差分传输管预充电逻辑(differential pass-transistor pre-charge logic, DP2L)[16]等.这些电路都具有功耗恒定特性,可以在一定程度上消除逻辑电路的运算结果与功耗之间的相关性.利用Hspice对DP2L电路进行分析,发现该电路在不同输入信号情况下,还无法达到完全的功耗恒定,仍然存在被功耗攻击的风险.因此,本文对该逻辑电路进行改进,同时加入电路级掩码技术.即使攻击者获得电路的输入信号,由于随机掩码的存在,攻击者仍然无法获得准确的运算结果,增强其抗功耗攻击的能力.

1 DP2L逻辑电路及其功耗恒定性分析

1.1 双轨预充电逻辑结构

双轨预充电逻辑结构被广泛应用于具有功耗恒定特性的逻辑电路设计当中,主要利用了CMOS逻辑单元在信号输出时的功耗特点进行设计,即该类型的电路只有在输出信号发生“0→1”或“1→0”翻转时才消耗能量,其他情况下不消耗能量.之后利用两个对称的互补单轨电路组成双轨电路,使整个电路的输出信号翻转率恒定,从而达到功耗恒定的特性.在预充电阶段,所有输入信号的取值都为低电平“0”,双轨(单轨)预充电逻辑电路的输出也都为逻辑值“0”.在求值阶段,双轨(单轨)预充电逻辑电路输出正常的逻辑运算值.其中对于双轨预充电逻辑电路来说,两个输出端为互补信号.

当双轨预充电逻辑电路从预充电阶段进入求值阶段时,两个互补输出端中有且仅有一个会发生“0→1”翻转,而另一个将保持“0”不变.当从求值阶段进入预充电阶段时,也有且仅有一个发生“1→0”翻转,另一个保持“0”不变,这就使双轨预充电逻辑电路具有恒定的信号翻转率,成为功耗恒定的理论基础.

1.2 DP2L逻辑电路

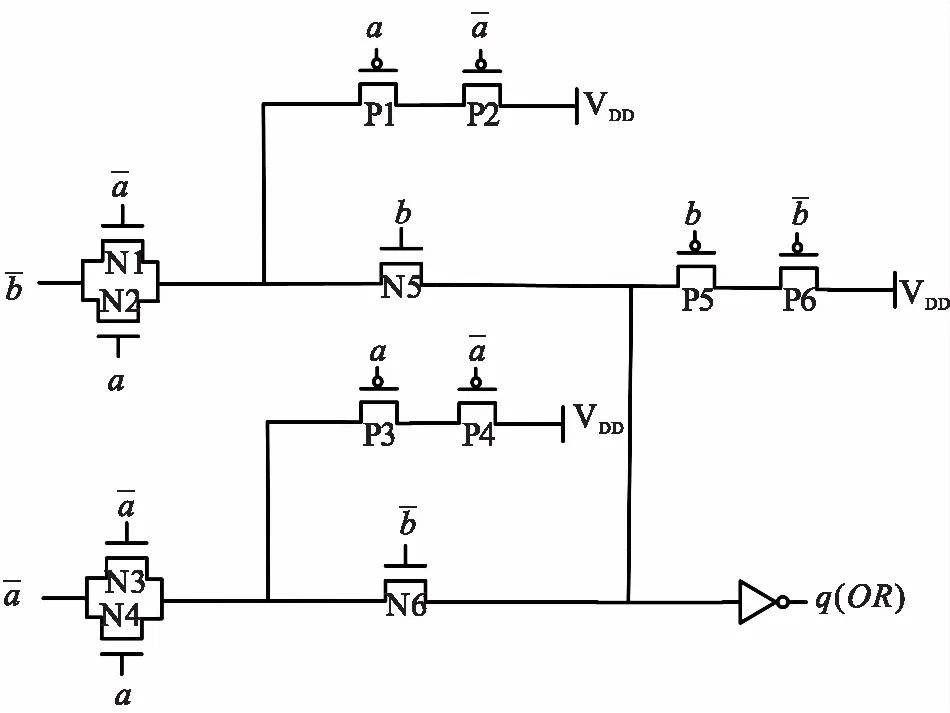

图1 DP2L单轨或逻辑门Fig.1 DP2L single-rail OR gate

1.3 DP2L逻辑电路的功耗分析

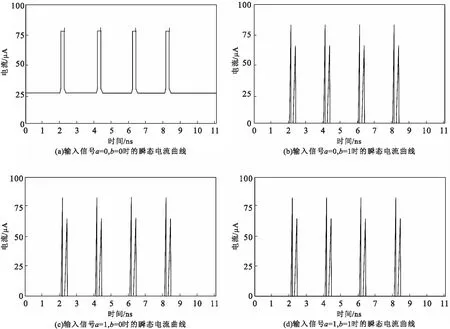

图2(a)、(b)、(c)、(d)分别是输入信号为(0,0)、(0,1)、(1,0)和(1,1)时的电源端瞬态电流.有明显电流峰值的部分为电路进入求值阶段且输出信号发生翻转时所产生的电源端瞬态电流,其中图2(a)由于输出信号未发生翻转,产生的电流很小.每个输入信号以2.3 ns为一个周期运行4次以保证实验数据的准确性.由图2可知,当输入信号不同时,电源端的电流出现差异,这也会造成一定程度的功耗信息泄露,即存在一定程度上的功耗与运算结果的相关性,存在被功耗攻击的风险.

图2 DP2L单轨或逻辑门瞬态电流曲线Fig.2 Current of the power supply terminal of DP2L singel-rail OR gate

2 DP2L逻辑电路的改进型设计

2.1 功耗恒定性改进设计

图3 改进后的DP2L单轨或逻辑门Fig.3 Improved DP2L single-rail OR gate

DP2L电路在不同输入信号条件下具有不同的功耗特性,对该电路进行改进.图3为改进后的DP2L单轨输出或逻辑门.

2.2 MDP2L电路设计

图4 MDP2L单轨或逻辑门Fig.4 MDP2L single-rail OR gate

以上述改进电路为基础,将掩码技术引入其中,设计了具有掩码功能的掩码型差分传输管预充电逻辑(masked differential pass-transistor precharge logic, MDP2L)电路.图4为MDP2L单轨或逻辑门,左侧由两部分组成,上半部分为或逻辑门的主要部分,下半部分为或非逻辑门的主要部分.随机掩码值m的取值不同时,会形成两条不同的通路.当m=0时,q为未掩码值的正逻辑输出;当m=1时,q为未掩码值的负逻辑输出.由于随机数的取值具有相同的可能性,因此该电路在此部分的输出值(0/1)也具有相同的概率,在密码芯片输出时利用掩码转换为正常逻辑值.根据该设计原理,只需对掩码的位置进行互换,就可得到相同结构的MDP2L单轨或非逻辑门.

利用Hspice软件对图4所示电路进行模拟仿真实验,实验方法与图2所使用的方法相同,并设随机掩码值m为0,实验结果如图5所示.由图可知,当输出信号发生翻转时,不管输入信号的取值如何,电源端电流(功耗)都是近似相等的.

图5 MDP2L单轨或逻辑门瞬态电流曲线Fig.5 Current of the power supply terminal of MDP2L single-rail OR gate

将MDP2L单轨“或”逻辑门与MDP2L单轨“或非”逻辑门相组合,就构成了MDP2L双轨输出“或”逻辑门(图6).若要实现MDP2L双轨输出“或非”逻辑门,只需要将两条输出交叉换线即可.

3 功耗恒定性评估

对图6所示的电路进行Hspice模拟仿真测试,设随机掩码值m为0,且以2 ns为一个周期,每个周期的输入信号(a,b)分别为(0,0)、(0,1)、(1,0)和(1,1).有明显电流峰值的部分为求值阶段,其余都为预充电阶段,实验结果如图7所示.由图7可知,无论输入信号为何值,该电源端的电流大小(功耗)都是非常接近的,即逻辑电路的运算结果与功耗之间的联系被一定程度地削弱.随机掩码的存在又可使电路的输出结果随机化,只需在使用时将其转换成正确的数值即可.设随机掩码值m为1,得到的实验结果与图7完全相同,即随机掩码的取值不影响电路运行时的功耗.

图6 MDP2L双轨或逻辑门Fig.6 MDP2L double-rail OR gate图7 MDP2L双轨或逻辑门电源端瞬态电流曲线Fig.7 Current of the power supply terminal of MDP2L double-rail OR gate

为验证其功耗恒定特性,并与国际上同类型逻辑电路比较,引入常用的衡量功耗恒定特性的评价指标:标准化能量偏差(normalized energy deviation, NED)[14].其定义为

式中,E是逻辑电路在一个运算周期内所产生的功耗值的集合,取值范围在[0,1],且数值越小表明功耗恒定性和抗功耗攻击的性能越好.

表1 同类型逻辑实现的门电路标准化能量偏差对比Tab.1 NED of gate implemented using the same logic type

表1列出了国际上同类型逻辑电路实现的与门和或门的标准化能量偏差数据对比,MDP2L双轨电路具有较低的NED值,表明该电路减少了电路运算结果与功耗之间的相关性,提高了电路抗功耗攻击的能力.

4 结论

在不同输入信号的情况下,DP2L电路晶体管导通数目不同,可能无法完全达到功耗恒定特性.本文提出了改进后的新型DP2L电路,并以此为基础引入掩码技术,提出了MDP2L电路.与其他同类型电路相比,MDP2L电路具有较低的NED值,可增强其抗功耗攻击能力,为密码元件的安全性和可靠性提供进一步保障.