LEO-5G下行同步算法设计与FPGA实现

2022-03-29肖俊秋

曾 维,肖俊秋,夏 欢,谭 磊,张 鹏

(成都理工大学 机电工程学院,成都 610059)

0 引 言

低地球轨道(Low Earth Orbit,LEO)卫星移动通信系统不仅是地面移动通信系统强有力的补充和扩展,还是未来移动通信的一个重要发展方向。然而,卫星运行轨道高度高,信号传输时延高且变化快,卫星通信需要比地面通信系统更高效准确的定时估计算法;地面终端与卫星通信过程中,会产生较大的多普勒频移,影响正交频分复用(Orthogonal Frequency Division Multiplexing,OFDM)信号各子载波的正交性,这对系统的频偏估计性能提出了挑战[1]。在地面第五代移动通信技术(5th Generation Mobile Communication Technology,5G)新空口(New Radio,NR)系统中,基站发送信号的定时和频偏估计是在下行同步过程中完成的[2]。因此,研究下行同步技术对于克服卫星信道对通信的影响和增强卫星5G系统的可靠性有重要的意义。目前,针对下行同步已有大量的算法研究,文献[3]介绍了使用最广泛的时域互相关算法,该算法将接收时域信号与本地生成的主同步信号(Primary Synchronization Signal,PSS)时域序列进行相关;文献[4]提出一种分段自相关算法,通过对PSS互相关值分段计算的方式,在一定程度上减少了频偏对检测结果的影响;文献[5]利用现场可编程逻辑门阵列(Filed Programmable Gate Array, FPGA)的并行策略实现了下行同步算法。

本文以第三代合作伙伴计划(3rd Generation Partnership Project,3GPP) 5G NR技术标准为基础,在最大程度复用5G NR通信体制的前提下,针对LEO卫星移动通信系统的技术特点,对物理层接收信道模型进行了优化和改进,对终端下行时频同步技术进行了算法研究设计和FPGA实现,利用Vivado软件仿真和板级调试,最终验证了该方案的实用性和可靠性。

1 LEO-5G下行时频同步算法设计

时频同步是用户设备(User Equipment, UE)接入LEO-5G系统的首要步骤之一。只有实现了物理小区标识(CELLID,ID)获取和下行时频同步,才能获得系统信息从而准确解调数据,因此下行时频同步算法的设计尤为重要。在LEO-5G系统同步过程中,通过子载波间隔和信号带宽等参数,按照协议进行查表,可确定OFDM符号长度以及循环前缀(Cyclic Prefix, CP)长度,基于上述参数才能进行去CP和快速傅里叶变换(Fast Fourier Transform,FFT)等操作。在上述参数已知的情况下,LEO-5G系统的下行时频同步算法主要包括PSS同步、辅同步信号(Secondary Synchronization Signal,SSS)同步、时间精同步和频偏精同步等步骤,其流程如图1所示。

图1 下行时频同步算法流程

1.1 改进的PSS检测算法

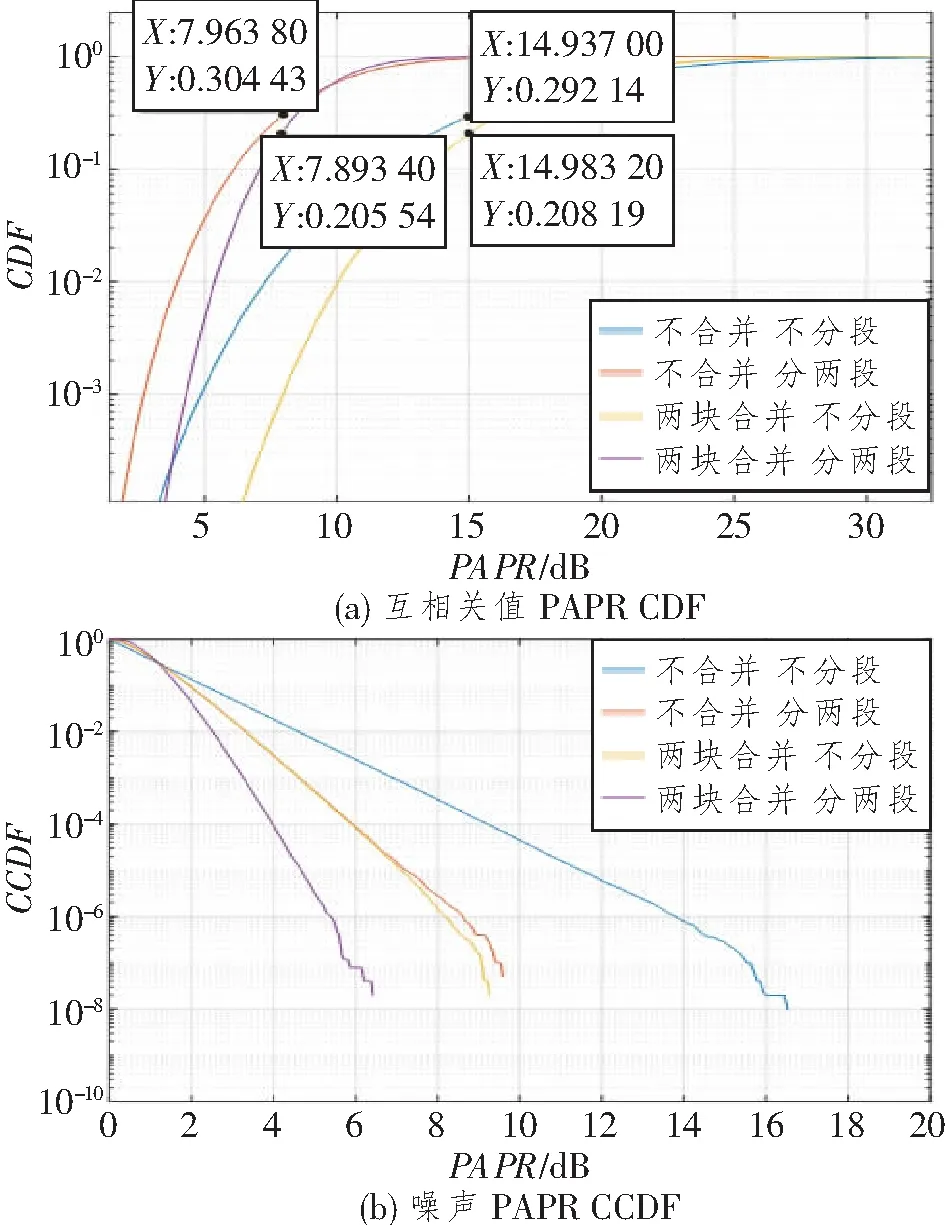

本文对传统PSS算法做出改进,通过对比提出了一种“两块合并分两段互相关”的PSS检测算法。在信噪比(Signal-to-Noise Ratio,SNR)SNR=-8 dB时,Matlab软件仿真得到:“不合并不分段”、“不合并分两段”、“两块合并不分段”和“两块合并分两段”[7]4种检测算法的互相关值峰值对平均值功率比(Peak-to-Average Power Ratio,PAPR)、累积分布函数(Cumulative Distribution Function,CDF)和噪声PAPR 互补累计分布函数(Complementary Cumulative Distribution Function,CCDF),如图2所示。

图2 互相关值PAPR CDF与噪声PAPR CCDF

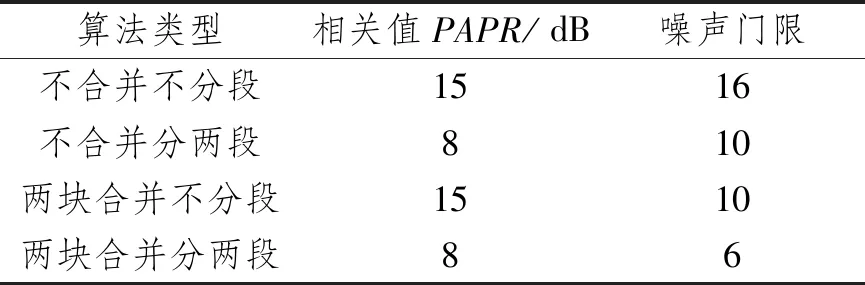

由图可知,在无频偏情况下:采用“不合并不分段”互相关算法时,对应PAPR约为15 dB,噪声门限取16;采用“不合并分两段”互相关算法时,对应PAPR约为8 dB,噪声门限取10;采用“两块合并不分段”互相关算法时,对应PAPR约为15 dB,噪声门限取10;采用“两块合并分两段”互相关算法时,对应PAPR约为8 dB,噪声门限取6。各算法性能表现如表1所示。

表1 算法性能表现

由图2可知,当频偏为50 kHz(0.45个子载波)时,“不分段”互相关检测算法与“分两段”互相关检测算法,在信号对齐时刻的PAPR分别为原来的80%(PAPR门限值为3 dB)和92.5%(PAPR门限值为0.6 dB),故采用“分两段”互相关检测算法时,PAPR值降低较少,PSS检测概率更高。

1.2 SSS检测算法

由LEO-5G系统定义,单边带(Single Side Band,SSB)块中的SSS共有336组,若在时域进行信号检测,会导致相关乘法计算量过大,因此SSS一般在频域进行检测,相关运算只涉及加法[8]。为保证资源消耗与延迟要求,在SSS逻辑实现部分,不考虑多块合并算法,而是将接收基带信号与本地336组SSS序列直接互相关,比较判决最大模值。

1.3 时间精同步

时间精同步的目的是找到原始采样率上的定时同步点。如式(1)所示,根据粗定时即PSS检测的结果,设置一个固定长度的搜索窗,将原始采样率信号与本地PSS进行滑动互相关求模方,最大值即为精定时点。

式中:rx(m+i)为原始采样率信号变换到频域的结果;i为滑动窗系数;pss*(m)为本地PSS检测值;NFFT为FFT点数。

根据粗定时结果,设置搜索窗SearchWindow范围为[-Dw,Dw] ×Ds个样点,本设计降采样倍数Ds取32,窗长Dw取2,在具体实现中可自由配置。

1.4 频偏精同步

频偏粗同步通过PSS分段相关估计,估计的频偏范围大,但精度较低。在完成SSS检测后,可以通过PSS和SSS相关对频偏进一步估计,与粗频偏同步类似,方法也是通过相位累积估计频偏值。

在系统120 kHz子载波间隔下,对应的频偏估计范围为(-28,28] kHz。为减小噪声影响,PSS和SSS仍使用降采样后的基带信号,即FFT点数为128。由于小区特定参考信号(Cell Specific Reference Signal,CRS)在整个带宽内分布,CRS相关在高采样率下进行。因此,本设计在利用同步信号的精频偏估计基础上,利用CRS导频信号完成进一步精频偏估计。

2 下行同步算法的FPGA实现

2.1 下行同步FPGA实现架构

图3 LEO-5G下行同步的FPGA实现架构

2.2 各个模块的具体功能与思路

2.2.1 PSS检测模块

2.2.2 SSS检测模块

2.2.3 CFOC频偏补偿模块

CFOC模块的思路是,通过输入的频率偏移量来产生相应的补偿数据,对最多4相并行输入的数据进行实时频偏补偿。在模块开始处理的valid信号拉高之后,如果收到的频偏与上一周期的频偏不一致,直接数字式频率合成器(Direct Digital Synthesizer,DDS)复位并计算频率控制字与相位偏移量等数据,复位电平低有效且持续2个时钟后拉高。当DDS接收到输入有效信号后开始工作,延迟6个时钟后拉高DDS输出有效信号,并开始输出计算得到的正余弦信号,然后通过该信号对延时了相应时钟的4相输入同相正交(In-phase/Quadrature,IQ)数据进行实时频偏补偿。

2.2.4 信道估计模块

信道估计模块的主要目的是通过本地频域数据X(k)和接收数据Y(k)来估计信道响应H(k)。具体思路是,首先将接收到的CRS信号与本地导频CRS信号进行共轭相乘,再进行离散傅里叶变换(Discrete Fourier Transformation,DFT)运算,求取信号功率。然后,搜索确定最大信号功率位置,并通过最大信号功率位置范围,计算出信号平均功率和噪声平均功率。同时进行时域降噪,采用DFT运算方式得到信道估计值,并通过信号和噪声功率计算SNR。最后,通过线性插值计算出定时误差。

2.2.5 星座解映射模块

在星座解映射模块采取了软解调的方式。发送端,星座映射是将N比特输入数据采用指定的调制方式变换成频域内的符号。二进制相移键控(Binary Phase-Shift Keying,BPSK)和π/2-BPSK将1 bit映射为一个符号,QPSK将2 bit映射为一个符号, 8PSK将3 bit映射为一个符号。星座解映射基本为星座映射的逆过程,通过上层信号控制的映射方式,将输入的复数数据还原为以对数似然比(Log Likelihood Ratio,LLR)表示的软解调信息,并通过一定的算法进行输出幅度的控制。

3 FPGA仿真结果及分析

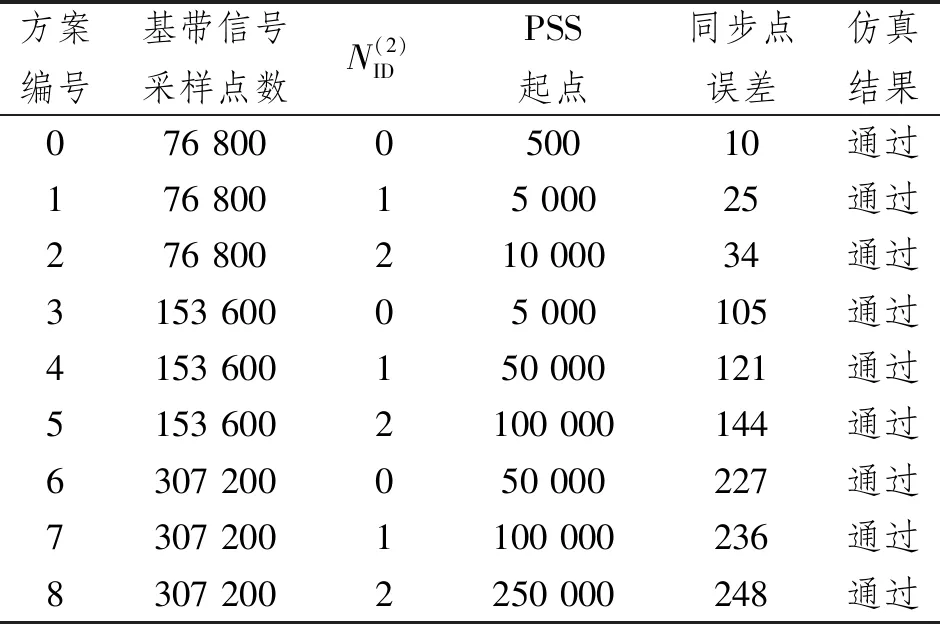

3.1 PSS检测仿真

表2 PSS检测模块仿真结果总结

3.2 SSS检测仿真

图4 SSS检测模块的仿真结果

4 FPGA有效性验证

4.1 Matlab软件仿真结果验证

为了验证 FPGA算法的有效性,联合Matlab软件对本设计中FPGA模块的同步性能进行测试,将空口实验数据PBCH比特作为Matlab软件链路发送端的输入,经过加性高斯信道,在接收端依次进行符号级和比特级的处理,最后完成MIB解析。其次,将第一步中加性高斯信道后的接收数据进行定点化处理,作为文本文件(Textfile,TXT)输入到下行时频同步FPGA模块中,完成一系列仿真测试;然后在Matlab软件中对仿真测试结果进行比特级处理;最后,完成MIB解析。MIB解析结果如图5所示,当SNR>-4 dB时,MIB解析正确率高于90%。当MIB解析正确率达到90%以上时,FPGA设计的同步性能比Matlab软件设计的同步性能低1 dB左右,当SNR范围为[-7,-4] dB时,FPGA模块MIB解析正确率为约83.07%。

图5 Matlab软件仿真结果

4.2 时序与资源消耗验证

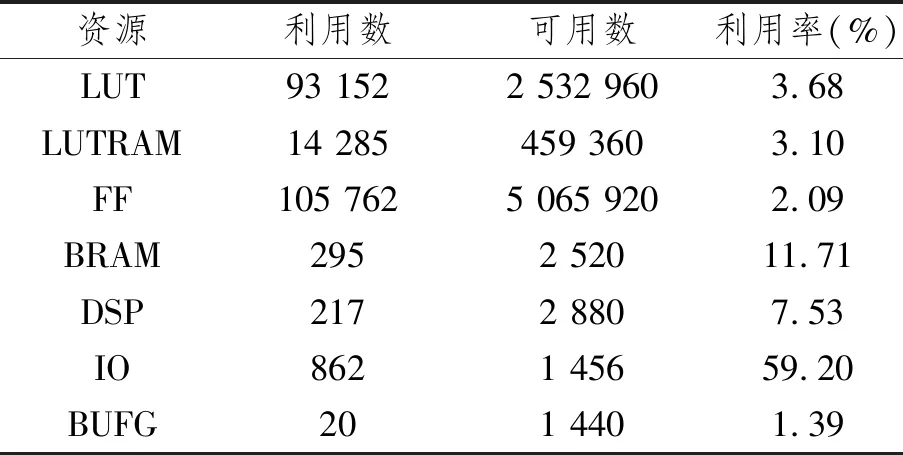

在实现下行时频同步功能后,需评估工程整体时序和资源消耗情况,以验证方案的合理性。本文LEO-5G系统下行链路配置为100 MHz带宽和120 kHz子载波间隔时,要求系统吞吐率为66 RB×12 RE×14 symbs×2 bit/0.125 ms=177.408 Mbit/s,而下行同步FPGA设计的最大运行频率为250 MHz,满足177 Mbit/s的LEO-5G系统下行峰值速率要求。

根据LEO-5G系统需求,设计选择的芯片型号为xcvu440-flga2892-1-i,Vivado给出的下行时频同步FPGA模块片上资源消耗报告如表3所示。查找表(Look-Up-Table,LUT)、嵌入式块(Block Random Access Memory,BRAM)和数字信号处理(Digital Signal Processing,DSP)的消耗占比分别为3.68%、11.71%和7.53%,为LEO-5G系统进一步集成物理下行共享信道(Physical Downlink Shared Channel, PDSCH)与物理下行控制信道(Physical Downlink Control Channel, PDCCH)链路留下了充足的资源。

表3 下行时频同步FPGA模块片上资源消耗报告

5 结束语

本文基于LEO-5G系统的PBCH链路结构和下行时频同步总体架构,对比了3种PSS检测算法后,提出了“两块合并分两段互相关”检测算法,有效提高了在有频偏情况下的检测正确率。同时,给出了频偏粗同步、SSS检测、时间精同步和频偏精同步的算法设计。此外,联合Matlab软件使用空口实验数据对FPGA工程进行测试,得到MIB解析正确率约为83.07%,成功验证了方案的正确性与可靠性。最后,通过对时序和资源消耗的评估,本文设计的FPGA工程时序为250 MHz,芯片的存储资源消耗仅为11.7%,各项指标均符合指标要求,可以为LEO-5G系统终端基带芯片的研制提供一定的参考价值。