万兆以太网TCP/IP 传输系统设计

2022-03-02宋海声李先勤赵承心杨海波孙文健李承飞

宋海声,彭 鹏,,李先勤,赵承心,杨海波,孙文健,,李承飞,

(1.西北师范大学 物理与电子工程学院,甘肃 兰州 730070;2.中国科学院近代物理研究所,甘肃 兰州 730000)

0 引 言

随着近年来物理学家对核物理实验要求的提升,现代核物理实验装置在规模、能级以及事件率上快速提升。我国目前核物理实验装置的数据传输系统多基于商用平台开发,存在数据带宽有限、成本较高、系统构建复杂、稳定性较差等问题。为了达到高性能、高稳定的数据传输需求,需要设计一种满足实验要求的数据传输系统。在考虑了高带宽、低成本和高通用性的要求之后,本文拟在FPGA 平台下实现对万兆以太网TCP/IP 传输系统的设计,并对设计进行测试验证。

1 系统设计方案

1.1 整体设计

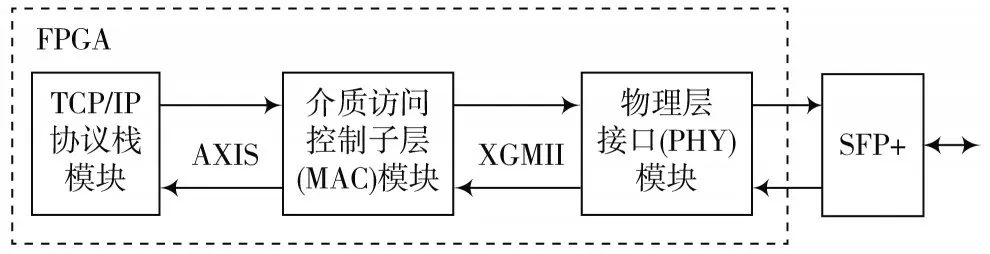

如图1 所示,万兆以太网TCP/IP 传输系统设计主要由TCP/IP 协议栈模块、介质访问控制子层(MAC)模块和物理层接口(PHY)模块三部分组成。TCP/IP 协议栈模块通过用户接口(AXIS)与介质访问控制子层(MAC)模块相连接,介质访问控制子层(MAC)模块通过XGMII接口连接到物理层接口(PHY)模块,最后通过10G SFP+光纤与外界进行数据传输。本文MAC 模块和PHY模块分别调用了Xilinx 官方的10 Gbit Ethernet MAC IP核与10 Gbit Ethernet PCS/PMA IP 核来实现对应模块的功能。下面将主要介绍TCP/IP 协议栈模块的设计,对MAC 模块和PHY 模块将不再过多阐述。

图1 系统设计框图

1.2 TCP/IP 协议栈模块设计

如图2 所示,TCP/IP 协议栈模块设计包含了协议报文的接收、解析、缓存、控制、组帧、发送等过程。在本设计中,调用Xilinx 官方RAM 缓存IP 核作为TCP/IP 协议栈在数据接收和发送过程中的数据缓存。

图2 TCP/IP 协议栈模块设计框图

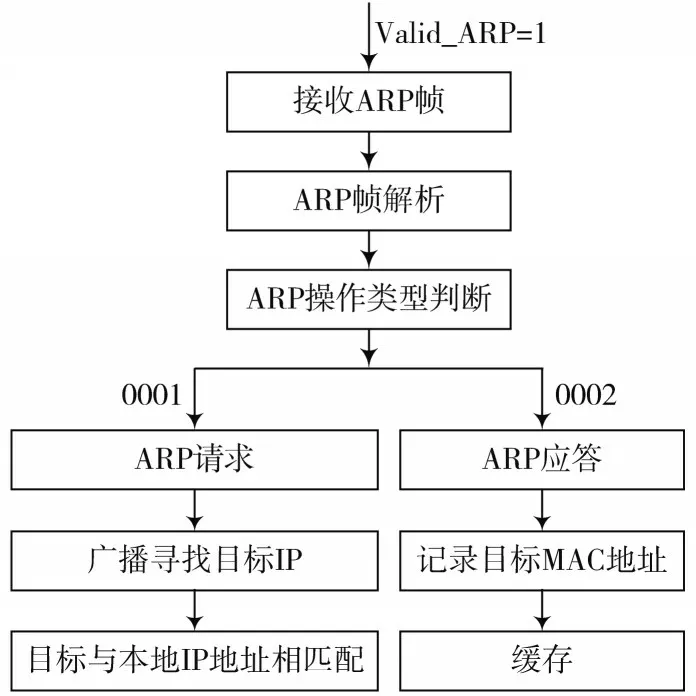

1.2.1 地址解析协议模块设计

ARP 模块设计主要分为两个模块:一个是ARP 接收模块,另一个是ARP 发送模块。如图3 所示为ARP 接收模块工作时的一个状态转移图。当接收信号为有效时,该模块将持续从介质访问控制子层模块接收ARP帧。随后将ARP 帧进行解析并对操作类型进行判断:当ARP 操作类型为0001 时,则进入ARP 请求状态,本地客户端进行广播寻找目标IP,直至目标IP 与本地IP 相匹配;当ARP 操作类型为0002 时,则进入ARP 应答状态,记录下目标MAC 地址并缓存至RAM。这时发送模块将ARP 的首部与ARP 的应答报文组帧成ARP 报文,封装完毕后,发送ARP 报文。

图3 ARP 接收模块状态转移图

1.2.2 网际协议模块设计

IP 模块设计主要分为两个模块:一个是IP 接收模块,另一个是IP 发送模块。如图4 所示为IP 接收模块工作时的一个状态转移图。当接收模块的接收信号为有效时,该模块将持续从介质访问控制子层模块接收IP帧并解析。首先解析IP 首部,再根据IP 字段进行协议分层:当IP 协议字段为01,则解析出ICMP 数据报文;当IP 协议字段为17,则解析出UDP 数据报文;当IP 协议字段为06,则解析出TCP 数据报文;将解析的协议报文存入缓存。随后进入发送模块,将IP 首部依次与TCP、UDP、ICMP 协议的首部及数据部分进行组帧;最终IP 报文封装完毕,发送IP 报文。

图4 IP 接收模块状态转移图

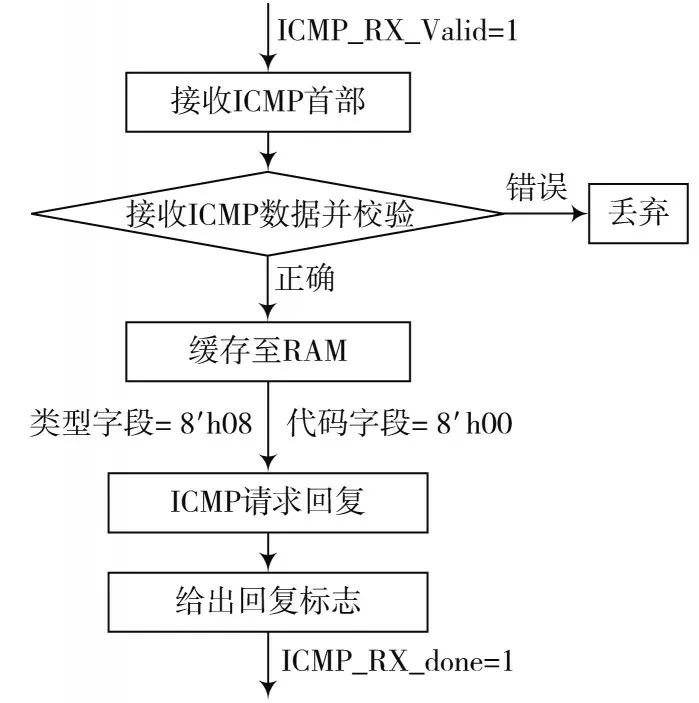

1.2.3 网络控制报文协议模块设计

ICMP 模块设计主要分为两个模块:一个是ICMP 接收模块,另一个是ICMP 发送模块。如图5 所示为ICMP接收模块工作时的一个状态转移图。当接收模块的接收信号为有效时,该模块将持续从IP 模块接收ICMP帧。首先接收ICMP 首部,其次对ICMP 数据边接收边校验,将错误的数据丢弃,正确的数据缓存至RAM。对校验正确的ICMP 数据进行判断:类型字段是否为08;代码字段是否为00。若这两个条件都可以满足,即触发ICMP 请求回复机制,并给出回复标志,进入到ICMP 发送模块。发送模块进入回显应答状态。首先将ICMP 报文的首部及数据部分进行组帧;然后将类型字段与代码字段都设置为00 置于首部;最终ICMP 报文封装完毕,发送ICMP 报文。

图5 ICMP 接收模块状态转移图

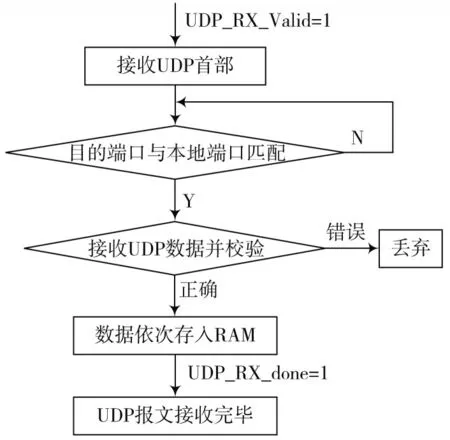

1.2.4 用户数据报协议模块设计

UDP 模块设计主要分为两个模块:一个是UDP 接收模块,另一个是UDP 发送模块。如图6 所示为UDP 接收模块工作时的一个状态转移图。

图6 UDP 接收模块状态转移图

当接收模块的接收信号为有效时,该模块将持续从IP 模块接收UDP 首部,接收完毕后对目标端口与PC 本地端口两者进行判断:只有两者匹配的情况下,才接收UDP 数据并校验。将错误的数据丢弃,正确的数据缓存至RAM。最后给出回复标志,表明UDP 报文接收完毕,进入发送模块。发送模块首先从RAM 中读取UDP 数据;然后将UDP 首部及数据部分组帧;最终UDP 报文封装完毕,发送UDP 报文。

1.2.5 传输控制协议模块设计

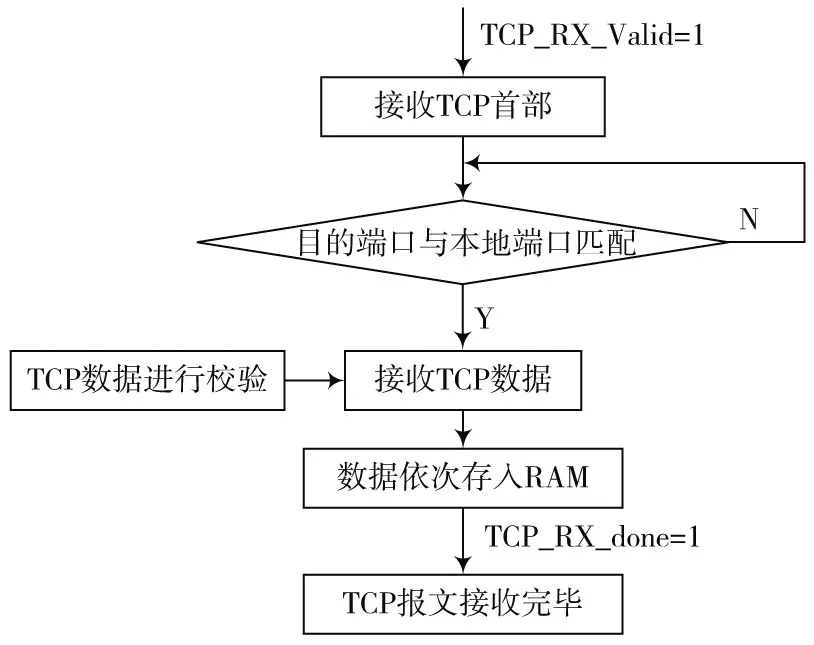

TCP 模块设计主要分为四个模块:TCP 接收模块、TCP 发送模块、TCP 接收发送控制模块、TCP 流量控制模块。如图7 所示为TCP 接收模块工作时的一个状态转移图。当接收模块的接收信号为有效时,该模块将持续从IP 模块接收TCP 首部,接收完毕后对目标端口与PC本地端口两者进行判断:只有在两者匹配的情况下,才能接收TCP 的数据部分,并对它进行校验,将正确的数据缓存至RAM。最后给出回复标志,表明TCP 报文接收完毕,进入发送模块。发送模块首先从RAM 中读取TCP 数据;然后将TCP 首部及数据部分进行组帧;最终TCP 报文封装完毕,发送TCP 报文。

图7 TCP 接收模块状态转移图

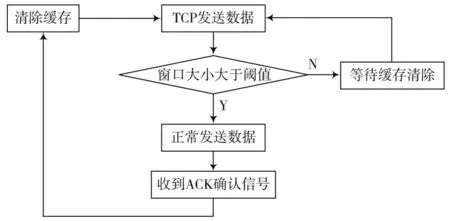

TCP 接收发送控制模块的主要功能是:从TCP 接收和TCP 发送这两个模块中接收到各种TCP 帧类型的标志,然后根据接收数据格式,给出需要发送的TCP 数据格式标志。如图8 所示为TCP 流量控制模块工作时的一个状态转移图。

图8 TCP 流量控制模块状态转移图

TCP 发送模块开始发送数据,并对窗口大小与阈值进行判断:若窗口大小大于阈值,则继续发送数据;若窗口大小小于阈值,则等待直到窗口大小达到要求。TCP发送模块正常发送数据时,若未收到ACK 确认信号,需将数据缓存并占用窗口的内存,直至收到ACK 确认后才能清除缓存,接着发送TCP 数据。这样有效解决了TCP发送缓存队列问题,简化了滑动窗口设计,避免拥塞。

2 系统测试

2.1 测试平台搭建

如图9 所示为本文搭建的万兆以太网通信硬件测试环境平台。该测试平台选用黑金AX7325 FPGA 开发板,开发板具有4 路光纤接口,10G 光纤连接到开发板的OPT1 口。下面将设计的整个系统程序在FPGA 开发板中进行测试。

图9 测试环境平台图

2.2 ARP 请求与应答测试

通过Wireshark 软件抓取ARP 请求与应答测试结果,如图10 所示。在FPGA 服务器端和PC 客户端进行通 信 后,PC 客 户 端(10.1.212.10)向FPGA 服 务 器 端(10.1.212.209)发起了ARP 请求,FPGA 服务器端收到请求后迅速应答,并告知其对应的MAC 地址是:00_0a_35_02_9d_e5。PC 客户端收到对应目标MAC 地址,将其存入缓存RAM。

图10 ARP 请求与应答测试结果图

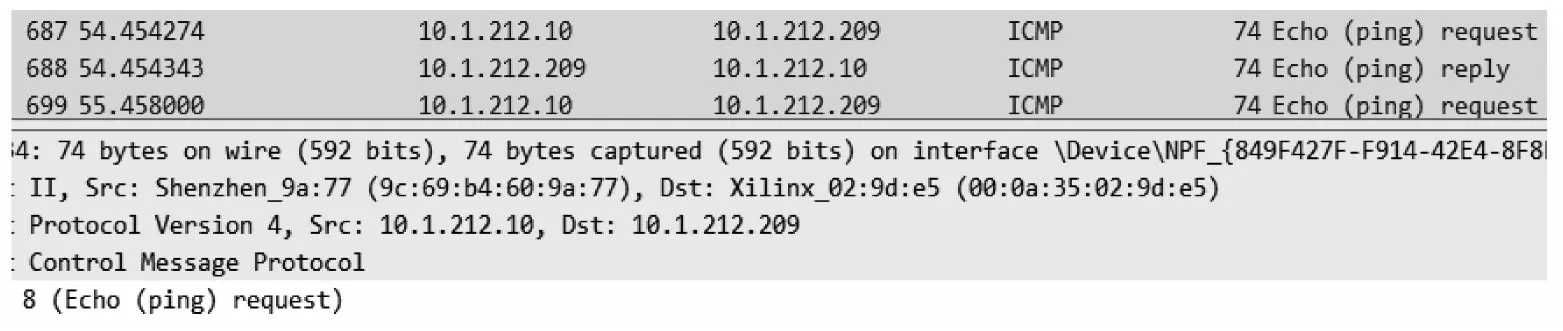

2.3 ICMP 回显请求与应答测试

通过客户端命令控制界面执行Ping 指令进行ICMP 回显测试,通过Wireshark 软件抓取ICMP 请求与应答测试结果如图11 所示。PC 客户端(10.1.212.10)向FPGA 服务器端(10.1.212.209)发起了ICMP 回显请求,FPGA 服务器端收到请求后迅速给出ICMP 回显应答。测试结果表明ICMP 回显测试正确,且应答速度快。

图11 ICMP 请求与应答测试结果图

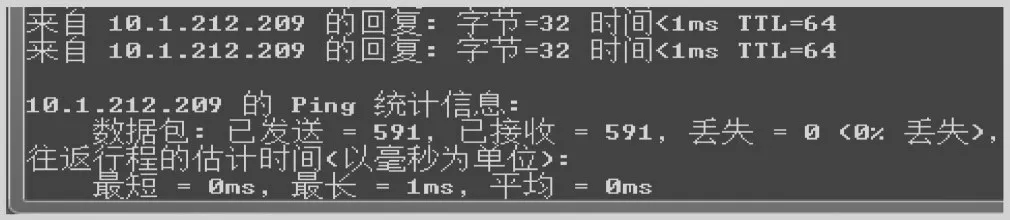

如图12 所示,在客户端的命令控制界面执行Ping指令,指令执行大约10 min,测试结果表明,服务器端发送591 个包、客户端接收到591 个包,无数据包丢失,表明双方链路传输稳定,以太网连接成功。

图12 Ping 测试图

2.4 TCP 通信基本功能测试

整个TCP 通信过程中,TCP 客户端需要经历以下几个过程:建立连接、发送数据、接收确认回复、断开连接。客户端与服务器端的连接与断开需要在电脑端通过Python 程序实现。

如图13 所示,通过Wireshark 工具捕获TCP 通信过程前三个过程。通过序号1814、1815、1816 的报文“三次握手”实现TCP 通信连接。

图13 TCP 基本通信结果图

其中序号1814 为PC 客户端发送的TCP 同步报文;序号1815 为FPGA 服务器端回应的连接同步报文;序号1816 为客户端向服务器端发送确认SYN 已收到,实现成功连接。序号1817 为客户端发送的TCP 数据报文,其总长为59 B,负载数据长度为5 B;序号1818 为FPGA 服务器端回应的ACK 报文,此时ACK 序号由原来的1 更新为6,实现正确应答。

在TCP 通信测试最后,需要进行通信断开操作。如图14 所示,利用Wireshark 工具捕获TCP 通信测试的最后断开过程。通过序号10951、10952、10953 和10954的报文“四次挥手”实现TCP 通信断开。

图14 TCP 通信断开图

其中序号10951 为客户端发送的TCP 请求断开报文;序号10952 报文为FPGA 服务器端对客户端进行的ACK 确认回应;序号10953 报文为FPGA 服务器端对客户端再次发送请求断开报文;序号10954 报文为客户端做出ACK 确认回应,完成双方的TCP 断开连接。

3 结 语

本文设计了一种基于FPGA 的万兆以太网TCP/IP传输系统,该设计对主要模块TCP/IP 协议栈模块自顶向下进行了模块化设计。对设计的传输系统进行了全面的性能测试,通过Wireshark 软件对ARP、ICMP 协议进行请求与应答测试,并成功地完成对客户端(PC)与服务器端(FPGA)之间的以太网连接和TCP/IP 协议的数据传输,且传输过程持续稳定,无数据丢失。测试结果表明,本文设计的万兆以太网TCP/IP 传输系统符合实验要求,可以将该传输系统更好地应用在核物理实验,且前景光明。