基于MOCVD三步生长的GaAs/Si外延技术

2022-02-23王嘉宾王海珠刘伟超王曲惠邹永刚马晓辉

王嘉宾, 王海珠*, 刘伟超, 王曲惠, 范 杰, 邹永刚, 马晓辉

(1. 长春理工大学 重庆研究院, 重庆 401135;2. 长春理工大学 高功率半导体国家重点实验室, 吉林 长春 130022)

1 引 言

大数据时代的到来极大地振兴了集成电路的发展,而且对其提出了更高的要求,即具有更加快速高效的获取与处理信息的能力[1]。硅基光电子可以实现光互联,突破传统电互联导致的延时和功耗方面的瓶颈[2]。然而,Si是间接带隙半导体材料,不具有良好的发光性能。通过单片集成的方式,Si上异质外延Ⅲ-V族半导体材料进而实现硅光子芯片上Ⅲ-Ⅴ材料激光器的制作成为近年来实现硅基片上光源的研究热点[3-6]。而且单片集成方式可以与硅光子工艺同步缩小线宽,在大规模光子集成芯片的研制中具有巨大潜力,成为硅光子技术的主要方向[7]。并且在制造激光器、光电探测器、太阳能电池等传统Ⅲ-Ⅴ器件时,硅基砷化镓(GaAs-on-Si)晶圆在取代昂贵的GaAs晶圆方面具有巨大的市场潜力[8]。因此,针对Si上异质外延高质量的GaAs材料的研究十分重要。

然而,Si 与GaAs材料间的匹配存在以下三个问题[9]:(1)具有较大的晶格失配,可以达到4%左右,因此,在Si上异质外延生长GaAs时会出现应力弛豫所产生的高密度穿透位错;(2)具有较大热失配,可以达到59%左右,产生的热应力会导致进一步的晶格失配,最后产生微裂缝;(3)材料极性/非极性界面将导致反相畴,反相畴是一种平面位错,会产生非辐射复合中心,降低晶体质量。在过去三十多年间,许多提升GaAs/Si异质外延层晶体质量的方法陆续被提出,其中包括多步生长法[10-11]、循环热退火法[12]、应变超晶格位错阻挡层[13-15]、量子点位错阻挡层[16]、选择性区域生长[17-18]、使用Ge、SiGe缓冲层[19-20]等方法,并取得了令人称赞的实验结果。2015年,中国香港科技大学Li等[18]通过干法刻蚀,实现了Si(001)衬底上二氧化硅条纹图案,之后利用KOH溶液湿法刻蚀在沟槽底部形成Ⅴ型槽(111)面。在(001)Ⅴ型槽Si衬底上生长切面光滑和低缺陷密度的砷化镓纳米线,在纳米线中生长出大面积的GaAs薄膜,生长2 μm厚度的GaAs薄膜的摇摆曲线[110]方向峰值半高宽(FWHM)为154″。2016年,北京邮电大学胡海洋等[16]利用金属有机化学气相沉积(MOCVD)技术,优化了多层InAs/GaAs量子点位错阻挡层的生长条件,采用三步生长法结合量子点位错阻挡层的方式提高GaAs晶体质量,生长3 μm厚度GaAs的腐蚀坑密度(EPD)为9×105cm-2。同年,中科院半导体所刘广政等[11]利用MBE技术,采用四步生长法在硅衬底上生长GaAs材料,与两步生长法相比显著减少了穿透位错,中间两层的低温、高温GaAs缓冲层保护不稳定的成核层,提升了GaAs晶体质量与表面形貌,生长厚度1 μm的GaAs外延层表面粗糙度为2.1 nm,由XRD FWHM估算的穿透位错为1.9×107cm-2。2019年,米兰工业大学Ballabio等[20]在深沟槽的Si图形化衬底上利用低能等离子体增强化学气相沉积(LEPECVD)生长悬浮的厚Ge层,利用迁移增强外延(MEE)和分子束外延(MBE)沉积GaAs薄膜,其表面5 μm×5 μm区域均方根粗糙度为2.2 nm。光致发光测量结果表明,在该砷化镓层上实现的AlGaAs/GaAs量子阱结构具有良好的均匀性和较高的光学质量。毫无疑问,不处理衬底表面图案且仅使用一种设备外延的方案是更加经济与简单的,为了获得高晶体质量外延层,这对GaAs/Si异质外延中初始阶段GaAs外延层的生长提出了更高要求,因此针对GaAs/Si异质外延的低温成核层的研究极具意义。同时,本文为了进一步获得高质量硅基砷化镓薄膜,通过MOCVD技术,利用优化后的GaAs低温成核层的生长条件,分析并验证采用三步生长及循环热退火方法对Si衬底直接外延生长GaAs材料表面形貌和晶体质量的影响。

2 实 验

利用德国AIXTRON公司的200/4型MOCVD开展GaAs/Si异质外延生长研究。以三甲基镓(TMGa)为Ⅲ族源,砷烷(AsH3)为Ⅴ族源,氢气(H2)作为载气,反应室压力保持在10 000 Pa(100 mbar)的条件下进行生长实验。外延生长采用Si(100)偏向<011>晶向4°衬底,用来抑制反相畴的形成。生长前需要对Si衬底进行去氧化处理,否则非晶状氧化层会严重影响GaAs外延层的生长质量。首先,将Si衬底用10%氢氟酸溶液漂洗30 s,可以去除表面大部分的氧化物。经氮气吹干后送入反应室,在750 ℃下退火/烘烤15 min,使剩余氧化物解吸。

在生长过程中,GaAs低温成核层(Low temperature GaAs nucleation layer,LT-GaAs layer)在390 ℃下通入AsH3流量4.5×10-3mol/min、TMGa流量1.8×10-5mol/min,GaAs高温外延层(High temperature GaAs epilayer)和更高温度GaAs外延层(Higher-temperature GaAs epilayer)在600 ℃/650 ℃下通入AsH3流量2.7×10-3mol/min、TMGa流量4.1×10-5mol/min。

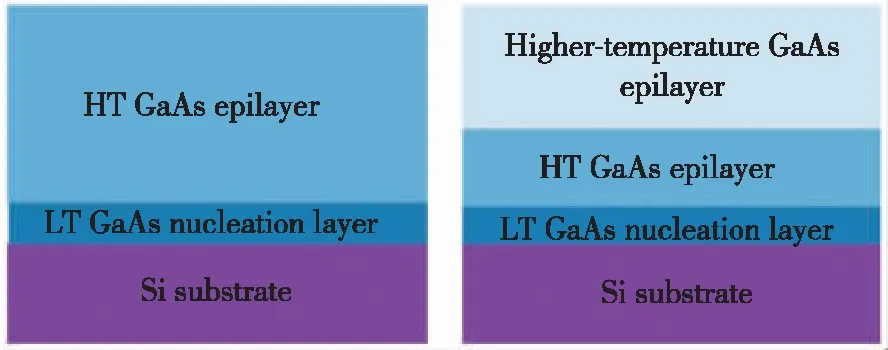

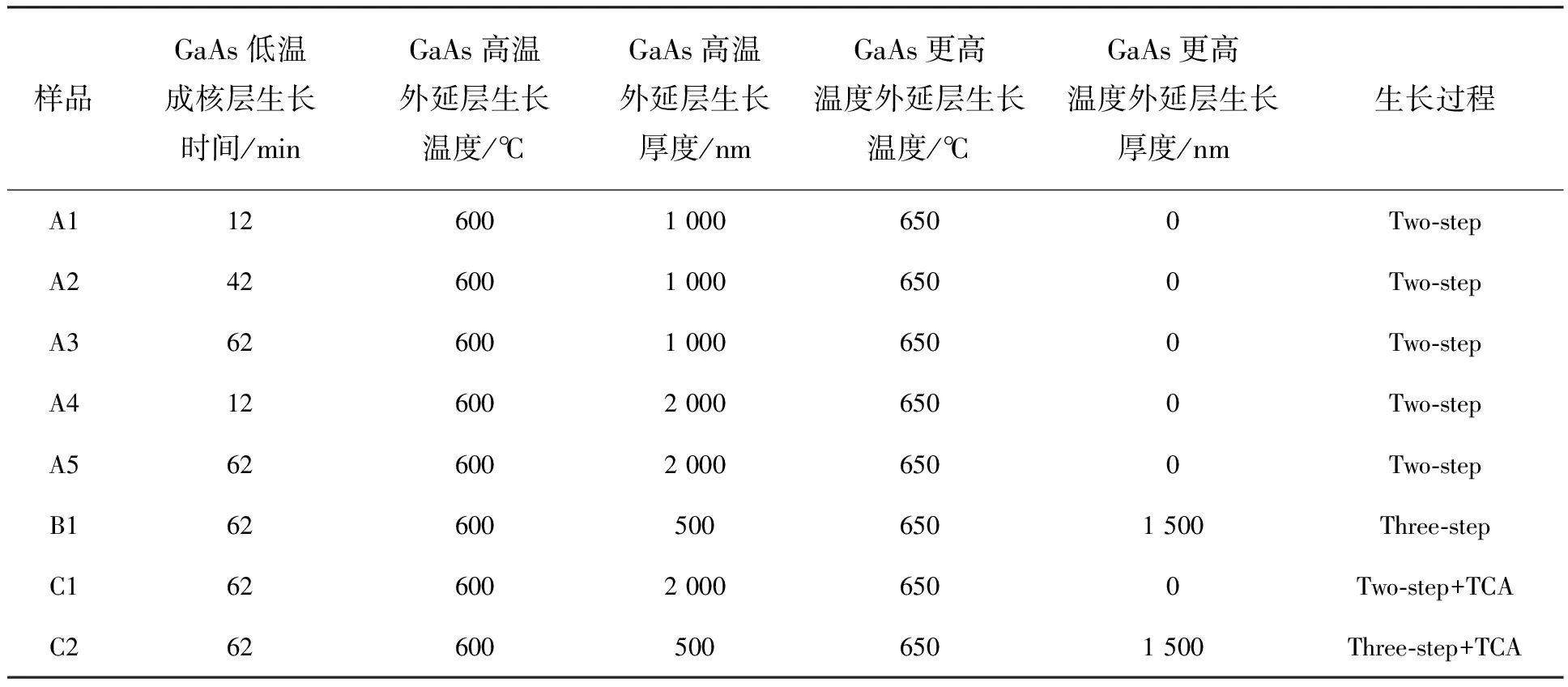

为了确定低温成核层最佳生长厚度以及对比研究GaAs/Si两步生长和三步生长对GaAs晶体质量的影响,设计了如图1所示的两种外延结构。其中详细的生长参数如表1所示。利用两步生长结构生长样品,高温外延层生长温度为600 ℃,厚度为1 000 nm。低温成核层生长时间为0~122 min,对低温成核层生长时间为12,42,62 min的样品分别编号为A1、A2、A3。设计样品A4、A5分别与样品A1、A3对比,研究增加高温外延层厚度对GaAs外延层生长质量的影响。样品B1采用三步生长结构,其中低温成核层生长时间为62 min,高温外延层和更高温度外延层生长温度分别为600 ℃和650 ℃,厚度分别为500 nm和1 500 nm。在A5、B1生长过程结束后进行循环热退火(Thermal cycle annealing,TCA)的样品编号C1、C2。每个TCA步骤包括三个周期,在每个周期内将GaAs/Si晶圆加热到740 ℃并保持5 min,然后降温至370 ℃并保持5 min。并且整个循环热退火过程在AsH3、H2混合气体的氛围中进行。

注1 GaAs两步生长(左)和三步生长(右)外延结构示意图

表1 实验样品生长结构参数

本文采用台阶仪(Alpha-Step D-300)对样品表面粗糙度进行初步表征。利用原子力显微镜(AFM,Bruker ULTIMODE8)表征GaAs/Si外延层的表面形态。利用扫描电子显微镜(SEM,FEI QUANTA FEG250)表征样品截面特征。通过高分辨率X射线衍射(HRXRD,Bruker D8 DISCOVER)ω扫描测量GaAs(004)衍射峰的FWHM值,评估GaAs晶体质量;通过ω-2θ扫描衍射峰间距评估GaAs与Si间的残余应力。

3 结果与讨论

3.1 低温成核层生长时间选取

为了检验不同低温成核层厚度下生长的GaAs薄膜材料的质量,采用两步生长结构探究不同低温生长厚度对GaAs外延质量的影响。采用台阶仪对样品表面粗糙程度进行初步表征,生长样品的表面均方根粗糙度(Rq)、平均粗糙度(Ra)与GaAs低温成核层生长时间的关系如图2所示。由图可知,随着生长时间的增加,样品的表面粗糙度先减小后增大。当低温成核层生长时间为0 min时,获得的GaAs材料的表面粗糙度最大,约为其他样品的3~5倍。这是因为在Si上直接生长GaAs高温外延层最初的生长机制是岛状生长模式[21],较高的生长温度导致反应源裂解率和结合效率提升,原子迁移率和扩散距离增大,Si上GaAs快速形成尺寸较大且密度较小的岛屿,随着生长厚度的增加,形成了肉眼可观察到的雾状表面。然而随着低温成核层的介入,较低的生长温度导致原子扩散距离减小,形成了小尺寸、高密度的GaAs岛。在适当的时间,岛与岛之间可以很好地合并生长,在本文中成核层生长时间为62 min的样品具有最好的表面形貌。然而,随着生长时间增加到122 min,过厚的GaAs低温成核层会使样品表面质量恶化。

注2 样品的表面均方根粗糙度(Rq)和算数平均粗糙度(Ra)与GaAs低温成核层生长时间的关系

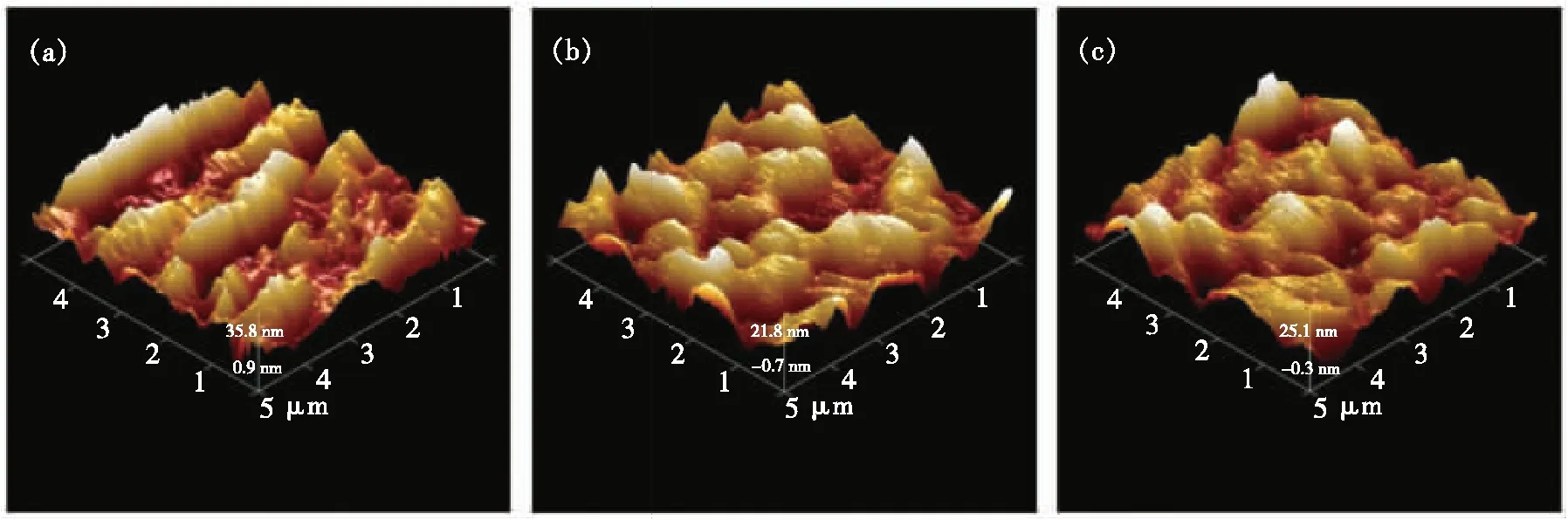

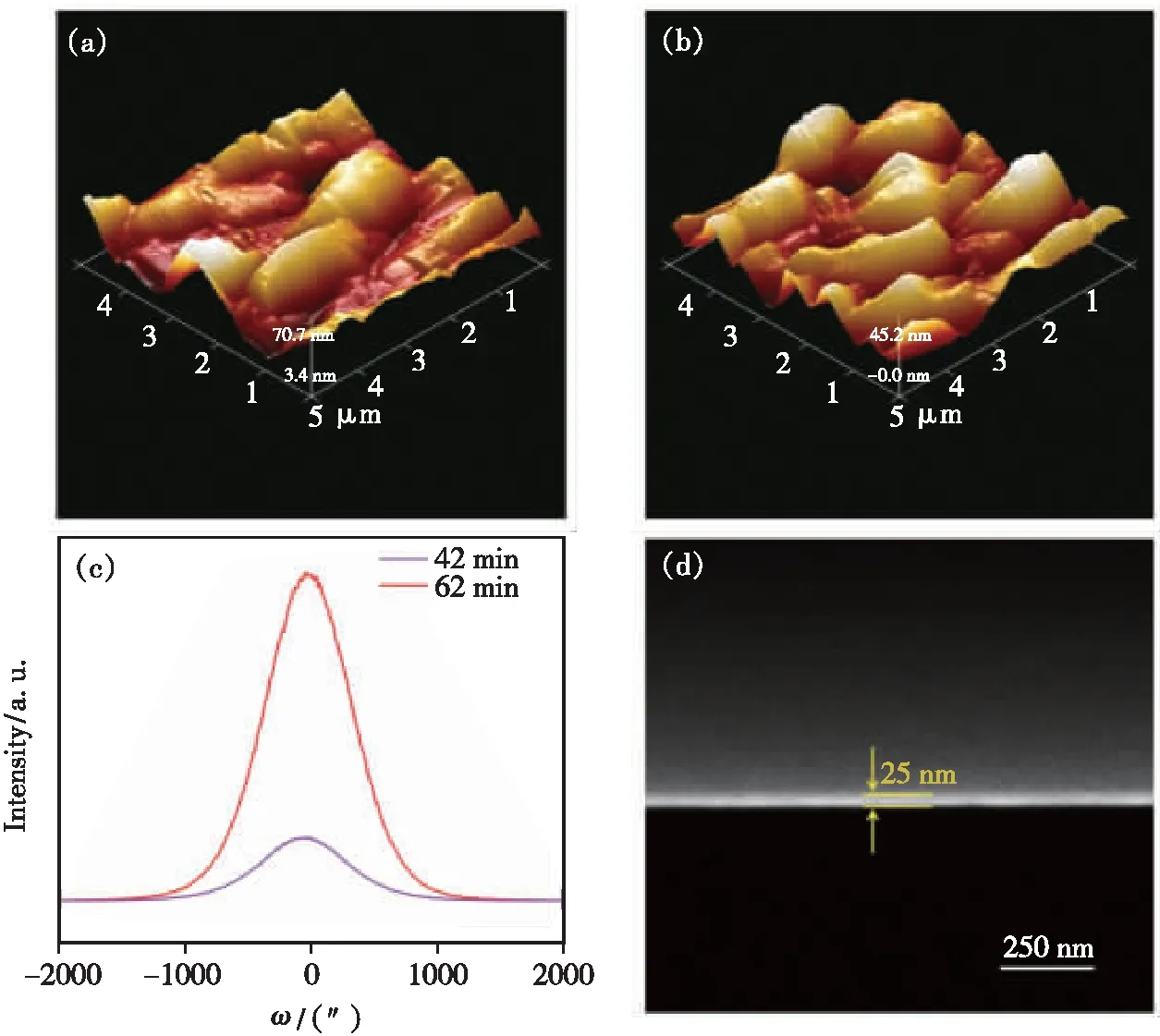

为了进一步观察GaAs低温成核层生长厚度对样品表面形貌的影响,我们对样品进行了AFM扫描。图3 (a)、(b)、(c)分别为样品A1、A2、A3的5 μm×5 μm AFM图像,对应低温成核层生长时间为12,42,62 min。不同样品均方根粗糙度分别为10.1,6.69,6.79 nm。从AFM图像中可以观察到,随着GaAs成核层生长厚度的增加,GaAs外延层表面的大尺寸岛屿逐渐减少,在低温成核层生长时间62 min时,图像中出现了大面积较为平坦的区域。

注3 不同生长时间(12,42,62 min)的低温成核层5 μm×5 μm AFM测试图像

低表面粗糙度和低缺陷密度是Si上生长GaAs材料所期望具有的特征,为了观察样品表面粗糙度随生长厚度增长的变化,制备了高温外延层厚度为2 000 nm的样品A4、A5。图4(a)、(b)分别是样品A4、A5的AFM图像,低温成核层生长时间为12 min、62 min的样品表面均方根粗糙度分别为18.8 nm、14.6 nm。随着高温外延层厚度的增加,低温成核层生长时间为12 min的样品表面粗糙度依然大于62 min的样品表面粗糙度。这说明在生长过程中初始GaAs的表面粗糙程度决定之后生长的GaAs表面形貌,62 min的低温成核层生长时间显然可以使两步生长样品具备较为平滑的表面。同时我们注意到,随着生长厚度增加,样品表面粗糙度也有所增加。这是由于低温成核层形成的岛屿没有完全合并成近似的平面,随着生长的继续进行,GaAs表面岛屿相互汇集致使密度进一步减小,尺寸进一步增大,从而导致表面形貌随着生长厚度的增加而恶化。

为了评估表面粗糙度相近的样品A1、A2,我们对样品进行了XRDω扫描测试。如图4(c)所示,从XRD测量GaAs(004)摇摆曲线中可以看到,低温成核层生长时间为42 min和62 min时,摇摆曲线半峰宽(FWHM)分别为727″和707″。通过XRD的FWHM值评估晶体的穿透位错密度(TDD),可以非常直观地反映材料的结晶质量,两者关系可以用公式(1)表示[22]:

(1)

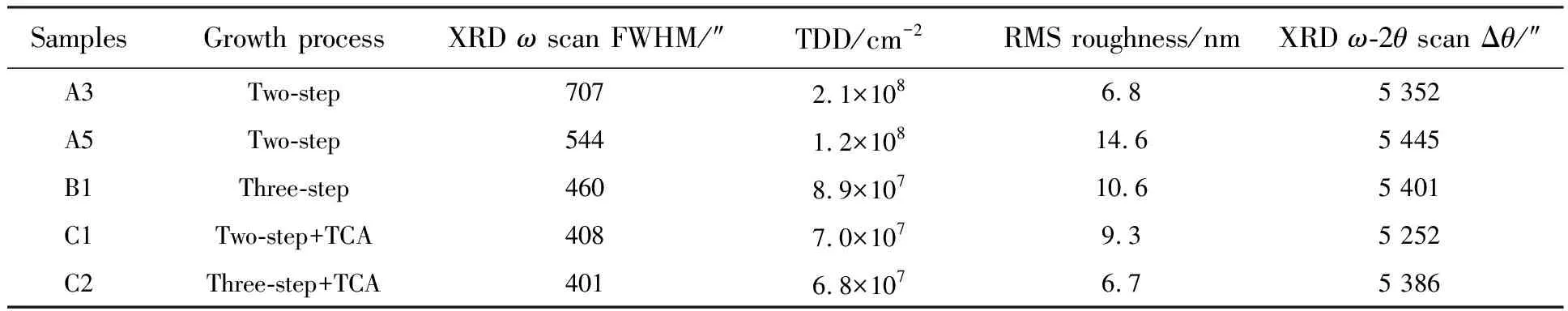

然而,通过公式(1)的计算,两个样品中仍然具有108cm-2量级的穿透位错密度。通过比较样品A3、A5的XRDω扫描FWHM值,测试结果如表2所示,增加高温外延层厚度可以实现晶体质量的改善。为了进一步降低穿透位错密度,本文通过采用确定的低温成核层生长时间62 min,在增加高温外延层厚度的基础上采用三步生长、循环热退火等方法进一步提升晶体质量。

注4 (a)~(b)样品A4、A5的AFM图像;(c)样品A2、A3的GaAs(004)XRD ω扫描摇摆曲线;(d)Si上生长62 min GaAs低温成核层的截面图像。

表2 不同生长过程的样品的XRD ω 扫描FWHM、TDD(来自FWHM计算)、均方根粗糙度、ω-2θ扫描衍射峰间距

3.2 利用三步生长和循环热退火生长研究

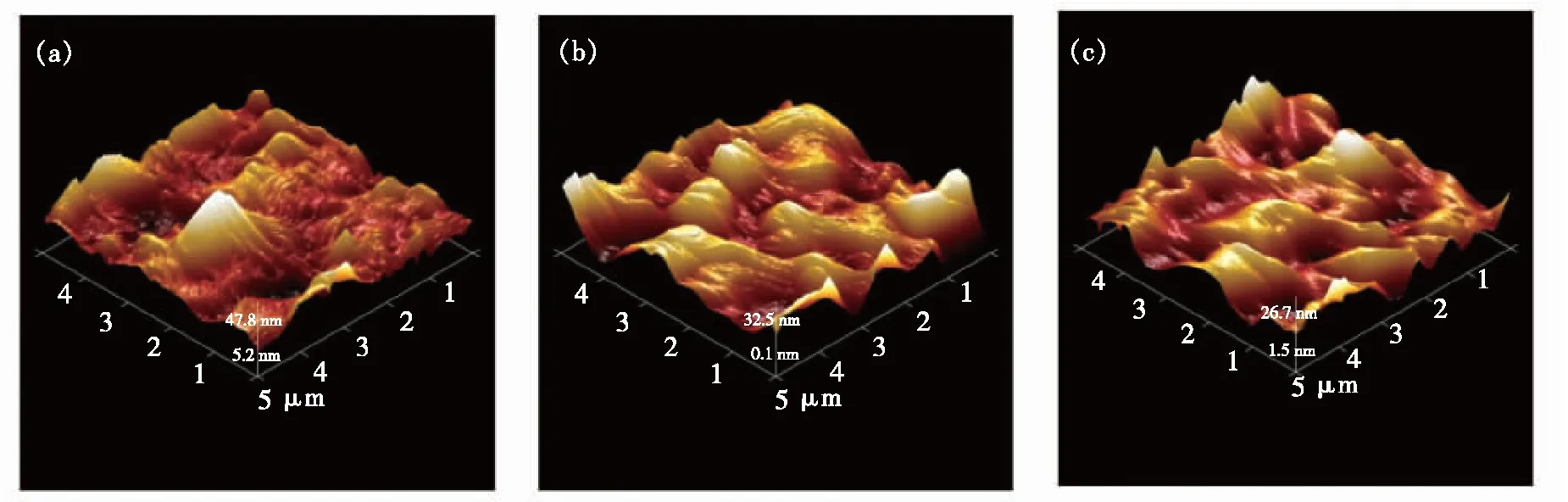

为了观察采用三步生长和循环热退火对GaAs表面形貌的影响,对样品B1、C1、C2进行AFM测试。如图5所示,样品B1、C1、C2的5 μm×5 μm范围均方根粗糙度分别为10.6,9.29,6.71 nm。对比未采用TCA两步生长样品A5(14.6 nm)与三步生长样品B1(10.6 nm)和采用TCA样品C1(9.29 nm),采用三步生长和TCA可以降低表面粗糙度,使表面形貌得到提升。而采用三步生长和TCA结合的方法增强了降低粗糙度的效果。

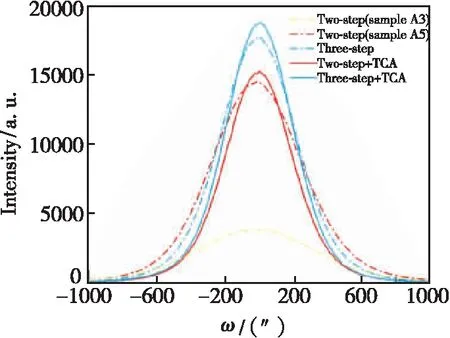

为了进一步验证三步生长和TCA对GaAs晶体质量的影响,我们对样品进行了XRDω扫描测试,测试结果如图6所示。对比未采用TCA两步生长样品A5与三步生长样品B1以及采用TCA的样品C1的XRDω扫描摇摆曲线的FWHM值,再利用公式(1)估算出样品的穿透位错密度,如表2所示。结果发现,三步生长和循环热退火方法都可以有效地降低穿透位错密度,提升了GaAs的晶体质量。采用TCA三步生长样品C2的FWHM值相比于未采用TCA两步生长样品A5降低了143″,穿透位错密度从1.2×108cm-2降到6.8×107cm-2。结合样品表面的粗糙度测试结果,同时采用三步生长与循环热退火生长GaAs,不仅可以很好地改善GaAs表面形貌,而且进一步提升了GaAs的晶体质量。据文献报道[23],在热退火过程中两个伯格斯矢量接近60°的穿透位错会融合或湮灭,在TCA期间由于GaAs与Si之间热膨胀系数的差异引起的热应力会迫使穿透位错滑动。三步生长对晶体质量的提高归因于650 ℃生长的更高温度外延层,这一过程相当于对之前生长的GaAs晶体进行一次原位退火,退火期间热应力发挥作用使部分位错滑移或消失,同样起到了降低GaAs外延层缺陷密度的效果。

图5 (a)~(c)样品B1、C1、C2的5 μm×5 μm AFM图像。

注6 样品A3、A5、B1、C1、C2的GaAs(004)XRD ω扫描摇摆曲线。

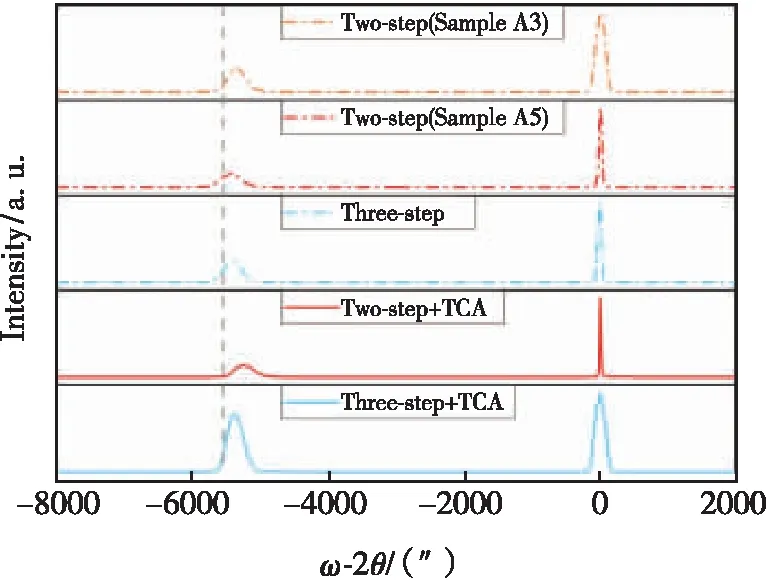

为了探究三步生长和循环热退火对GaAs残余应力的影响,我们对样品进行了XRDω-2θ扫描测试,结果如图7所示。GaAs的衍射峰和Si的衍射峰对应的布拉格角间距Δθ可以表征外延层与衬底间的应力状态,样片A3、A5、B1、C1、C2的Δθ值分别为5 352″、5 445″、5 401″、5 252″、5 386″,如表2所示。图7中灰色虚线对应着完全弛豫时GaAs衍射峰的位置,完全弛豫时GaAs与Si的Δθ理论值应为5 540″。GaAs的晶格常数和热膨胀系数都大于Si,因此GaAs在生长过程中受到的晶格失配应力是压应力,生长结束降温过程中受到的热失配应力是张应力。样品在室温下检测的残余应力是晶格失配压应力和热失配张应力共同作用的结果。所有样品衍射角间距都小于5 540″,GaAs衍射峰向高位偏移,这说明GaAs沿生长方向的晶格常数变小,热失配张应力在GaAs的残余应力中占主导地位。通过对比样品A3和A5,随着GaAs生长厚度的增加而Δθ趋近5 540″,由晶格失配导致的累积应力得到进一步释放。对比采用三步生长的B1与两步生长A5以及未采用TCA的样品A5、B1和采用TCA的样品C1和C2,三步生长和循环热退火过程减小了GaAs的衍射峰和Si的衍射峰间距Δθ,增大了GaAs与Si之间的张应力。热应力在促使GaAs中位错运动提升晶体质量的同时也增加了晶体内残余应力。

注7 测量样品的XRD ω-2θ扫描图像,由上至下生长过程分别为两步生长(样品A3)、两步生长(样品A5)、三步生长、两步生长+循环热退火、三步生长+循环热退火。

当然这种现象需要注意,残余应力不仅会存在于外延薄膜中,也会转移到之后的硅基GaAs器件中。过大的残余应力导致 GaAs薄膜出现微裂缝,严重影响芯片的良率与器件的性能[24-25]。因此,三步生长与循环热退火结合以减少残余应力的生长技术方法有待进一步发掘。

4 结 论

本文采用MOCVD生长技术开展了GaAs/Si异质外延生长技术研究。为获得较低缺陷密度且低粗糙度的GaAs薄膜,通过优化GaAs低温成核层生长时间,调控低温成核层生长厚度。结合台阶仪测试、XRDω扫描和AFM测试探究GaAs低温成核层厚度对GaAs外延材料质量的影响,分析测试结果确定了最佳的GaAs低温成核层生长时间62 min(生长厚度约25 nm)。引入更高温度外延层的三步生长法和循环热退火方法通过热应力的作用有效地降低了GaAs缺陷密度和表面粗糙度,然而不可避免地增大了GaAs中的残余张应变。采用三步生长法与循环热退火结合的方法获得了GaAs(004) XRD摇摆曲线FWHM为401″、缺陷密度为6.8×107cm-2、5 μm×5 μm区域内表面粗糙度为6.71 nm的GaAs外延材料。

本文专家审稿意见及作者回复内容的下载地址:http://cjl.lightpublishing.cn/thesisDetails#10.37188/CJL.20210378.