一种基于小间距LED显示驱动的SRAM 控制器设计与实现

2022-02-17范学仕唐茂洁李鸣晓

范学仕,王 松,唐茂洁,李鸣晓

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

随着LED显示驱动技术的更新换代,小间距LED显示驱动正逐步成为主流技术[1-2]。相比于传统显示屏,具有高密度、高清晰度、宽角度、高亮度、高刷新率、高对比度、智能控制、节能环保等多种技术优势的高端小间距LED显示屏成为重点发展的对象[3-4]。多路恒流LED 驱动芯片通过串行数字信号和PWM 配合使用,具有匹配性好、电流控制精准、显示灰度高的特点,可以达到良好的显示效果,在小点间距LED 驱动芯片中得到广泛应用[5-6]。随着5G+8K显示技术的逐渐成熟,照明设备、显示屏及其他电子设备等显示驱动产品的发展推动着存储技术的发展,大规模数据计算和传输对存储器性能提出越来越高的要求[7-8]。

在多行扫多通道恒流LED显示驱动芯片中,为节省带宽、提高刷新率、降低功耗和面积,数据的读写是同时进行的[9]。常用的做法有两种,一是采用两块大小相同的SRAM 分别进行读写操作;二是采用双端口SRAM 实现同时读写的操作[10-11]。第一种做法不仅增加了IP 的成本和芯片面积,还增加了实现的复杂度,同样增加了芯片的面积。第二种方法采用双端口的SRAM,受限于不同的工艺厂商和IP 厂商,可供选择的双端口SRAM 屈指可数,极大地限制了产品的迭代升级,同时成本也大幅度增加[12]。

本文针对小间距LED显示驱动的应用背景,突破常规选择,打破局限,选用通用类型的SRAM IP 设计了一种SRAM 控制器。

2 SRAM 控制器电路设计与实现

2.1 总结架构设计

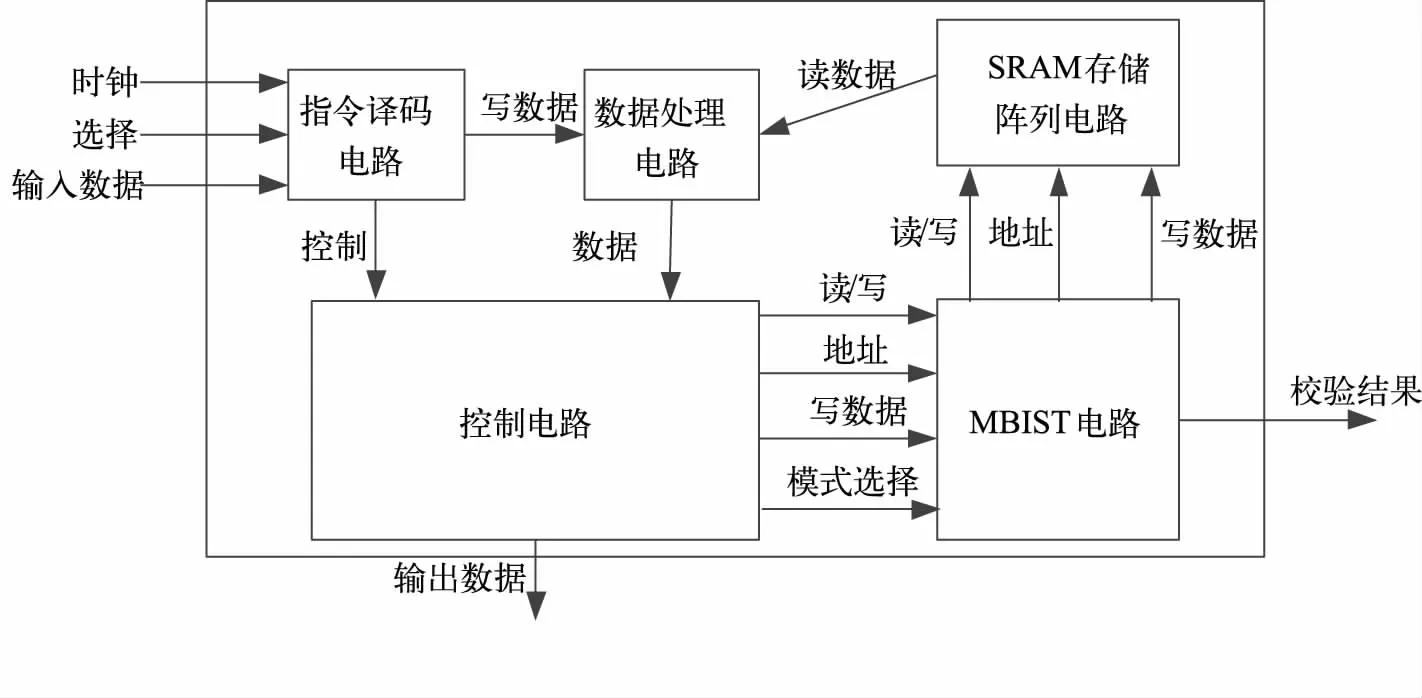

基于小间距LED显示驱动的SRAM 控制电路结构如图1 所示[13]。整个控制器电路由指令译码电路、控制电路、数据处理电路、MBIST 电路和SRAM 存储阵列电路5 个部分组成。指令译码电路根据输入的时钟信号、选择信号和输入数据信号,译码成相应的控制指令和写入数据;控制电路生成读/写信号、地址信号、写数据信号和模式选择信号等SRAM 相关控制信号;数据处理电路完成输入数据、读出数据和预读取数据等数据处理;MBIST 电路根据模式选择信号对SRAM 进行校验,并将校验结果输出;SRAM 存储阵列电路用于数据存储。

图1 SRAM 控制器电路结构

2.2 指令译码电路设计

指令译码电路在输入时钟的驱动下,根据选择信号的长短和串行输入数据将输入信号译码成相应的模式选择控制信号和写入到SRAM 的并行LED显示数据,指令译码时序如图2 所示。通过记录选择信号高电平期间时钟信号上升沿的个数,选择进入MBIST校验模式或者进入SRAM 读/写数据模式。时钟最高频率为50 MHz,当记录高电平个数为X 时,进入MBIST 校验模式;记录高电平个数为Y 时,进入SRAM 读模式;记录高电平个数为Z(X、Y、Z 均可自行定义)时,进入SRAM 写模式,并将串行输入数据通过移位寄存器转换为并行数据传递到数据处理电路中。

图2 指令译码时序

为进一步降低系统功耗,通过时钟门控电路,关闭暂时用不到的芯片部分如触发器、逻辑门等。节约的功耗主要是开关电容的降低以及开关系数的减小,原因是当时钟频率处于闲置状态时,一些不必需的晶体管被关闭,在整个模块不工作时就可以节省大量的功耗。这种时钟门控的状态机是有限的,并且包含在RTL 代码中。在实际芯片工作过程中,只有数据读写,SRAM 才会工作,因此对于SRAM 的读写时钟采用门时钟电路处理,只有在读写信号发生时才会工作,从而达到降低功耗的目的。

2.3 控制电路设计

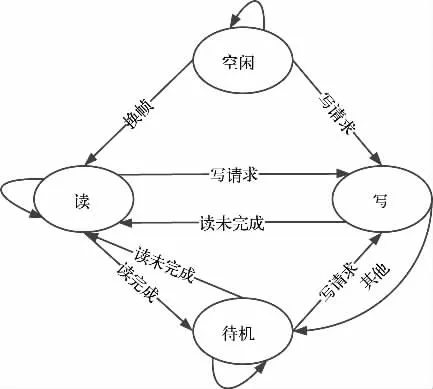

控制电路包括:(1)状态机电路,实现读、写、空闲、待机4 种不同状态的切换;(2)地址生成电路,生成写入数据对应的SRAM 地址信号;(3)时钟生成电路,生成SRAM 的读写时钟;读/写信号生成电路,生成SRAM 的读/写信号。

状态机电路实现读、写、空闲、待机4 种不同状态的切换,完成SRAM 数据的读取和写入。上电复位之后系统处于空闲状态,根据读请求信号/写请求信号跳转到相应的读/写状态,当读写同时发出请求时,优先处理写操作。

指令译码电路每译码一组写入SRAM 数据,地址生成电路将生成的写地址加1,直到写满一帧数据;系统从SRAM 每读出一组数据,地址生成电路将生成的读地址加1。此外地址生成电路增加地址溢出保护功能,防止超出地址范围的非法操作。

时钟生成电路根据状态机电路当前的工作状态和指令译码电路的读写请求,产生相应的读/写时钟信号,上升沿进行读/写操作。一组读时钟读出当前显示所需要的一组数据,一组写时钟每次写入一个显示数据。

读/写信号生成电路,根据时钟生成电路生成的读/写时钟信号,生成相应的读/写信号,读信号为高,即为“1”,写信号为低,即为“0”。读写操作相互独立,支持任意的读写操作。

所述控制电路状态跳转关系如图3 所示,总共包含空闲、读、写和待机4 种状态。系统在上电之后处于空闲状态,当换帧信号到来时,意味着开始进行数据显示,状态机跳转到读状态。在每一个读状态中,需要读取16 个通道的数据,当16 个数据全部从SRAM 中读出,读完成信号拉高,否则读未完成信号拉高。若在读状态中有写请求信号,则优先处理写操作,系统跳转至写状态。在写状态中,每一次写入一个通道数据,写完数据之后,根据读未完成信号的高低,跳转至读状态或者待机状态。在待机状态中,等待下一次写请求进入写状态或者读未完成进入读状态。

图3 系统状态跳转关系

2.4 数据处理电路设计

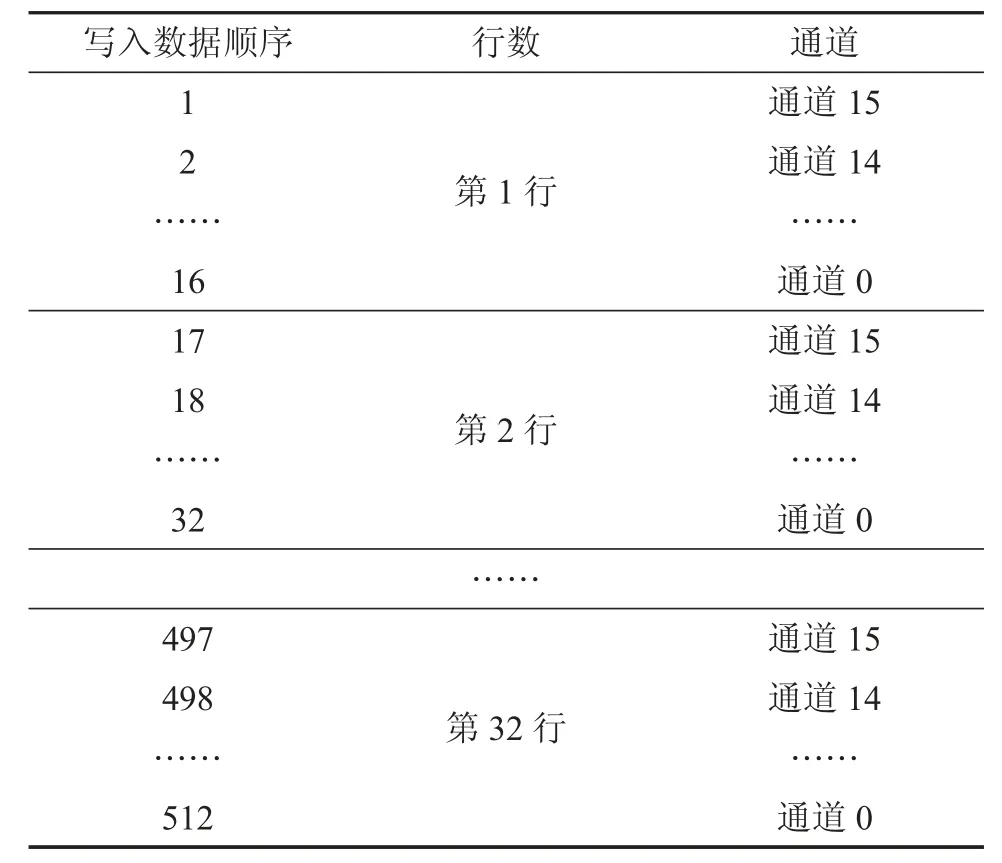

基于LED显示驱动的SRAM 控制电路,适用于多行扫多通道恒流LED 驱动芯片。现以32 行扫16 通道16 位灰度的恒流LED 驱动芯片为例,一帧数据的大小为32(行扫)×16(通道)×16 bit=8192 bit=8 kbit,两帧数据总共需要16 kbit 的SRAM 用于存放数据,SRAM 的地址为10 bit,数据为16 bit,图4 为所述SRAM 存放数据图。根据SRAM 的地址最高位将16kbit的SRAM 分为大小相同的两个8 kbit SRAM。低地址(0~10’h1FF)用于存放需要读取的当前显示的一帧数据,高地址(10’h200~10’h3FF)用于存放需要写入的下一帧显示的数据。读写操作可独立进行,互不干扰,在读取当前帧数据的同时,可以写入下一帧显示数据,以此进一步提高刷新率。

图4 SRAM 存放数据图

具体的写入SRAM 数据和显示的对应关系如表1 所示。通过指令译码将灰度数据第1 个16 bit 数据作为第1 行通道15 的数据,第2 个16 bit 数据作为第1 行通道14 的数据,……,第17 个16 bit 数据作为第2 行通道15 的数据,……,第512 个16 bit 数据作为第32 行通道0 的数据。

表1 写入SRAM 数据和显示的对应关系

2.5 MBIST 电路设计

为提高芯片可测性,本文通过MBIST 方式提供芯片可测性,进而保证芯片性能。MBIST 校验电路当指令译码生成的模式选择信号为高时,执行SRAM 校验操作,并将校验结果输出,用于判断SRAM 是否正常的具体校验过程如下。

(1)SRAM 地址从0 到10’h3FF:所有的SRAM写16’h5555;

(2)SRAM 地址从0 到10’h3FF:先读出(1)写入的16’h5555,再写入16’hAAAA;

(3)SRAM 地址从0 到10’h3FF:先读出(2)写入的16’hAAAA,再写16’h0000;

(4)SRAM 地址从0 到10’h3FF:先读出(3)写入的16’h0000,再写16’hFFFF;

(5)SRAM 地址从10’h3FF 到0:先读出(4)写入的16’hFFFF,再写16’hAAAA;

(6)SRAM 地址从10’h3FF 到0:先读出(5)写入的16’hAAAA,再写16’h5555;

(7)SRAM 地址从10’h3FF 到0:先读出(6)写入的16’h5555,再写16’hFFFF;

(8)SRAM 地址从10’h3FF 到0:读出(7)写入的16’hFFFF。

当(1)~(8)所有的写入读出全部正确,则SRAM校验正确,此时SDO 始终输出1;否则SRAM 校验错误,此时SDO 输出0。

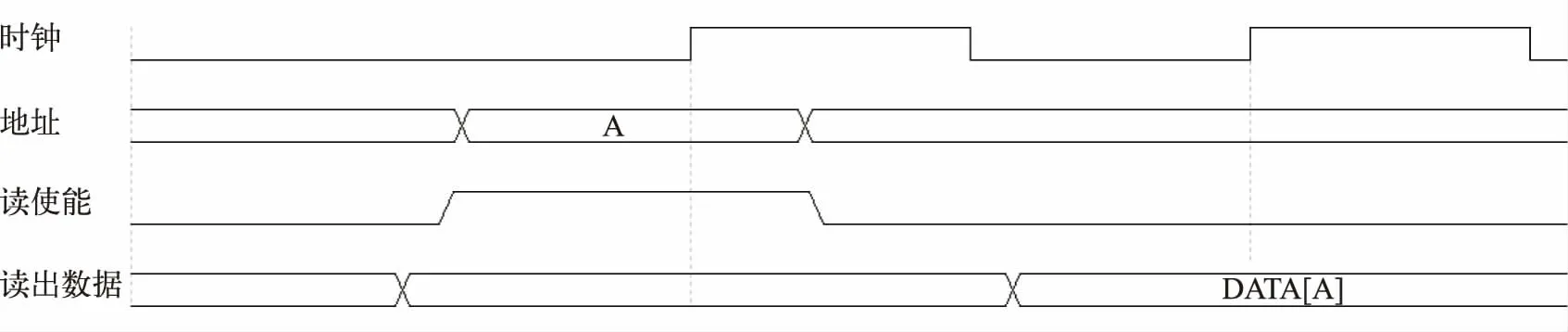

2.6 SRAM 存储阵列电路设计

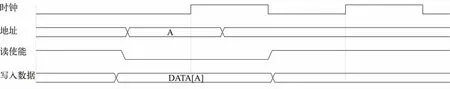

SRAM 读操作时序如图5 所示,在时钟上升沿,读使能信号拉高,从SRAM 的地址A 读出数据DATA[A]SRAM 写操作时序如图6 所示,在时钟上升沿,读使能信号拉低,将数据DATA[A]写入SRAM的地址A 中。SRAM 读写同时进行时的时序如图7 所示,SRAM 需连续读取地址A~A+3 的数据,在读取完地址A+1 的数据之后,出现写地址B 的操作,此时系统状态机跳转至写状态,在将DATA[B]的数据写入地址B 之后,继续之前未完成的读操作,将地址A+2 和地址A+3 的数据读出。

图5 SRAM 读操作时序

图6 SRAM 写操作时序

图7 SRAM 读写同时进行时的时序

3 结果及分析

本文提出的32 扫恒流PWM 输出LED 驱动芯片是一款全彩LED显示屏驱动芯片,内建PWM 高刷新算法,专门针对小间距显示屏存在的低灰问题做出优化处理,可以有效地解决传统的PWM 刷新率较低、灰度等级不高、低灰麻点、首行偏暗、开路十字架等问题。

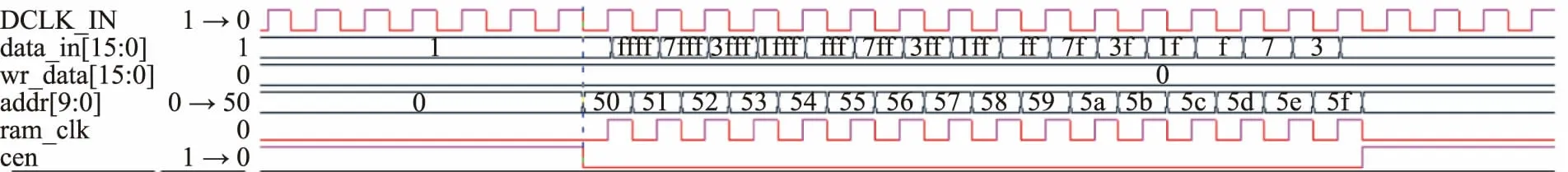

SRAM 正常读仿真时序如图8 所示,DCLK_IN 为时钟信号,data_in 为SRAM 读出的数据信号,wr_data为写入SRAM 的数据信号,addr 为SRAM 读写地址信号,ram_clk 为采用门控时钟技术之后的SRAM 读写时钟,cen 为SRAM 片选信号。cen 为低时,选择SRAM,此时依次从SRAM 的地址0x50~0x5f 读出数据0xffff、0x7fff、……、0x3、0x1。

图8 SRAM 正常读仿真时序

SRAM 读写冲突仿真时序如图9 所示,SRAM 正在从地址0x220~0x22f 中依次读出数据0xffff、0x7fff、……、0x3、0x1,但是在读完地址0x22a 后,系统向SRAM 发出写地址0x79 的请求(wr_en 为0),此时由于写优先级高,控制器暂停读操作,优先执行写操作,向地址0x79 写入数据0xff,写操作完成之后,继续读取0x22b 及之后的地址数据。

图9 读写冲突仿真时序

图10 为MBIST 按照2.5 节进行的正确校验过程,校验结果正确,sdo 始终输出1。

图10 MIBST 校验正确仿真时序

设计的芯片已完成流片,实测结果表明,仿真结果符合预期,测试验证结果与仿真一致(见表2)。

由表2 可知,采用该SRAM 控制器结构的芯片在整体面积上减少40%,在相同的数据量条件下,基于该SRAM 控制器的芯片在传输效率上提升近50%,级联个数提升50%。

表2 设计芯片与传统LED 驱动芯片测试结果对比

4 总结

本文介绍了LED 大屏显示的应用背景,以此提出对LED 大屏显示驱动电路的设计要求。接着对整体电路中的各个功能模块(控制电路、指令译码电路、数据处理电路、MBIST 电路)进行设计,并给出重要子电路参数的仿真波形。针对多行扫多通道恒流LED显示驱动芯片的SRAM 选择问题,突破常规选择,基于通用类型SRAM,分析并设计了一款基于小间距LED显示驱动的SRAM 控制电路,为相似设计提供了新的选择设计思路。实验结果表明该芯片面积减小40%,有效降低了成本;同时节省系统带宽,传输效率进一步提升了50%;降低了系统设计的复杂度。