QFN 器件焊接缺陷分析与工艺优化*

2022-02-17陈该青许春停

刘 颖,吴 瑛,陈该青,许春停

(1.中国电子科技集团公司第三十八研究所,合肥 230088;2.天地信息网络研究院有限公司,合肥 230088)

1 引言

QFN 封装沿封装本体底部四边通过金属端子与PCB 焊接实现电气连接,元件底部没有引线、焊球等,可以实现小的寄生电感和电阻,具有更好的电气性能。随着电子制造技术的不断进步,QFN 封装器件在航天产品中也有越来越多的应用,实现QFN 器件的高可靠焊接对组装工艺技术也提出了新的挑战和要求。热沉焊盘空洞、引脚虚焊、桥连、锡珠等是QFN 器件常见的焊接缺陷,在本单位某型号产品混合印制板电装后出现QFN 器件热沉焊盘焊接空洞、器件引脚间锡珠缺陷,本文通过对缺陷产生机理进行分析,并采取针对性的优化措施,提高了QFN 组装一致性,焊后缺陷率显著降低。

2 问题分析

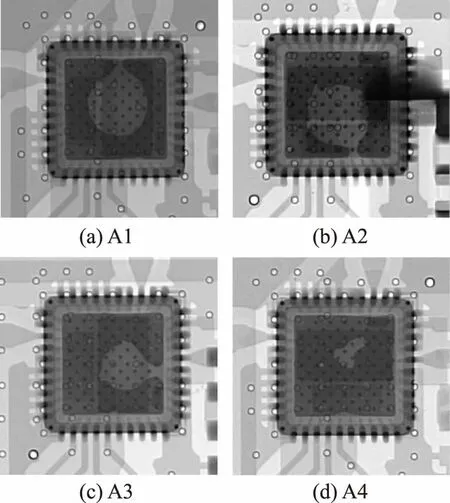

在印制板回流焊接后,使用X 光检测设备进行检测,印制板上QFN 器件底部大面积焊盘出现大的空洞,单个空洞尺寸约占焊盘面积的10%~30%,QFN 回流焊后X 光照片如图1 所示。该批次焊接的32 个通道产品中,30 个通道发现焊后大面积空洞缺陷,不良率为93.75%。同时,焊后采用OLYMPUS SZX7 体视显微镜放大40 倍检验焊点发现,芯片焊端出现较多锡珠缺陷。

图1 QFN 回流焊后X 光照片

关于QFN 大面积焊盘,目前未有标准对钎透率、空洞提出具体要求。IPC 对QFN 封装器件进行散热模拟,表明散热焊盘的空洞率低于50%时,不会导致散热性能降低,且散热焊盘区域的空洞不会影响周边焊点的可靠性,但居中散热平面的空洞会增加电路的电流路径,因此空洞的最大尺寸应该小于此平面内散热导通孔的间距[1]。初步分析认为,该缺陷的产生可能是由于印制板焊盘布局不合理、钢网设计不合理或焊接温度曲线不合理。

2.1 印制板焊盘布局

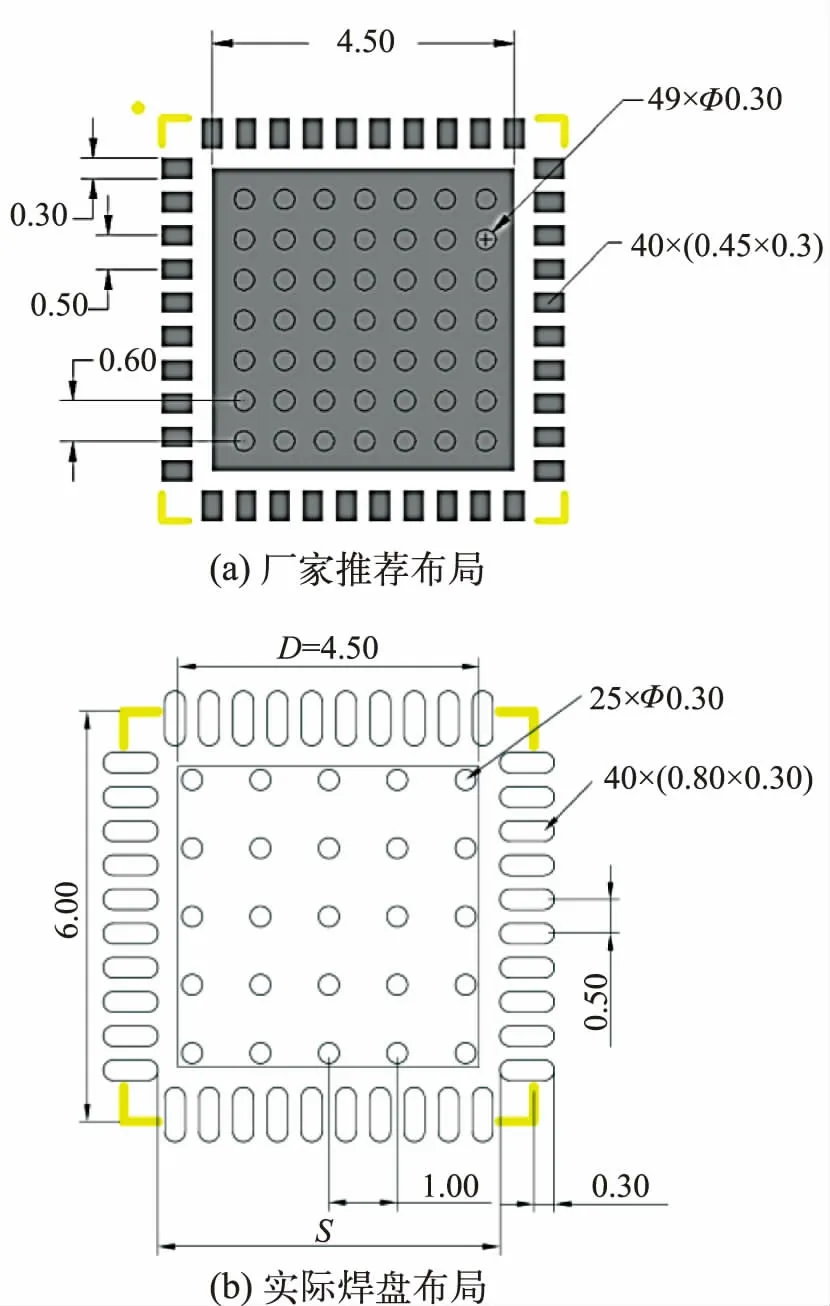

该芯片采用CQFN40 封装,端子间距0.50 mm,焊端焊盘宽(0.30±0.10)mm,长0.45 mm,侧面金属化高度(0.60±0.10)mm,芯片总高1.50 mm。芯片在印制电路板组件表面阵列式排列,并与印制板组件其他待安装元器件有合理的间距。

图2(a)为厂家推荐的PCB 焊盘布局。经验表明,该焊盘设计会导致焊点存在偏离出焊盘、润湿不良的缺陷,因此实际布局调整为图2(b)。其中印制板散热焊盘导通孔间距由0.60 mm 提升至1.00 mm,通过仿真满足器件散热要求。散热导通孔为半通孔,防止焊料通过导通孔溢出导致焊接不良。四周焊端焊盘向外延伸0.30 mm,根部向内延伸0.05 mm,端部外露焊盘可检验焊料润湿及根部焊料填充。焊盘由方形焊盘改为腰形焊盘,预防锡珠溅出。另外,根据器件封装外形,通过均方根方法计算焊盘尺寸,应满足趾部焊盘间距S≥4.93 mm,散热焊盘尺寸D≤4.63 mm[2],实际焊盘设计满足该要求,焊盘设计合理。

图2 PCB 焊盘(单位:mm)

2.2 钢网开孔

QFN 是一种底部端子元器件,在组装的过程中,焊点是否可靠主要由焊点的形状、高度、面积等控制。QFN 器件焊接时如果焊端焊料过多容易使器件漂浮,焊料过少可能导致虚焊,因此需要严格平衡底部大面积焊盘与焊端的影响,保证焊接效果。

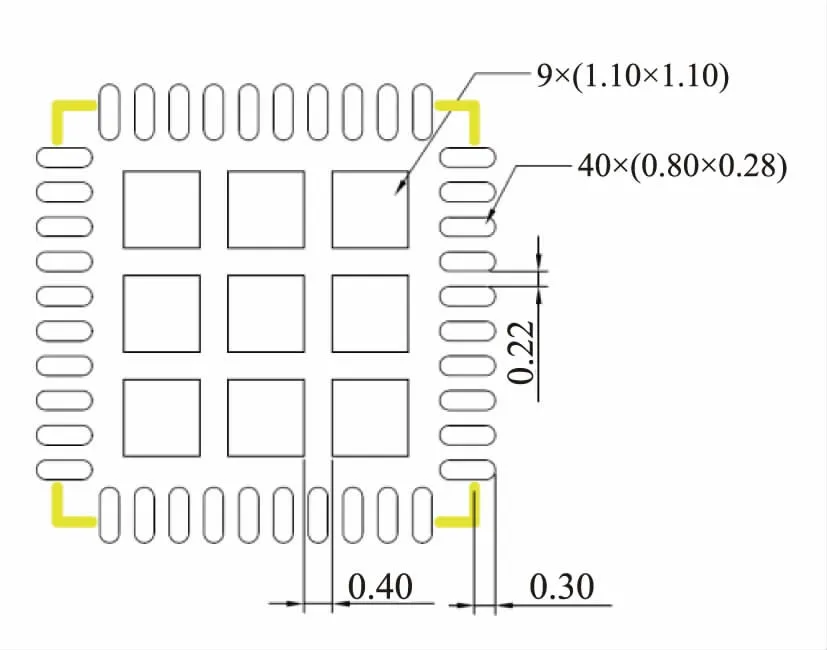

该印制板采用厚0.15 mm 的钢网印刷,开孔图形如图3 所示。QFN 芯片大面积焊盘开孔率54%,四周焊端开孔宽0.28 mm,长0.80 mm。查阅相关厂家数据,对于该封装QFN 芯片,推荐钢网大面积焊盘开孔率40%~60%,芯片四周焊端开孔宽取0.22~0.24mm[1]。

图3 钢网开孔布局(单位:mm)

QFN 大面积焊盘空洞形成主要有两类机理:(1)少锡引起的空洞;(2)排气不畅引起的空洞。少锡引起的空洞主要因为PCB 设计或制作原因,芯片大面积焊盘不能自由塌落,表现为底部非圆滑过渡的空洞。排气不畅形成的空洞主要由于:①回流焊接初期,焊膏熔融、联连,将空气和焊膏中的挥发气体包裹在锡内部,形成空洞;②四周焊端焊膏中助焊剂溢出包裹在焊料外围,芯片底部焊膏中的挥发性气体逸出通道不畅,引发空洞[3]。

另外,由于芯片引线框架制造公差、PCB 制版位置公差、钢网开孔累积公差等因素,该钢网四周焊端开孔过宽,印刷后四周焊盘焊膏偏移,导致锡珠溅出。钢网开孔需优化。

2.3 焊接温度曲线

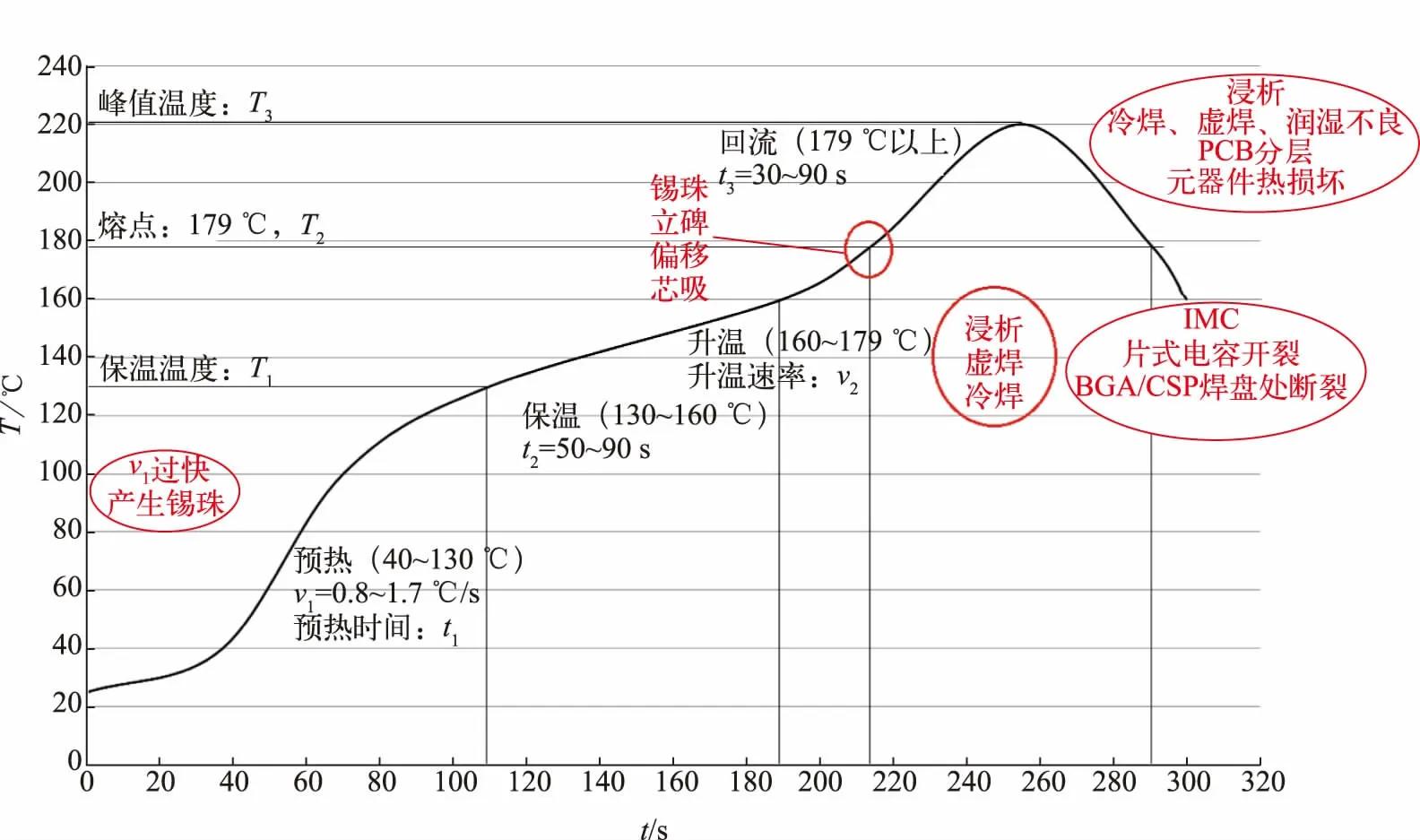

焊膏为Alpha LR721H3 型免清洗焊膏,合金成分为Sn62Pb36Ag2,金属含量90%,推荐焊接曲线见图4。图4显示了典型回流焊接缺陷发生点,锡珠缺陷主要发生在焊接起始预热阶段、锡膏融化前的升温阶段。这主要是因为升温速率过高,焊膏中焊剂的挥发速度快,容易引发焊料飞溅形成锡球。实测v1为0.9~1.3 ℃/s,v2为0.8~1.0 ℃/s[4],保温时间t2为60~65 s,回流时间t3为73~88 s,印制板峰值温度温差为7 ℃。

图4 推荐温度曲线及缺陷发生时间点

对于PCB 整板元器件焊接,必须减少PCB 和元件热变形的问题,因此回流焊接时温度曲线应尽量使整板和元器件接近热平衡条件,保证足够的时间缓慢加热和冷却。由于该印制板为微波-数字混合印制板,存在由于印制板温度不均匀引起的变形导致产生大面积焊盘空洞的可能性。

HANCE 发现锡珠产生率会随焊膏金属含量的递增迅速下降。焊膏中金属含量增加可以减少锡珠产生,金属含量对锡珠率的影响见图5[5],当焊膏中金属成分提升至91%时,锡珠率降低至0。

图5 金属含量对锡珠率的影响

高金属含量的焊锡膏在印刷、贴片后不易坍落,当焊盘以外区域被挤出多余的锡膏时,熔融的焊锡通过表面张力将其拉回[6]。另外,金属含量的增加可以使焊球排列紧密,在融化后更容易结合。因而,焊膏中金属成分的增加可以减少锡珠缺陷,有利于焊接。

3 工艺优化

QFN 底部空洞形成的主要原因有:(1)大面积焊盘少锡,芯片周边焊端形成焊点高度大于芯片中心大面积焊点高度,芯片不能自由塌落形成空洞;(2)相邻焊端焊盘间距小,助焊剂形成薄膜附着在焊点外部,焊膏中的气体没有逸出通道,导致气体在焊点滞留形成空洞。锡珠形成的主要原因有:(1)焊膏印刷后塌落,引发锡珠;(2)回流温升速率过快,焊剂飞溅产生锡珠;(3)相邻焊端焊盘间距小,大面积焊盘产生气体在逃逸过程中对引脚间焊料产生作用力,导致焊料飞溅形成锡珠。因此,需要对钢网开孔、温度曲线进行优化。

3.1 钢网开孔

对高可靠性要求的星载产品,连接QFN 四周焊端的焊点厚度经再流焊后应在0.050~0.075 mm[1],焊点不饱满可能导致机械强度差。故对QFN 四周焊端开孔进行优化,采用厂家推荐尺寸0.24 mm×1.00 mm。

大面积焊盘焊料覆盖对间隙高度有最大的影响,所以有必要改变焊料量以形成最佳填充。研究表明,QFN 底部大面积焊接空洞产生的主要原因有:(1)少锡引起的空洞;(2)排气不畅引起的空洞。根据钢网厂家推荐,大面积焊盘采用“井”字型开窗,开窗间架桥宽度应不小于0.20 mm,使底部锡膏有使气体排出的通道,这是由于当钢网开窗架桥过小时,在回流焊接初期,焊膏熔融、联连,将空气和焊膏中的挥发气体包裹在锡内部;大面积焊盘应内缩,并减小宽度,防止与周边焊端连锡,保障焊膏中气体溢出通畅。分别对4 种大面积焊盘开窗方式焊接QFN 芯片进行实验,钢网开孔率列于表1。

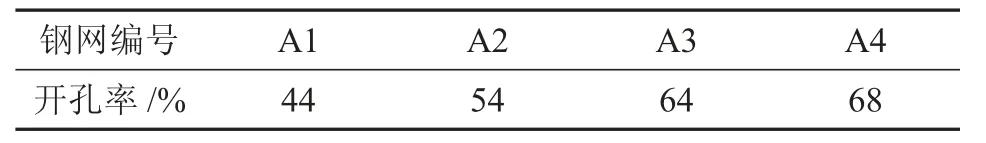

表1 钢网开孔率

实现结果表明,随着钢网开孔率的增加,芯片底部大面积空洞尺寸减小,且空洞发生率大幅降低。图6显示了不同钢网大面积焊盘典型焊接结果。

图6 不同钢网开孔芯片大面积焊盘典型焊接结果

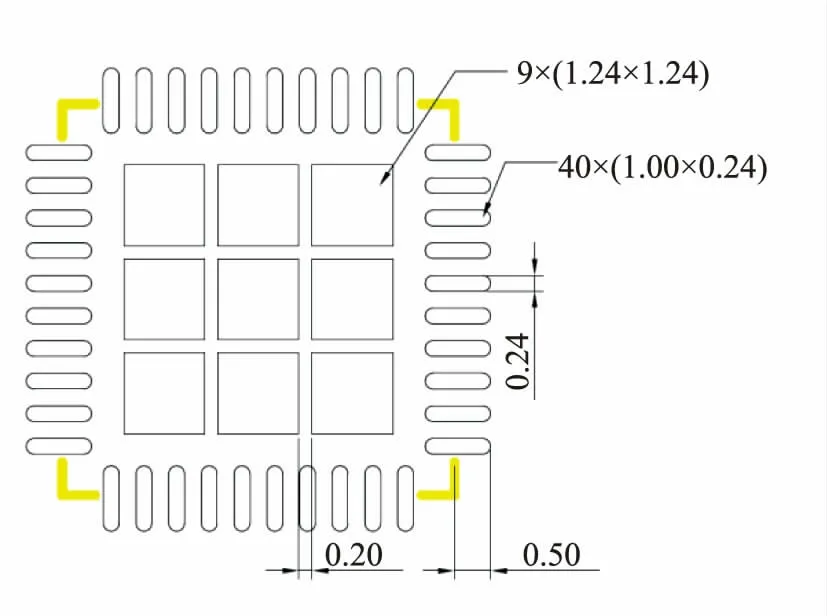

经优化后A4 钢网开孔布局如图7 所示,大面积焊盘开孔单边内缩0.19 mm,钢网架桥宽度0.2 mm,开孔率提升至68%。焊端开孔宽度减小至0.24 mm,有效避免了由于印制板、钢网加工精度原因导致的印刷图形偏移。

图7 A4 钢网开孔布局图(单位:mm)

3.2 温度曲线

参照J-STD-004B 标准,通过选型对比,更换采用等级ROL0 的Alpha OL107E 锡膏进行焊接,其合金成分为Sn63Pb37,金属含量90%。

通过降低回流炉链条传输速度、增加保温时间优化推荐焊接曲线,使印制板达到整板热平衡,单板实测温差4 ℃。

3.3 实施效果

对改善后的印制电路板焊接效果进行检查,QFN底部大面积焊盘空洞得到有效控制,空洞率显著降低。采用40 倍体视显微镜检查焊点,焊点侧面焊料填充、润湿良好,锡珠得到有效控制。通过工艺优化,该产品第二批次焊接的32 个通道中,QFN 元器件焊后一致性良好,单个空洞的最大尺寸均小于焊盘面积的5%,焊接一次合格率为100%。

4 结论

在高可靠性要求的航天产品焊接过程中,器件返修次数有限,且返修会造成器件性能下降、组件可靠性降低等问题,优化焊盘设计、钢网开窗及焊接温度对特殊应用下的QFN 器件的高可靠焊接有重要意义。

QFN 底部空洞产生原因主要有少锡引起的空洞和排气不畅引起的空洞。对于少锡引起的空洞,需要增加钢网漏印焊锡量以形成良好焊接;对于排气不畅引起的空洞,应保证回流过程中焊膏内气体有通畅的溢出通道。器件焊盘及钢网应进行针对性的优化设计,实际装配过程保证焊膏印刷质量,并保持印制电路板在预热、保温、回流、冷却过程中具有良好的温度一致性,避免引起其他缺陷,以保证焊点满足高可靠性要求。