高可靠性的读写分离14T 存储单元设计*

2022-02-17张景波朱亚男彭春雨

张景波,朱亚男,彭春雨,赵 强

(1.工业和信息化部产业发展促进中心,北京 100084;2.安徽大学集成电路学院,合肥 230601)

1 引言

半导体器件,如静态随机存储器(SRAM),对大气中存在的高能粒子[1-2]很敏感。当高能粒子撞击微电子电路的敏感区域时,就会引起微电子学中的单粒子翻转(Single Event Upset,SEU)。因此,降低SEU[3-5]发生的概率是提高SRAM 抗辐照性能的关键。SRAM 作为存储模块的基本单元,广泛用于高速低功耗[6]的存储芯片中,其在空间环境中的稳定性成为影响电子系统可靠性的主要因素。近年来,抗辐射存储单元设计被认为是提高电路抗辐射能力的一种有效方法。但是,通过改变电路结构来降低SRAM 单元的软错误率会增加额外的电路成本[7-9]。因此,有必要提出一种高性能、高可靠性的SRAM 单元。近年来,研究人员对CMOS 工艺下的存储单元电路展开加固设计研究,并提出了多种抗SEU 存储电路加固设计结构[10-13]。一些具有显著辐射耐受能力的SRAM 单元被报道,如文献[5]中提出的双联锁存储单元(DICE),它由12 个晶体管组成,其中Q、QB 与S0、S1 利用2 个联锁节点来存储1 组互补数据。当存储单元的任意节点被重离子撞击时,存储单元利用正反馈恢复到初始状态。另一种典型的存储单元是QUATRO[14]。虽然它能够利用4 个节点来恢复2 个互补的数据对,但是它不能实现恢复所有单个节点的翻转。文献[7,9]都提出了10T 存储单元,其中文献[9]使用了晶体管的极化、电容效应等方法来防止存储单元的任意单节点翻转。

本文提出了一种新型的读写分离RWS 14T 存储单元,该单元通过选择更多的NMOS 晶体管与合理的晶体管尺寸,能够提供良好的抗辐射能力,并且读写分离技术的应用使其具有良好的读写性能。

2 RWS 14T 单元设计

2.1 RWS 14T 单元的结构

RWS 14T 存储单元结构如图1 所示。该单元包括4 个PMOS 晶体管和10 个NMOS 晶体管。其中上拉晶体管(N1、N2、P1、P2、P3、P4)、下拉电晶体管(N3、N4)和下拉晶体管(N5、N6)的宽长比(W/L)分别为80 nm/65 nm、210 nm/65 nm 和280 nm/65 nm。另外还有4 个额外的NMOS 晶体管N7~N10 为传输管,它的宽长比(W/L)为140 nm/65 nm。其中N7~N8 栅极接公共写字线(WL),N9 栅极接读字线(RWL),N10 栅极接存储节点QB。

图1 RWS 14T 存储单元

2.2 工作原理

该RWS 14T 存储单元采用读写分离结构,分别由WL 和RWL 控制单元的读和写操作。相比于传统SRAM 读写结构,读写分离结构不仅提高了单元的读写速度,减少读写延迟时间,并且避免了单元的“读破坏”问题,使得该存储单元的工作性能得到了提升。

假设RWS 14T 存储单元存储电压为低电平,即Q=“0”,QB=“1”,S1=“0”,S0=“1”,RWS 14T 存储单元的仿真波形如图2 所示。下面详细分析RWS 14T 单元的工作原理。

图2 RWS 14T 存储单元时序

保持状态:位线BL、BLB 均为高电平,WL、RWL均为低电平,单元内部存储节点通过传输管与位线隔离,存储数据保持不变。

写操作:写“1”操作,位线BL 为高电平,位线BLB置为低电平。当WL 为高电平、RWL 置为低电平时,执行写操作。晶体管N1、N3、N6 打开,P1 关闭,此时S1节点数据存储为“1”,说明数据“1”被成功写入。

写“0”操作,位线BL 为低电平,BLB 为高电平,字线WL 为高电平,RWL 为低电平时,执行写操作。此时存储节点Q 点的电压为“1”,存储节点QB 点的电压为“0”,晶体管N1、N4、N5 导通,P2 关闭,此时S1 节点数据存储为“0”,从而完成写“0”操作。

读操作:读“1”操作,经过预充电阶段后,两条位线的电压均升至高电平。当WL 为低电平、RWL 置为高电平时,NMOS 晶体管N9 导通进行读操作。当QB=“0”,则晶体管N10 截止,BL 不能对地放电保持高电位,与位线BLB 形成电压差。通过外围电路灵敏放大器进行识别,可读出存储节点Q 为“1”。

读“0”操作,经过预充电阶段后,两条位线的电压均升至高“1”。当WL 为低电平、RWL 为高电平时,打开NMOS 晶体管N9 进行读操作。当QB=“1”,晶体管N10 导通,BL 的电压由于N9 和N10 的放电而降低,与位线BLB 存在电压差。通过外围电路灵敏放大器进行识别,可读出存储节点Q 为“0”。

2.3 性能的仿真分析

对该单元与其他对比电路的读写速度、写裕度、功耗、噪声容限以及临界电荷等方面进行测试。为了公平比较,所有电路都是在65 nm 工艺下进行测试,且使各个对比电路的上拉管和下拉管与传输管的比率保持一致。

读写速度是SRAM 性能的主要指标,对所提出的RWS 14T 存储单元的运行速度进行了仿真和评估,仿真结果如图3 所示。读取访问时间定义为字线电压达到50%VDD时刻到BL 电压下降50 mV 时刻之间的时间间隔;写访问时间定义为字线电压达到50%VDD时刻到存储节点翻转时刻之间的时间间隔。

图3 读写时间

RWS 14T 单元的读写访问时间和静态功耗与其他存储单元的比较如表1 所示。RWS 14T 单元写速度具有一定的优势,读速度略大,但可通过增大晶体管N9、N10 的尺寸提高读速度。静态功耗略高于其他存储单元。

表1 不同存储单元读写时间和静态功耗的对比

在SRAM 单元的电路级性能中,读写操作稳定性是其中一项关键指标和衡量因子,通常用读/写静态噪声容限或者读/写裕度大小来判别衡量。裕度反映的是读写操作时读写数据的容易程度,以写裕度(WM)为例,它是指使得存储数据发生翻转的最小字线/位线电压[15-16],WM 的值越大则表明其写操作能力越强,反之,则越弱。

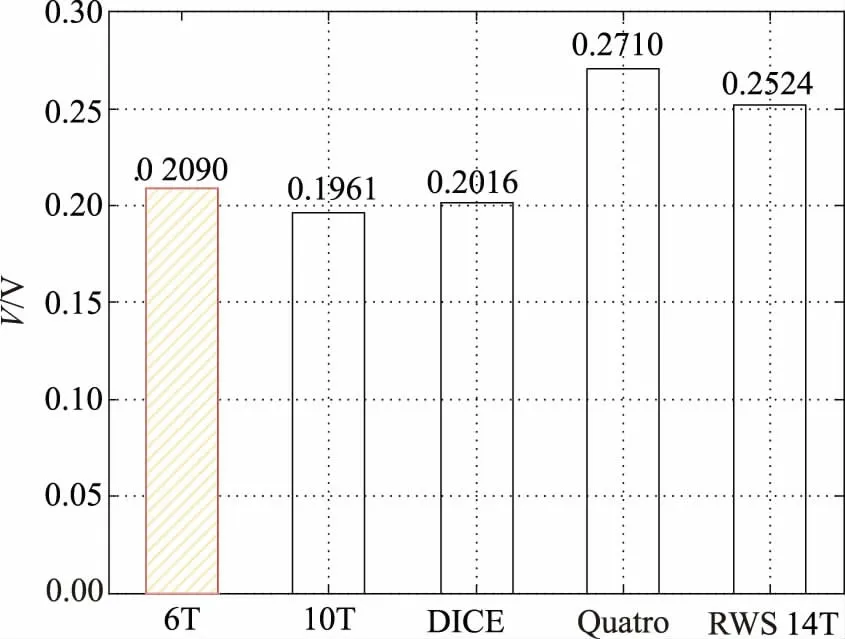

静态噪声容限(Static Noise Margin,SNM)作为衡量存储单元稳定性的重要指标,被设计人员广泛采用[17]。读静态噪声容限(RSNM)被定义为存储单元在不发生翻转的情况下所能容忍的最大直流噪声值。电源电压1.2 V 时RWS 14T 的RSNM 的仿真结果如图4 所示。1.2 V 供电电压下RWS 14T 存储单元的RSNM 明显优于6T 单元、10T 单元和DICE 单元,仅次于Quatro 单元,仿真结果如图5 所示。

图4 1.2 V 电压下RWS 14T 单元的RSNM

图5 不同存储单元读噪声容限

在本设计的仿真分析中,写操作稳定性是通过写裕度来衡量的。位线写裕度是BL 电压从VDD下降到一定值后,存储单元存储数据发生翻转,则此时的电压值就表示写操作是BL 电压允许的最高电压值。字线写裕度是WL 电压从0 上升到一定值后,存储单元存储数据发生翻转,则此时的电压值就表示写操作WL 电压的最低电压值。在TT 工艺角、温度为25 ℃、供给电压为1.2 V 的条件下,所提出的14T 单元的写裕度示意图对比结果如表2 所示。RWS 14T 存储单元的位线写裕度明显优于6T 单元、Quatro 单元、DICE单元。字线写裕度略差于6T 单元、10T 单元、DICE 单元,但优于Quatro 单元。

表2 不同存储单元写裕度的对比

综上所述,通过对存储单元的读噪声容限、写裕度、读写速度、功耗的仿真分析,提出的14T 单元不但能够正确地实现读写功能,并且具有一定的优势。仿真结果表明14T 存储单元在高速应用上与其他辐射存储单元相比是有竞争力的。

临界电荷Qcrit(Critical Charge)是衡量SRAM 单元抗辐射性能的重要指标。它被定义为节点发生翻转时所收集到的最少电荷量[18]。通过对所提出的RWS 14T单元与其他对比电路的临界电荷测试,从表3 中可以清楚地看出,RWS 14T 单元的临界电荷仅仅低于DICE 单元,而相比于其他抗辐射单元,RWS 14T 单元有着较大的优势。

表3 存储单元临界电荷的对比

3 RWS 14T 抗辐射研究方法

3.1 SEU 恢复分析

提出的RWS 14T 单元敏感节点是节点Q、QB、S0和S1,具体取决于存储值。假设存储单元为“0”(Q=“0”,QB=“1”,S1=“0”,S0=“1”)。详细说明了提出RWS 14T 对抗SEU 的行为,分析结果如下。

(1)当节点Q 受到粒子轰击,节点Q 数据发生从0 到1 的翻转,晶体管P3 暂时关闭,晶体管N1 暂时打开。由于上拉晶体管N5 的尺寸大于驱动晶体管N1,节点S1 和S0 数据恢复初始状态。

(2)当节点QB 受到粒子轰击,节点QB 存储数据将从1 翻转到0,晶体管P4 暂开,晶体管N2 暂时关闭,节点Q 的电压保持“0”状态。节点S1 保持其初始状态,N6 也将保持关闭状态,节点S0 也将保持初始状态“1”。最后,将节点QB 恢复到“1”状态。

(3) 当节点S0 和S1 受粒子轰击,重离子撞击NMOS 晶体管的敏感区域时,只产生负电压脉冲[4,19],即S0 受“1→0”暂态脉冲影响,S1 受“0→0”暂态脉冲影响,由于容量效应,这两个电压脉冲不影响其他存储节点,所以S0 和S1 在RWS-14T 单元中不是敏感节点。

(4)最后,讨论了多节点干扰问题。当节点同时受到S0-Q 干扰时,存储在节点上的数据将发生变化。由于晶体管N4、N5 均停止,并且N1 将导通,因此节点Q 无法恢复其初始状态。这种电荷共享效应引起的问题可以通过布局优化技术来缓解[20]。文献[21-22]中提出的RHMP 和RHMN 存储单元结构就是在节点冗余加固技术的基础上利用了极性加固技术和版图加固技术。本文仅考虑辐射粒子对节点Q-QB 的影响。

图6 是通过Cadence Spectre 中的SEU 故障注入仿真验证结果。在故障注入中,采用双指数电流源模型来近似设备[3,22-23]的重离子撞击效应。如图6(a)(b)(c)所示,故障脉冲被注入到存储节点,以模拟重离子撞击效应。单个瞬态脉冲分别注入节点Q、QB、S1,时间分别为6.5 ns、11.5 ns、6.5 ns。可以看出,节点Q、QB、S1 可以恢复到初始状态。为了验证Q-QB 节点对的稳健性,在图6(d)中分别在6.5 ns 和11.5 ns 处同时向Q 和QB 节点注入故障脉冲。这种模拟电荷共享的同步注入方法已被广泛应用[4,9]。仿真结果表明,所提出的14T 单元可以防止任何单节点扰动和内部节点对的扰动。

图6 SEU 故障注入仿真验证

对于纳米级半导体电路,晶体管属性(如长度、宽度、氧化层厚度)中工艺参数的变化会导致设计性能的下降。这些变化也会影响抗辐射电路的SEU 免疫力。图6(c)中显示S1 电压损耗,但是受到粒子撞击后仍能够恢复初始状态。分析电路可知,S0、S1 电压达不到1.2 V,这是由于上拉管NMOS 的阈值损耗造成的。

3.2 TCAD 仿真

除了采用脉冲电流注入方式,使用TCAD 软件设置基本参数、模拟各种空间辐射环境的方式被研究抗辐射性能的研究人员认可。SEU 故障注入仿真验证如图7 所示,建立包含RWS 14T 单元电路中敏感节点对应的晶体管的TCAD 模型,其他非敏感节点对应的晶体管可以调用SPICE 模型库中的模拟器件代替,建立模型,并在相应的仿真平台进行模拟。

图7 SEU 故障注入仿真验证

为了能够更好地描述粒子的入射角以及入射粒子能量,引入了参数θ、β 和线性能量传递(LET)。θ 表示粒子入射方向与y 轴的正方向之间的夹角,β 表示入射粒子轨迹投影在xz 平面上的投影向量与x 轴正方向之间的角度。

当入射粒子的能量LET 为30 MeV·cm2/mg,以θ=60°,β=0°轰击时,不同关键节点在高能粒子的轰击下存储节点的数据能够恢复。以轰击NMOS2、NMOS5的漏端为例,轰击RWS 14T 单元关键节点验证如图8所示,存储数据不会发生变化,其他存储节点数据也不变。当入射粒子的能量LET 为25 MeV·cm2/mg,以不同的入射粒子角度轰击存储单元关键节点时,存储数据不发生改变,证实RWS 14T 单元具有较好的抗SEU 能力。

图8 轰击RWS 14T 单元关键节点验证

4 总结

本文提出了一种具有高可靠性的抗辐射存储单元RWS 14T,以对存储器提供完善的SEU 保护。所提出的设计不仅可以为单个节点上的感应瞬态脉冲提供完全的免疫力,而且不考虑极性和强度的影响,还可以容忍2 个固定节点上的双节点故障。与各种辐射存储单元相比,该RWS 14T 存储单元应用读写分离技术,而且该存储单元的位线写裕度明显优于其他存储单元,字线写裕度也比QUATRO 提高了约28.4%。为了获得更好的读时间,可以通过修改晶体管N9、N10的尺寸,或者设计人员再进一步改善。综上分析,提出的RWS-14T 单元在具有良好抗SEU 能力的同时,具有良好的读写速度。