一种消除共模反馈电流辅助放大的高增益运放

2022-01-12孙正龙商世广

刘 伟,孙正龙,黄 东,商世广

(西安邮电大学 电子工程学院,陕西 西安 710121)

放大器是一种能将输入信号的电压或功率进行放大的装置。它是模拟电路中最重要的组成部分,其性能的优劣将对整个系统产生直接的影响。然而高性能的高增益运算放大器在模拟电路的需求中具有较大的缺口[1-2]。在当前的技术中,已经有很多方法来解决这个问题,如俄勒冈州立大学的Yang 等[3]将多个放大器进行级联来提高整个运放的增益,然而使用更多数量的放大器级联会增加功耗,还会带来稳定性问题。针对功耗与稳定性的问题,荷兰飞利浦研究实验室的Bult 等[4]提出了一种名为增益增强的电路结构,其能够在保持其他性能的前提下有效地提高运算放大器的整体开环增益,使其成为高增益运算放大器的另一种实现方式。在后续的研究中为了针对复杂的实际情况,北方工业大学的朱江南等[5]对此结构进行了优化,但使用的全差分共源共栅结构会由于器件存在的不匹配对其共模电压产生显著的影响,故引入了额外的共模反馈电路,最终增加了整体电路的面积与功耗。随后墨西哥Spherix 公司Far[6]针对不同的情况进行了改进,但电路的整体结构过于复杂,面积过大,未能实现电路参数的良好折中。长沙理工大学的唐俊龙等[7]使用的电路结构虽然具有较高的增益,但电源抑制比性能较差,未能实现电路性能的最优化。中国电子科技集团第54 研究所的田海燕等[8]使用的结构虽具有较大的增益带宽,但辅助运放的结构过于复杂,不利于电路的实现。

针对上述增益、功耗与电源抑制比等问题,本文提出了一种高增益轨对轨输出的运算放大器。该放大器由一个折叠式共源共栅放大器与两个电流辅助放大器构成,其中三个放大器都采用了差分输入单端输出的电路结构,消除了共模反馈电路。在主运放上添加的两个辅助放大器为电流放大器,简化了电路结构,降低了整体电路的功耗。电路开环增益达到了167.5 dB,且同时具有良好的共模抑制比与电源抑制比。在运算放大器的输出级采用改进型的AB 类放大器结构,提高了放大器的输出摆幅,基本实现了轨对轨的电压输出。

1 增益增强轨对轨输出运放设计

1.1 增益增强技术的基本原理

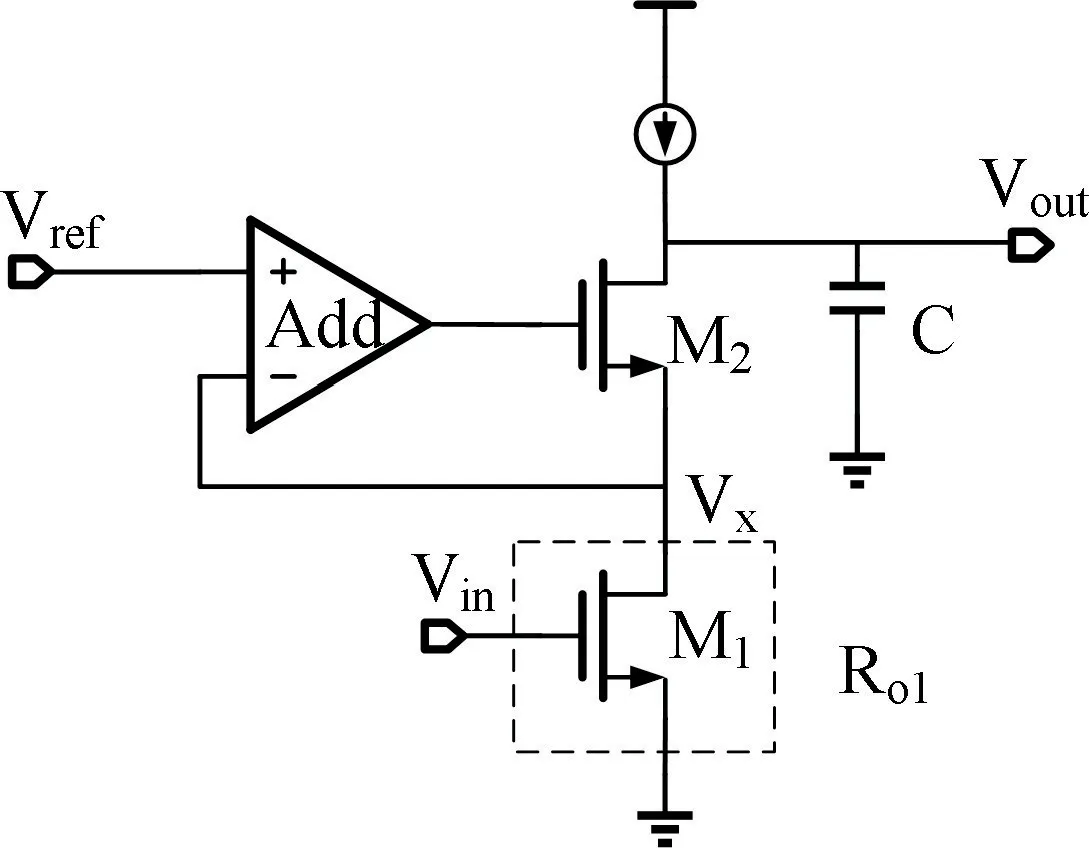

增益增强最直接的方法是提高运算放大器输出级电路的输出阻抗[9]。增益增强结构原理如图1 所示。

图1 增益增强技术结构图Fig.1 Structure diagram of gain enhancement technology

图1 中辅助放大器Add 的增益为A。当没有辅助放大器的时候,为了计算Rout,电路可以看成带负反馈电阻Ro1的共源级,因此可以得到[10]:

故得共源共栅放大器的增益为:

加入辅助放大器后,输出电阻变为:

则增益变为[11-12]:

通过式(4)可知,在利用增益增强技术后,其增益比原来增大了(1+A)倍。其中加入辅助放大器不会影响整体的输出摆幅与等效输入噪声,因此可以广泛地运用于高增益运放中[13]。

1.2 增益增强技术的电路实现

为了得到高增益而不影响运放的相位特性、压摆率和信号带宽等性能,本设计在折叠式共源共栅运放中加入辅助运放来提高整个电路的增益。与传统的折叠式结构相比,本文提出的放大器仅以电压裕度为代价就可以增强输出节点的阻抗。

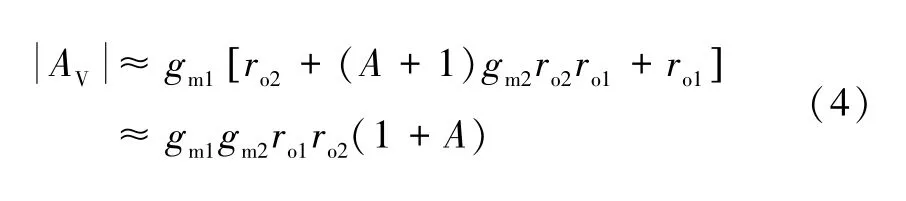

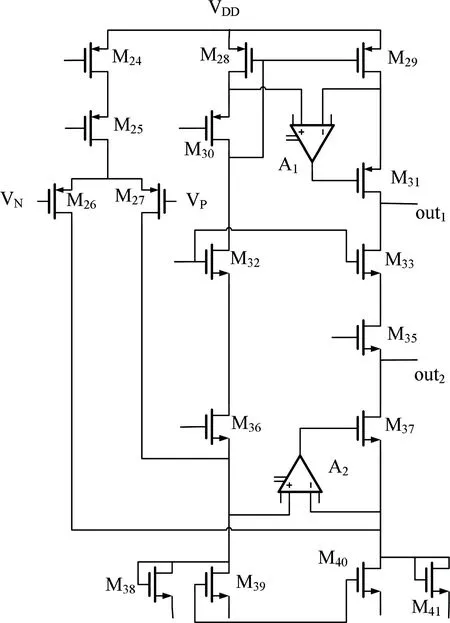

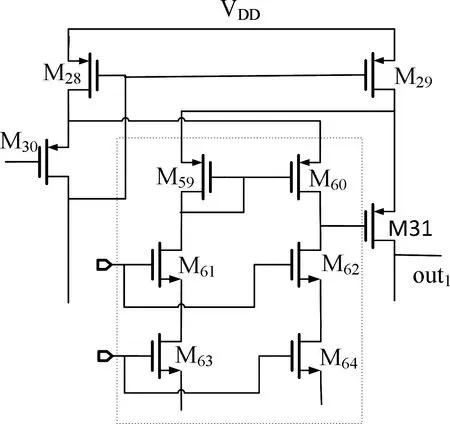

增益增强电路如图2 所示,其采用0.35 μm CMOS 工艺进行设计。图2 中A1、A2为主运放的两个电流辅助运算放大器。辅助放大器具有两个功能:第一,将输出阻抗提高到传统共源共栅结构的(1 +A)倍;第二,由共源共栅器件和辅助放大器形成的负反馈环路提高了电路的输出电阻,并确保M28 和M29,M39 和M40 具有相同的VSD(MOS 管的源漏之间的电压)。此外,由于M28 和M29,M39 和M40 具有相同的尺寸,即M28 和M29,M39 和M40 具有相同的VSG(MOS 管的栅源电压)和VSB(MOS 管的源与衬底之间的电压),从而在宽动态范围内实现了高度线性的输入-输出电流匹配。

图2 输入级及增益提高电路Fig.2 Input stage and gain enhancement circuit

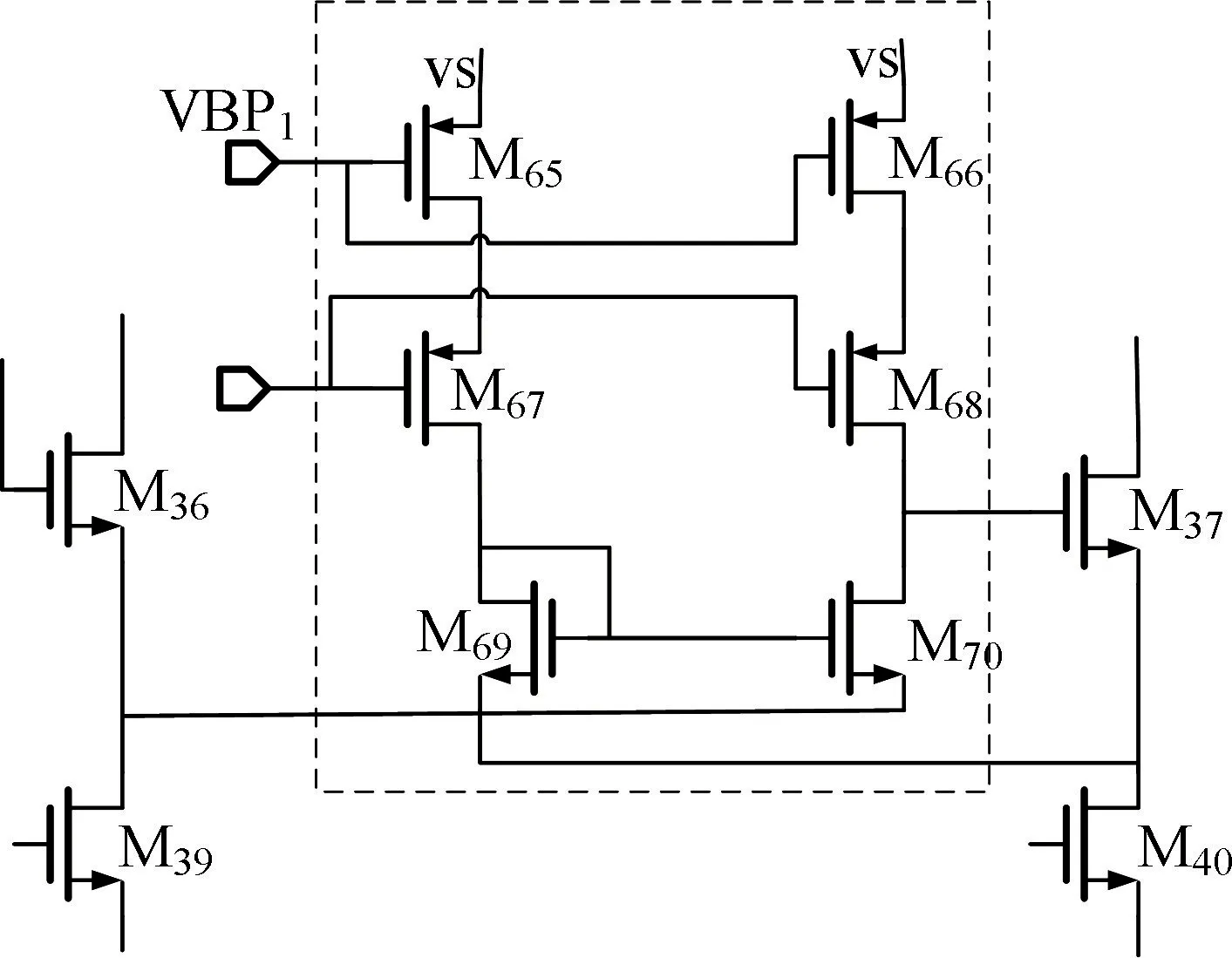

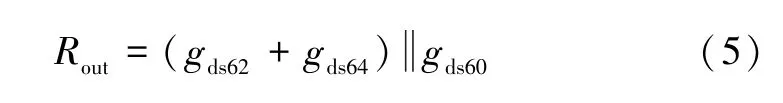

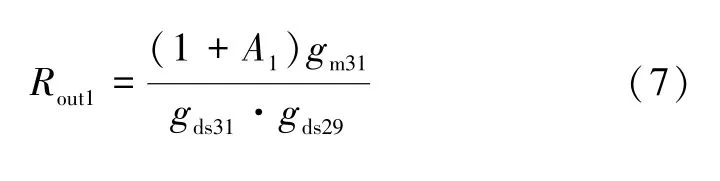

增益增强电路中使用的放大器A1、A2可以通过电压放大器或电流放大器来实现。电流放大器电路及连接关系分别如图3 和图4 辅助放大器连接图所示。其中虚线框内为辅助放大器电路结构。电流放大器A1由饱和状态下的M59~M64 组成,其中M59 匹配M60,M61匹配M62,M63 匹配M64。M61~M64 是电流放大器的有源负载。辅助放大器A1的输出阻抗表示为:

图3 辅助放大器A1连接关系Fig.3 Connection relationship of auxiliary amplifier A1

图4 辅助放大器A2连接关系Fig.4 Connection relationship of auxiliary amplifier A2

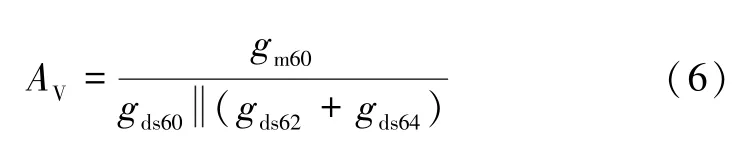

式中:gds为MOS 管的输出电导。辅助放大器的增益为:

因此,上半部分的输出电阻Rout1为:

式中:A1为辅助放大器A1的增益;gm为器件的跨导。同理,增益提高电路的下半部分的输出电阻为:

本文提出的电流放大器具有电路结构简单、功耗低和动态范围大等特点。其次,使用电流放大器可以减小电压放大器引起的寄生效应。这是因为在使用电压放大器时,应有一条与主放大器相连的MOS 管用作输入,此管的Cgb与主放大器相连并影响主放大器的性能。在使用电流放大器时,辅助放大器仅吸收主放大器的一小部分电流,Cgs与主放大器相连,但比同一管中的Cgb小得多。

全差分运放的负载是两个电流源形式的MOS 晶体管,其输出直流电位是随机的,因此需要引入共模负反馈来控制负载电流源的电流,使其输出电位恒定。而单端运放负载是电流镜结构,M28 支路的MOS 管是栅漏相连的二极管形式,可以提供固定的栅极电位,所以不需要共模反馈电路。

1.3 整体运放偏置电路

本文提出的整体运放的偏置电路如图5 所示。在偏置电路中大量使用了电流镜,但在使用中,MOS 管的二级效应严重影响了电流镜复制的准确性[14]。为了提高镜像电流的精度且同时消耗最小的电压余度来提高偏置电路的性能,本文采用低压共源共栅结构,如图中MOS 管M8~M9 与M12~M13,M18 与M19,M22 与M23 所示。

图5 偏置电路Fig.5 Bias circuit

1.4 整体运放输出级电路

本文提出的运放的输出级如图6 所示。其中M51~M52 为互补推挽放大管。R1、R2、C1和C2构成了补偿电路,分别为补偿电阻与补偿电容。M44~M45 为偏置管,M42、M43、M48 和M51 组成了一个跨导线性环。串联在M49 与M47 中间的MOS 管具有很低的双向小信号阻抗,通过确定的电流便形成了浮动电压源。输出电路中的跨导线性环回路,控制着输出管M51 与M52 的静态电流。这就使得输出级的静态工作点得以稳定,不会受到共模输入电压变化的影响[15]。

图6 高增益运放输出级Fig.6 High gain op amp output stage

传统的运放输出级为了严格实现轨对轨的输出,用PMOS 管、NMOS 管以及偏置电路组成两个跨导线性环来控制输出管的工作状态。本文采用单个PMOS 管及偏置电路组成的单跨导线性环,其目的是在基本实现轨对轨输出的基础上简化电路结构,降低输出级功耗。

2 仿真与分析

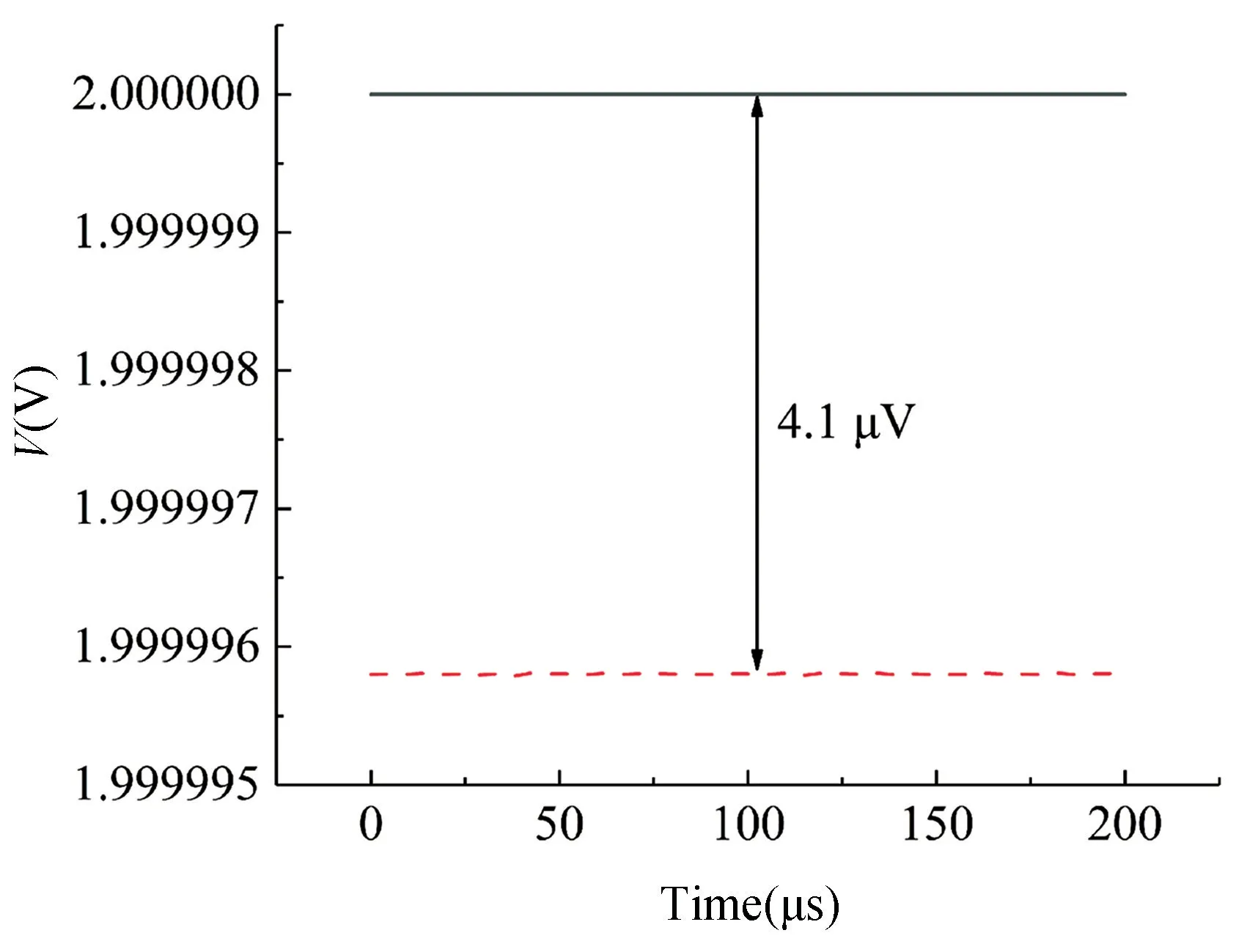

图7 为高增益运放失调电压的仿真结果。将运放接成缓冲器形式,测量输出与输入的差值,其值就为高增益运放的失调电压。图中实线为输出曲线,虚线为输入曲线,由图可知其失调电压值为4.1 μV。

图7 失调电压仿真Fig.7 Simulation of offset voltage

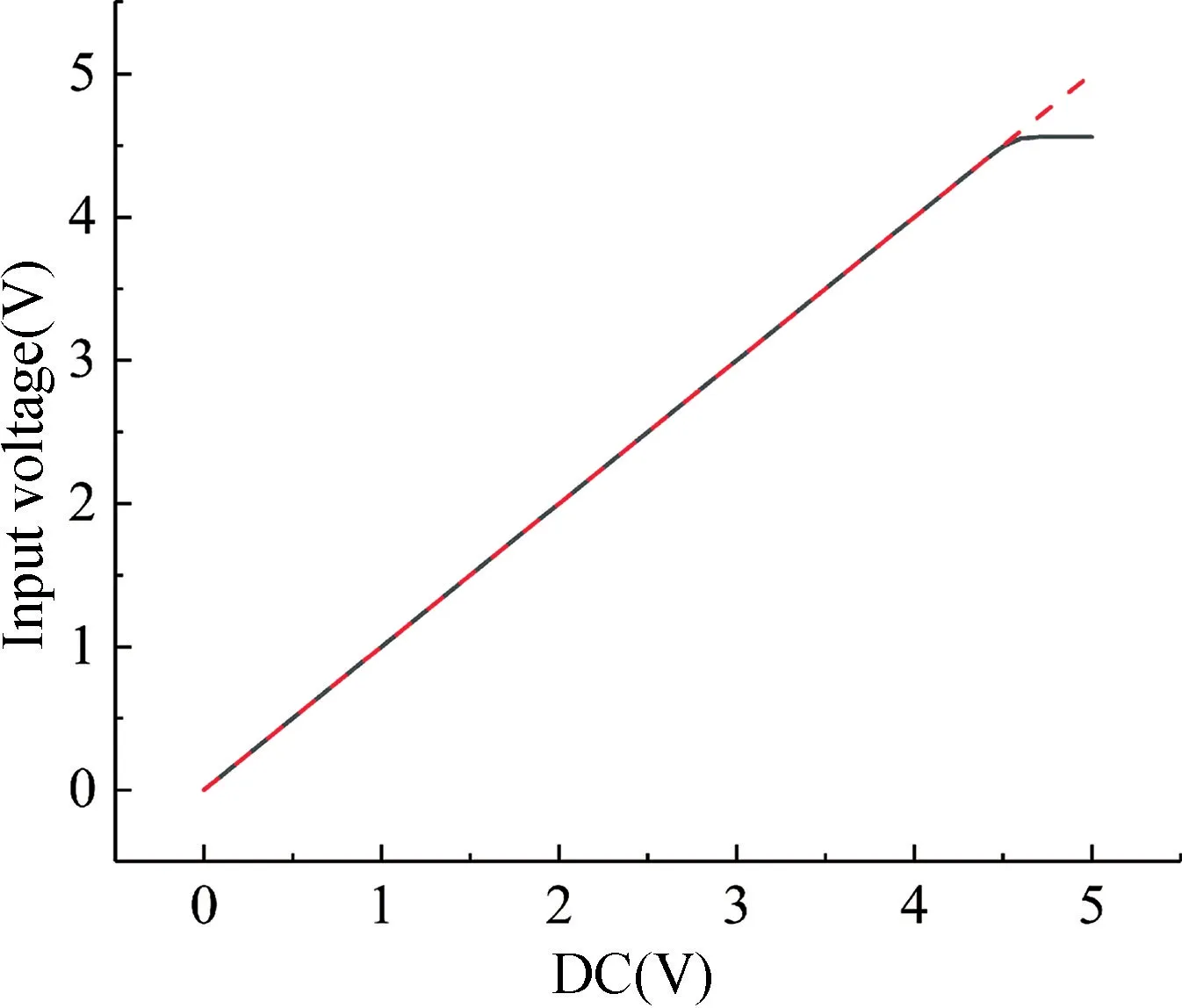

图8 为共模输入范围的仿真结果。将运放接成单位负反馈的形式,对0~5 V 电压进行直流扫描,同时观察放大器输入与输出端的电压变化。在5 V 的电源电压下,直流扫描曲线的斜率为45°,且在0~4.6 V 的电压下,输出能够良好地跟随输入,即共模输入范围为0~4.6 V。

图8 共模输入范围仿真曲线Fig.8 Simulation curve of common mode input range

将运放接成反向比例放大器,同时对输入信号进行直流扫描,观察放大器输出端的电压变化曲线,如图9 所示,曲线倾斜部分即为输出电压范围。由图9可得,输出电压范围为0~4.95 V,基本实现了轨到轨的输出。

图9 输出电压范围仿真曲线Fig.9 Simulation curve of output voltage range

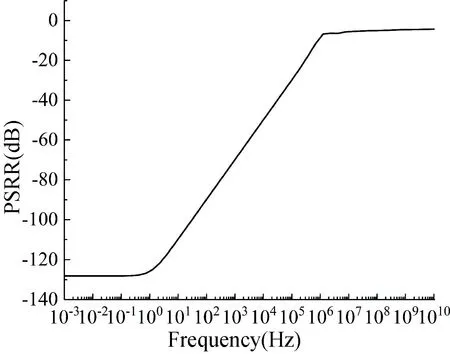

图10 为运算放大器电源抑制比(PSRR)的仿真曲线。可以将运算放大器接成单位负反馈的形式,同时在电源上设置一个单位的交流小信号,最后通过观察运算放大器的输出端的仿真曲线图即可得出电源抑制比。由图可知,电源抑制比为128 dB。

图10 电源抑制比仿真曲线Fig.10 Simulation curve of PSRR

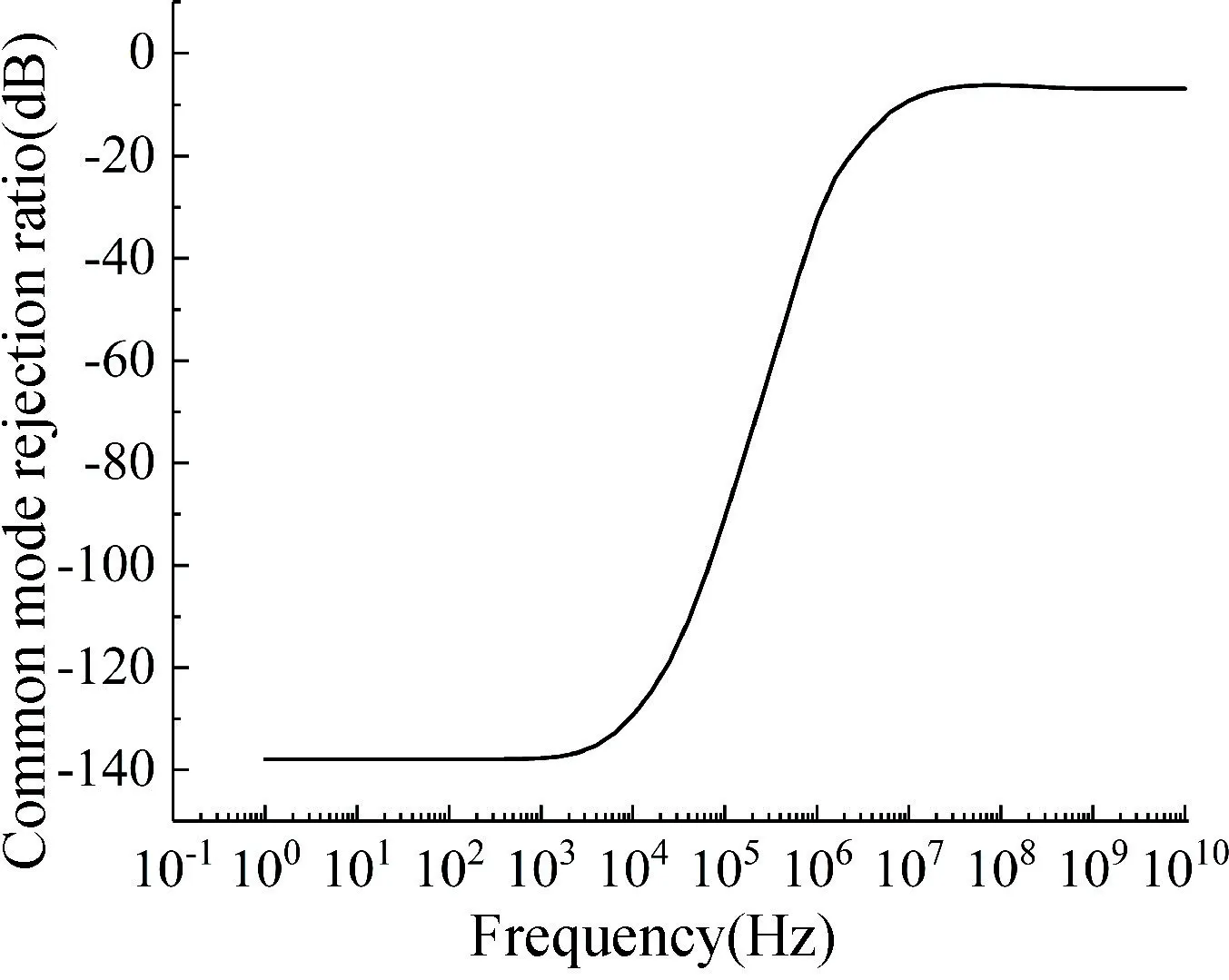

图11 为运算放大器共模抑制比的仿真曲线。将运放接成单位负反馈结构,在正输入端、输出端与负输入端中添加一个单位的交流小信号,对该结构进行AC 频率扫描。由图11 可知运放的共模抑制比为138 dB。

图11 共模抑制比仿真曲线Fig.11 Simulation curve of common mode rejection ratio

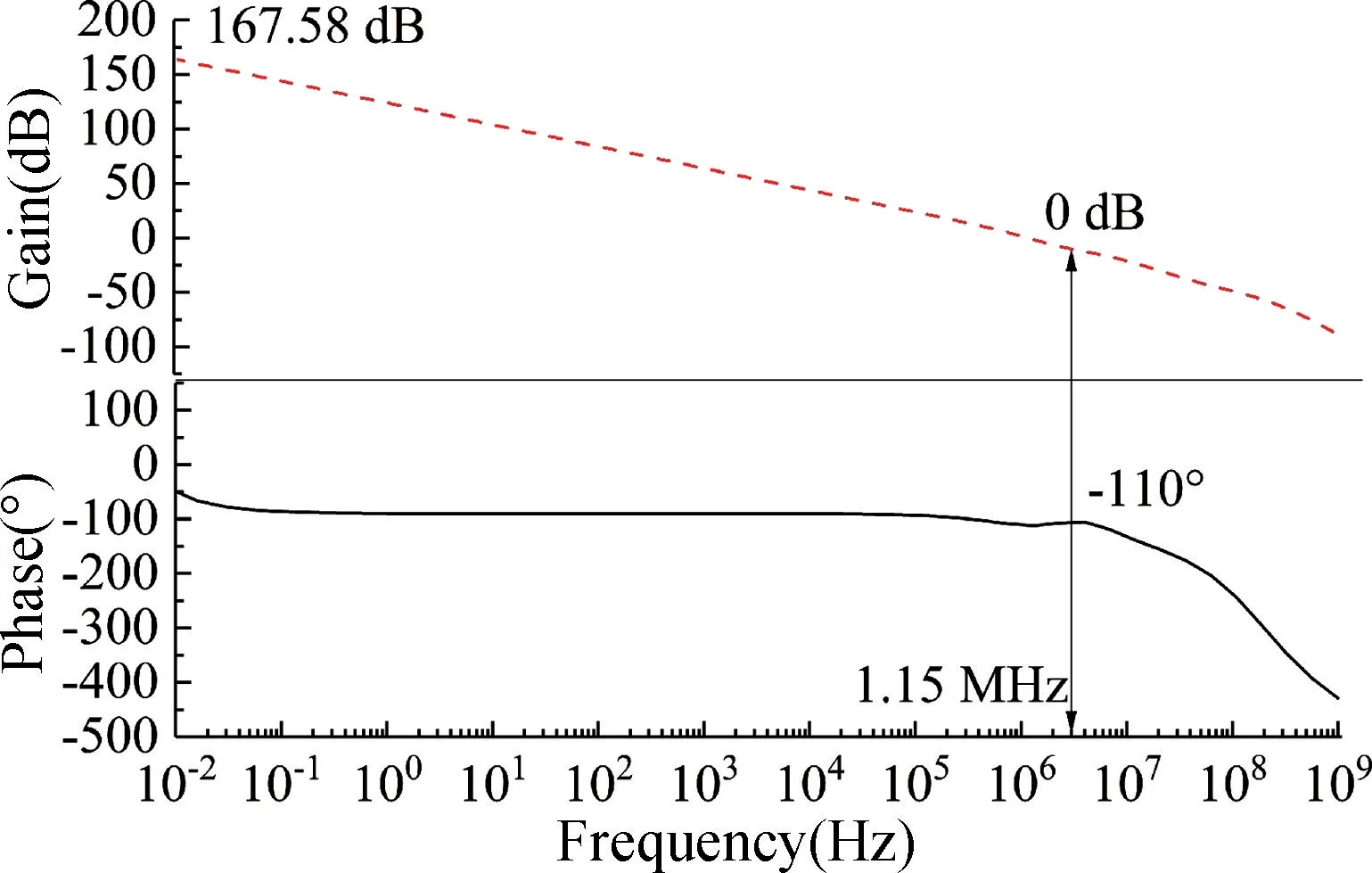

图12 为运算放大器的开环增益与相位裕度的仿真曲线。由图12 可知在低频时运放的开环增益为167.5 dB。当运放开环增益为0 dB 时,相位裕度为70°,单位增益带宽为1.15 MHz[16]。

图12 开环增益与相位裕度仿真曲线Fig.12 Simulation curves of open loop gain and phase margin

表1 为本文所设计的电路结构的仿真数据与国内外所发表文献的对比结果。由表1 可知,文献[6]提出的电路结构虽共模抑制比较高,但相位裕度太低,系统稳定性较差。文献[7]电路结构的电源抑制比较低,对电源波动的抑制能力较差。文献[8]未考虑电源抑制比与共模抑制比。文献[13]提出的电路结构电源抑制比与共模抑制比较低。由比较可得,本文所提出的结构具有较高的电压增益,同时其共模抑制比与电源抑制比较大,其系统稳定性较好。

3 结论

本文运用改进型增益增强技术设计了一款高增益、高电源抑制比、高输出摆幅的运算放大器。提出的改进型增益增强运算放大器整体电路都采用差分输入单端输出结构,解决了传统的增益增强技术引入共模反馈电路的问题,简化了电路结构,减小了整体电路面积与功耗,然而单位增益带宽较小,还拥有较大的优化空间。输出级采用了改进型AB 类放大器的结构,提高了输出电压摆幅和效率,基本实现了轨到轨电压的输出。整体电路采用0.35 μm 工艺实现,通过Candence 软件进行仿真。结果表明,在5 V 电源电压下,开环增益为167.5 dB,相位裕度为70°,失调电压为4.1 μV,共模输入范围为0~4 V,输出电压范围为0~4.95 V。电源抑制比为128 dB,共模抑制比为138dB。