基于FPGA的双路光纤激光拍频信号解调电路设计

2021-12-28莫立涛李宏伟张昕明吕国辉

莫立涛,李宏伟,湛 晖,张昕明,黄 妍,吕国辉,*

(黑龙江大学 a. 光纤传感技术国家地方联合工程研究中心; b. 电子工程学院,哈尔滨 150080)

0 引 言

基于光纤激光的传感技术在信噪比、测量精度、抗干扰能力、远距离传输方面有明显的优势[1],尤其是在分布式和高精度光纤传感测量中,激光拍频探测[2-3]已成为微弱信号放大和高精度信号提取的关键技术。近年来,学者们在激光拍频探测方面主要采用频谱仪进行测量射频信号,这种仪器体积庞大、价格昂贵,难以在实际工程中得到应用。有学者将射频技术中的混频技术应用于拍频信号处理,将GHz的频率信号通过混频降至中频甚至更低,便于高速信号采集和信号处理,可有效降低系统对高速模数转换和数据处理器件的要求,符合实际需求。本文以FPGA技术为核心,通过拍频探测和混频处理之后,应用高速ADC将信号采集到FPGA中进行处理,解调出激光的频差信息,对降低光纤传感系统的成本,促进系统的小型化和集成化奠定基础。

1 双路激光拍频解调

待解调的双路单频光纤激光器的波长间隔为5~30 pm,根据拍频计算:

(1)

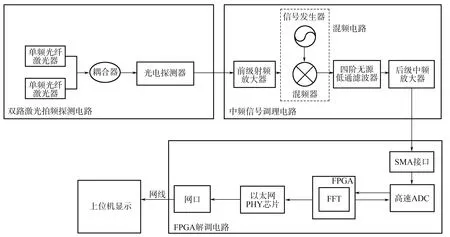

其中:波长λ=1 545.5 nm,光速c=3.0×108m·s-1,Δλ=5~30 pm,计算出理论上经光电探测器输出的拍频电信号的频率为0.63~3.77 GHz[4]。若直接通过高速ADC将射频域拍频信号采集到FPGA中进行处理,对ADC的采样速率要求高,采样率在GHz的ADC价格昂贵,技术指标要求高。可先将拍频信号下变频,再由高速ADC采样到FPGA中进行数字信号处理。电路的系统框图见图1。由图1可见,两台中心波长为1 550.001~1 550.601 nm的单频光纤激光器发出双路激光信号,经2×1耦合器在合束的过程中产生光的干涉,照射到光电探测器的光敏面上产生拍频信号,探测器的响应速度较快,能够输出拍频电信号,信号的频率为几个GHz。在中频信号调理电路中,拍频信号经0.05~6 GHz前级射频运算放大器的处理后送入混频电路模块,高增益的射频放大器可放大微弱信号的功率值。在混频电路中能够将射频域信号下变频为中频信号,其中混频器可提供10 MHz至6 GHz的宽动态范围频率转换,本振信号发生器能够输出35~4 400 MHz的本振信号。再通过截止频率为50 MHz的低通滤波器以及0.01~2 GHz后级中频放大器的滤波放大后将信号传输到FPGA解调电路中,中频调理后的拍频电信号传入高速ADC中进行模数转换,FPGA采集转换好的时域信号经FFT作用后实现时频变换,从而解析出双路激光的频差信息,最后通过千兆网口通信,将测量信息传输至PC机上存储与显示。

图1 双路激光拍频解调电路Fig.1 Dual laser beat frequency demodulation circuit

1.1 混频电路

在混频电路中,通过本振信号发生器产生射频域本振信号与拍频信号在混频器中下混频,将拍频信号下变频为中频信号。电路输出拍频信号频率为0.41~3.45 GHz,采用ADF4351频率合成器芯片作为本振信号发生器的主控芯片,通过三线式串行接口配置ADF4351片内寄存器,使其能够任意输出35~4 400 MHz的本振信号[5],功率为-9~0 dBm。

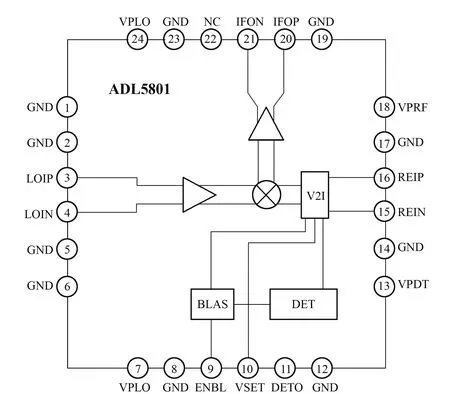

混频器是实现双路激光拍频解调的关键模块,经过前级射频放大器处理后的拍频信号需下混频才能将信号搬移至中频,通过混频器调频拍频信号频率降为50 MHz以内的中频信号,在此条件下更利于实现数字信号采样,以及后续基于FPGA的拍频信号频率解调。根据电路设计指标,ADL5801有源混频器芯片较适合本设计,其功率转换增益为1.8 dB,SSB噪声系数为9.75 dB,输入IP3为28.5 dBm,1 dB压缩点为13.3 dBm,可提供10 MHz至6 GHz的宽动态范围频率转换。

基于ADL5801的内部功能框图见图2。由图2可见,主要由混频器内核、LO放大器、RF电压电流转换器、RF检波器以及偏置电路组成。ADF4351输出的本振信号经LO放大器后进入混频器内核,光电探测器输出的拍频信号被RF电压电流转换器转换为射频电流,与本振信号一起进入混频器内核,偏置电路为各模块提供基准电流。此外,射频输入端口RFIP/RFIN的输入功率为0~20 dBm,本振输入端口LOIP/LOIN的输入功率为-10~10 dBm,混频输出端口IFON/IFOP的输出功率最大值为0 dBm。

图2 ADL5801内部功能Fig.2 ADL5801 internal function

1.2 FPGA内高速ADC控制模块设计

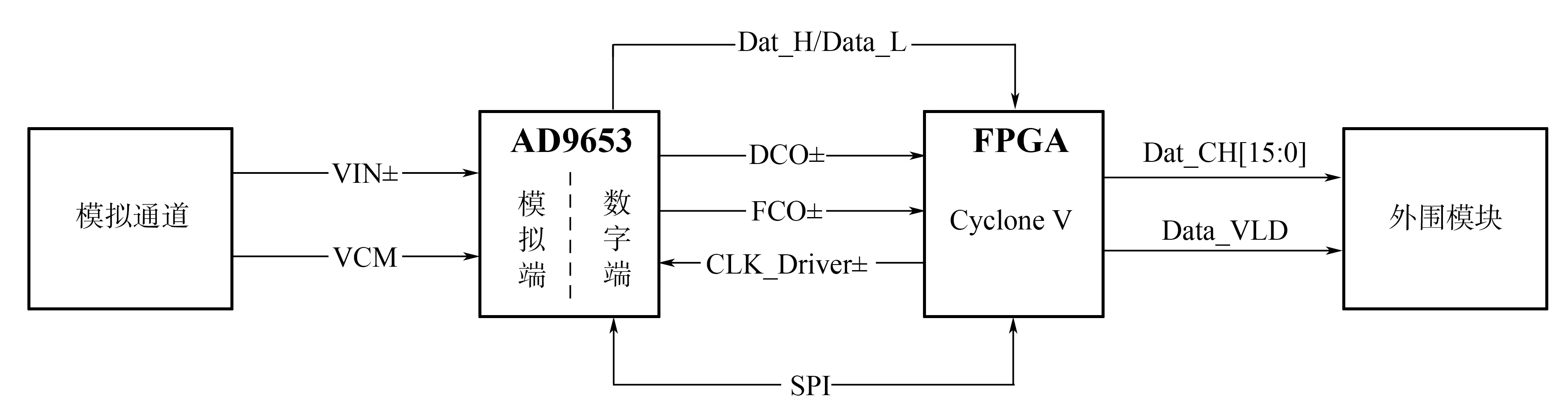

根据FPGA解调电路的设计需求,高速ADC选用Analog Devices公司生产的模数转换芯片AD9653实现,该芯片为4通道、16位、采样速率最高可配置为125MSPS的串行LVDS(低电压差分信号)模数转换器[6]。根据AD9653芯片特性,所设计的高速ADC控制模块的连接关系见图3。

图3 高速ADC控制模块连接关系Fig.3 High speed ADC control module connection

模拟端,AD9653支持4通道同步模数转换,而在本设计中,只需利用单通道。由于芯片的模拟输入接口不存在直流偏置,在交流耦合中,需利用VCM引脚提供电平大小为VCM=AVDD/2的共模基准电压,AVDD为模拟电源引脚。

数字端,FPGA芯片与AD芯片以及外围模块相连,其中DCO±、FCO±、CLK_Driver±为时钟引脚,DCO±、FCO±由AD芯片输入FPGA内,作为FPGA接收离散数据时的位对齐与帧对齐,CLK_Driver±则由FPGA输入AD芯片内部,作为供ADC工作的采样时钟,频率大小为125 MHz。Data_H/Data_L为经ADC转换完成的单比特高8位数据与低8位数据,由AD9653输入到FPGA内部后,以差分帧输出时钟FCO±为基准进行串并转换后由Data_CH接口输出,供外围其它模块使用。Data_VLD为16位数据转换完成标志信号,每当一帧数据转换完成后,拉高Data_VLD信号。AD9653中的SPI接口由SDIO、SCLK和CSB 3个引脚组成,SCLK为串行时钟引脚,用于同步写入和读取数据,时钟频率为25 MHz;SDIO为串行输入输出引脚,用于将数据写入内部寄存器或从内部寄存器中读取数据;CSB为片选引脚,低电平有效,用于控制启用或禁用读写周期。在硬件电路设计中,SPI 3个引脚都直接与FPGA相连,由FPGA根据具体情况设置SPI引脚的电气标准,通过SPI接口编程控制ADC内部的结构寄存器,为模数转换器配置特定的功能或操作。由于AD9653默认采样率为20MSPS,因此需要通过SPI配置使其采样率达到最高,即125MSPS。

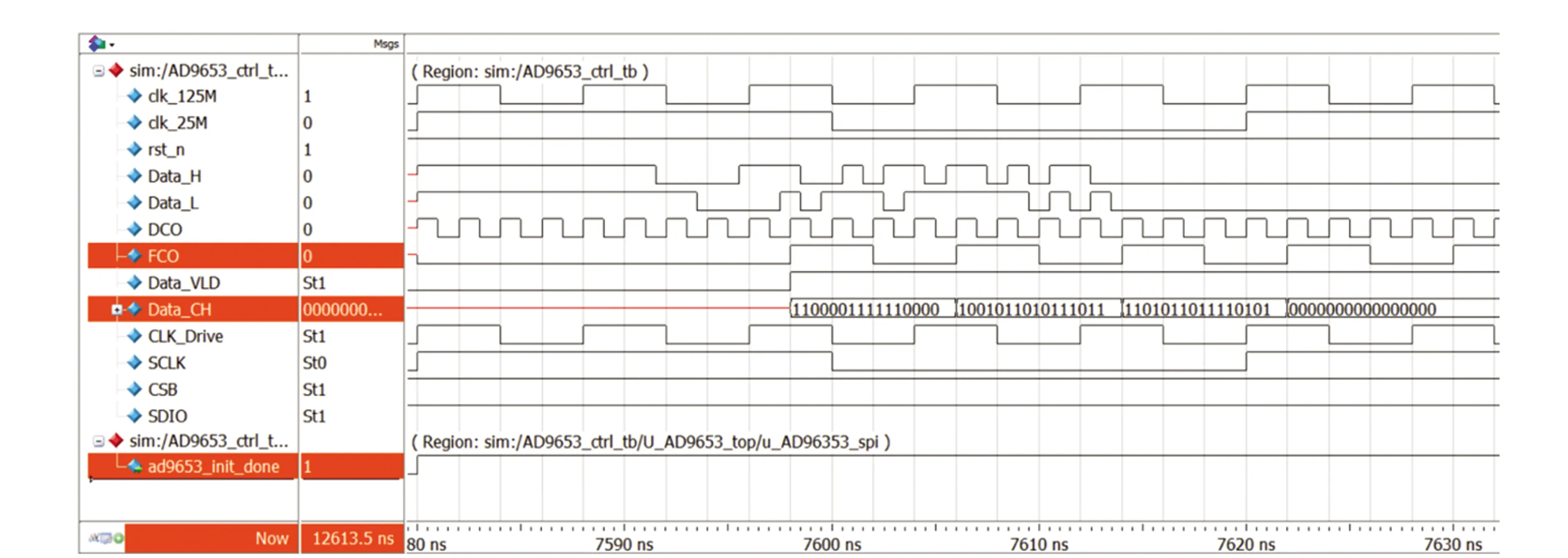

在QuartusⅡ13.1开发环境中编写高速ADC控制模块RTL代码以及测试文件,经分析综合后在Modelsim中的仿真波形见图4,符合AD9653的工作时序。当SPI配置完成,即初始化完成信号AD9653_int_done拉高时,SPI初始化成功,AD9653开始进行数据传输。

图4 AD9653控制模块功能仿真Fig.4 AD9653 control module function simulation

功能仿真后,对高速ADC控制模块进行上板验证,其中信号发生器的模拟信号输出端连接AD9653的通道一,AD9653的工作状态受FPGA控制。设置信号发生器输出频率10 MHz、幅值2 V的正弦波信号后,将程序烧录到FPGA芯片,通过Signal Tap Ⅱ Logic Analyzer(逻辑分析仪)软件实时抓取信号线上的数据,以此观察设计中内部节点情况,在逻辑分析仪中,设置采样时钟频率为50 MHz,采样深度设置为64 k,得到的AD9653采样波形见图5。由图5可见,对输入数据解串行后,16位并口Data_CH显示了所抓取到的10 MHz规律正弦波信号。

图5 逻辑分析仪抓取到的ADC采样波形Fig.5 Logic analyzer captures ADC sampling waveform

1.3 FPGA内FFT数值处理模块设计

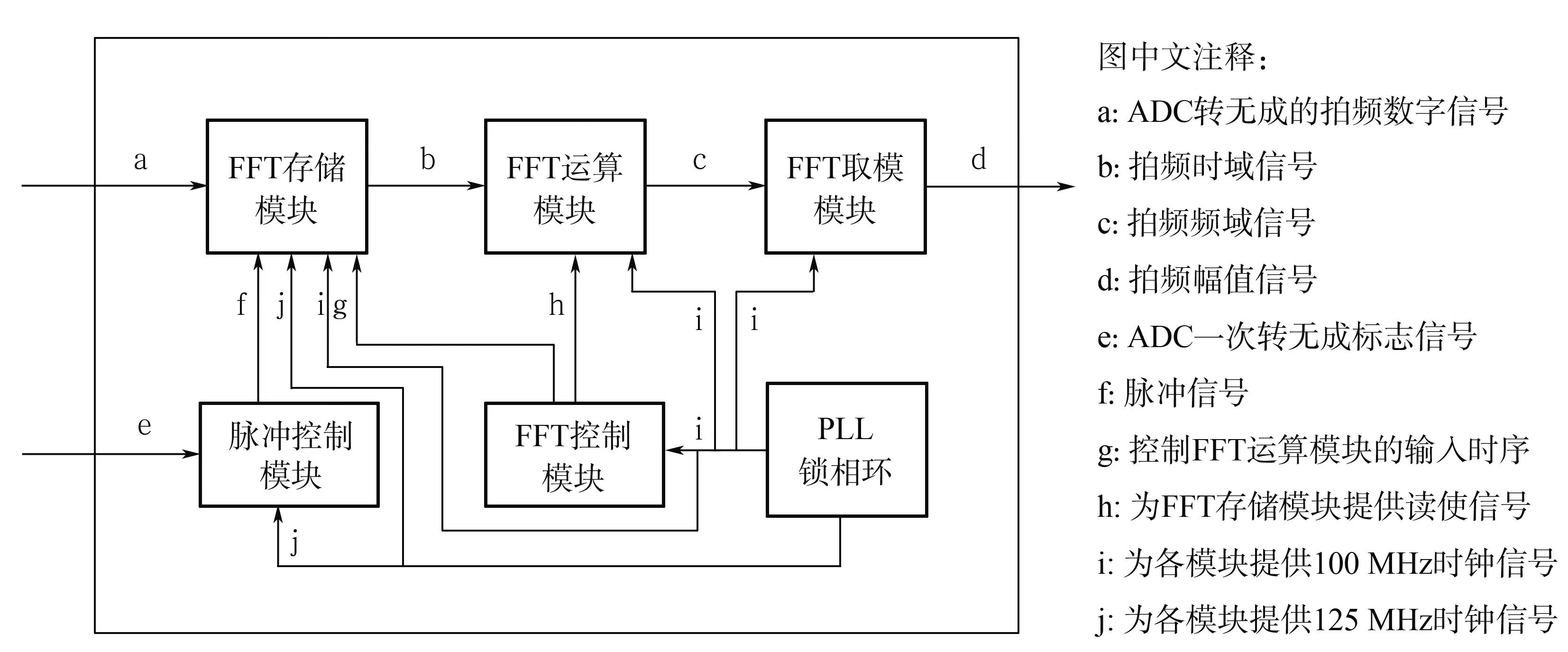

双路激光拍频信号经过混频器、低通滤波器处理后得到50 MHz以内的中频信号,应用高速ADC将中频信号采集到FPGA解调电路中进行数字信号处理,其中,FFT数值处理模块是FPGA解调电路设计的核心。FFT数值处理模块由脉冲控制模块、FFT运算模块、FFT存储模块、FFT控制模块、FFT取模模块组成,通过FFT数值处理模块完成点序列时频变换,解析出双路激光拍频信号的频谱信息。该模块的计算量占到本设计中FPGA计算量的70%以上,因此提高FFT数值处理模块的运算效率可直接提升FPGA解调电路的实时性能。FFT数值处理模块系统框图见图6。

图6 FFT数值处理模块功能Fig.6 FFT numerical processing module function

FFT的变换速度以及点数可提高FFT解调的实时性以及频率分辨率。选择Quartus Ⅱ 13.1提供的资源耗费和吞吐量都较大的Streaming模式下的FFT_v13.1 IP核来完成时频变换。配置该IP核的输入数据长度=16 384,输入序列为二进制补码格式的顺序复数序列,转换完成后分别倒序输出转换后序列的实部与虚部[7-8]。

在Quartus Ⅱ13.1FPGA开发环境中应用Verilog HDL硬件描述语言按照模块化的设计思想对各子模块进行了设计与仿真,构建了FFT数值处理模块。FFT数值处理模块的工作原理如下:脉冲控制模块pulse_ctrl输出占空比约为0.4的脉冲信号pulse传入FFT存储模块dcfifo1的写请求端口wrreq,实现对经ADC采集进来的拍频数字信号data_in的截取处理,将输入数据的速率降为50 MHz。FFT存储模块缓存脉冲处理后的数字信号,当存储模块不为空且由FFT运算模块,即FFT IP核传递给FFT控制模块fft_ctrl的准备完成信号fft_ready有效时,FFT存储模块的读请求信号rdreq被拉高,控制存储模块读取数据并传递到FFT运算模块的实部输入数据信号线sink_real上,并使输入数据能够满足FFT内核所要求的Streaming I/O数据流格式,每一帧将16 384个采样值传入FFT 内核,由于输入数据只有实部,所以将FFT 内核的虚部输入数据信号线sink_imag接地。最后将每一帧时频变换后得到的实部source_real与虚部source_imag依次送入FFT取模模块data_modulus即可计算出双路激光拍频信号的模值,经过16 384个时钟周期后,将计算结果data_modulus以倒序方式依次存入外部存储器中,完成FFT数值处理模块全部计算。

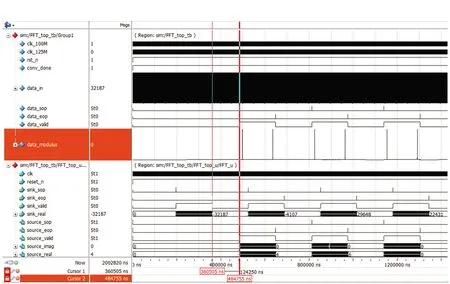

通过Matlab生成10 MHz的模拟正弦波输入文件读取到Quartus Ⅱ13.1中,编写FFT数值处理模块测试文件,经编译后在Modelsim中的仿真波形见图7。由图7可见,3帧16 384点长度的FFT模值数据,即双路激光拍频信号3次FFT变换各频率点下的幅值信息,由于FFT幅值结果具有对称性,在每一帧中可以清晰地分辨出两个成中心对称的频率成分,即10 MHz的正弦信号。每一帧数据的传递均由sop、eop、valid信号组成,且连续传输,满足Streaming I/O数据流格式。在这种算法下完成数据录入的时间点为360.504 961 μs,完成数据输出时间点为484.752 936 μs,中间计算时间为124.247 975 μs。

图7 FFT数值处理模块功能仿真Fig.7 FFT numerical processing module function simulation

使用Matlab验证FFT数值处理模块的Modelsim仿真结果,在Matlab中调用同样的FFT算法对10 MHz时域数据进行运算,并且控制其余变量均相同,将Matlab运算得到的结果与Modelsim仿真结果进行比较,结果对比见图8。由图8可见,两者计算产生的频谱图几乎重合,能够清晰地分辨出10 MHz信号的频率谱峰,由于Matlab产生的计算结果可认为是准确的,因此FFT数值处理模块的Modelsim仿真结果具有很高的准确度,进一步验证了在FPGA内所设计的FFT数值处理模块的正确性,在一定的误差范围内,利用FFT数值处理模块能够实现对拍频信号频谱数据的准确解调。

图8 Matlab与Modelsim仿真结果比较Fig.8 Comparison of simulation results between Matlab and Modelsim

2 电路测试

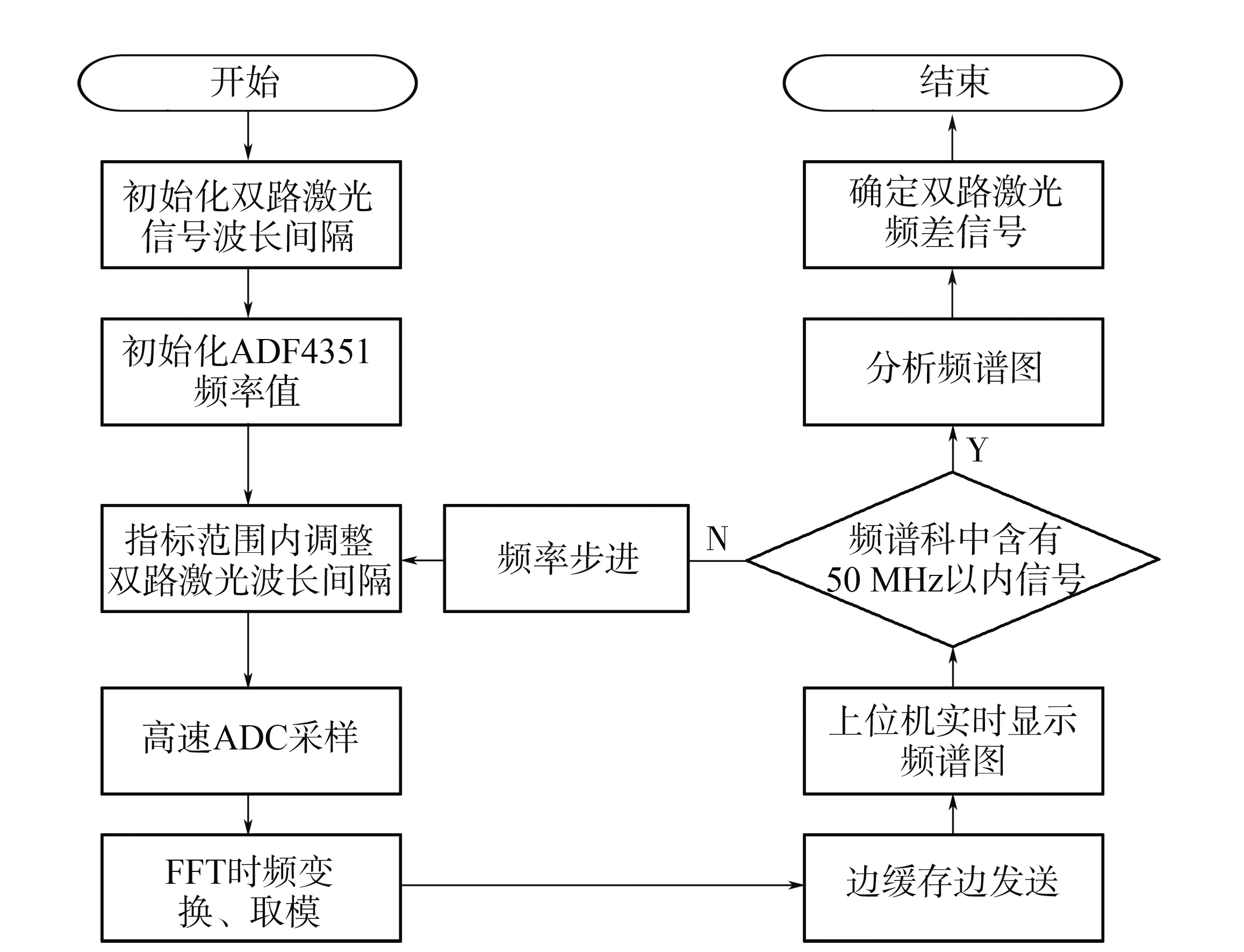

双路光纤激光拍频信号解调电路的总体测试流程见图9。上电后首先初始化双路激光信号的波长间隔、ADF4351本振信号发生器频率以及功率值,然后根据实验指标,即在5~30 pm内手动调整双路激光波长间隔值,以及连续调整ADF4351输出本振信号的频率值,每次频率步进后,FPGA控制高速ADC连续采样中频调理后的拍频信号并通过FFT数值处理模块进行时频变换、取模。由于通过FFT变换得到的频谱数据具有对称性,因此每次取半帧,即8 192点数据长度的频谱计算结果边缓存边通过千兆网络发送至上位机存储显示,若频谱图中含有50 MHz以内的频率谱峰,说明下变频完成,固定本振信号频率值。最后分析确定出频谱图中信号的频率值与本振信号频率值相加,即可解析出双路激光信号的频差信息。

图9 电路总体测试流程Fig.9 Overall circuit test flow

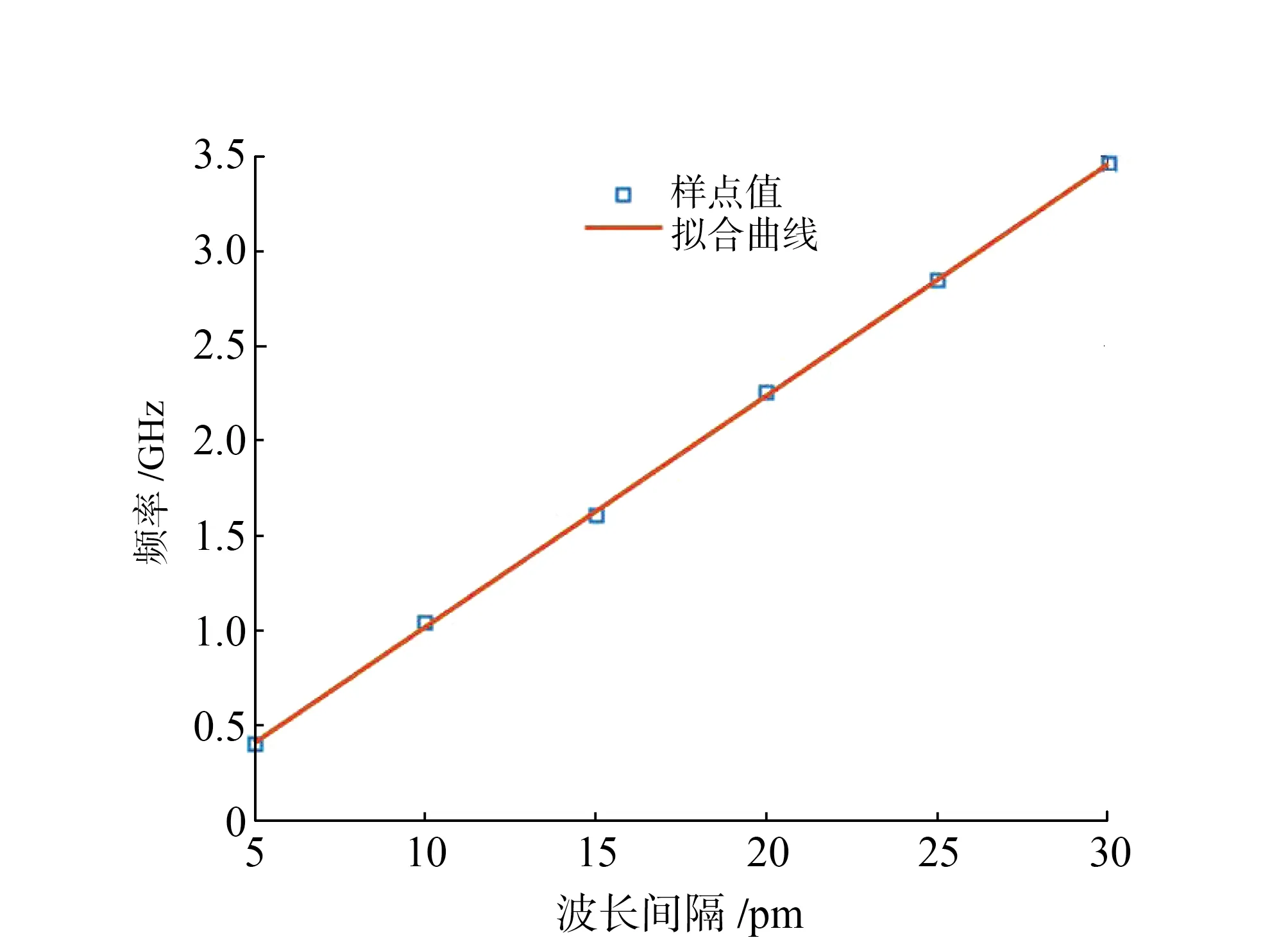

固定一台单频光纤激光器的波长为1 550.210 nm,在实验指标范围内以5 pm为单位,通过逐次改变另一台激光器的波长来调整双路激光信号的波长间隔,通过实验得到的6组数据见表1,经拟合得到的拍频信号频率值随波长间隔变化关系见图10。由图10可见,双路激光拍频信号的频率值随波长间隔的增大而增大,两者呈良好的线性关系。

图10 拍频信号频率随波长间隔变化关系Fig.10 Relationship between beat frequency and wavelength interval

表1 双路激光拍频探测电路测试数据Table 1 Test datas of dual laser beat frequency detection circuit

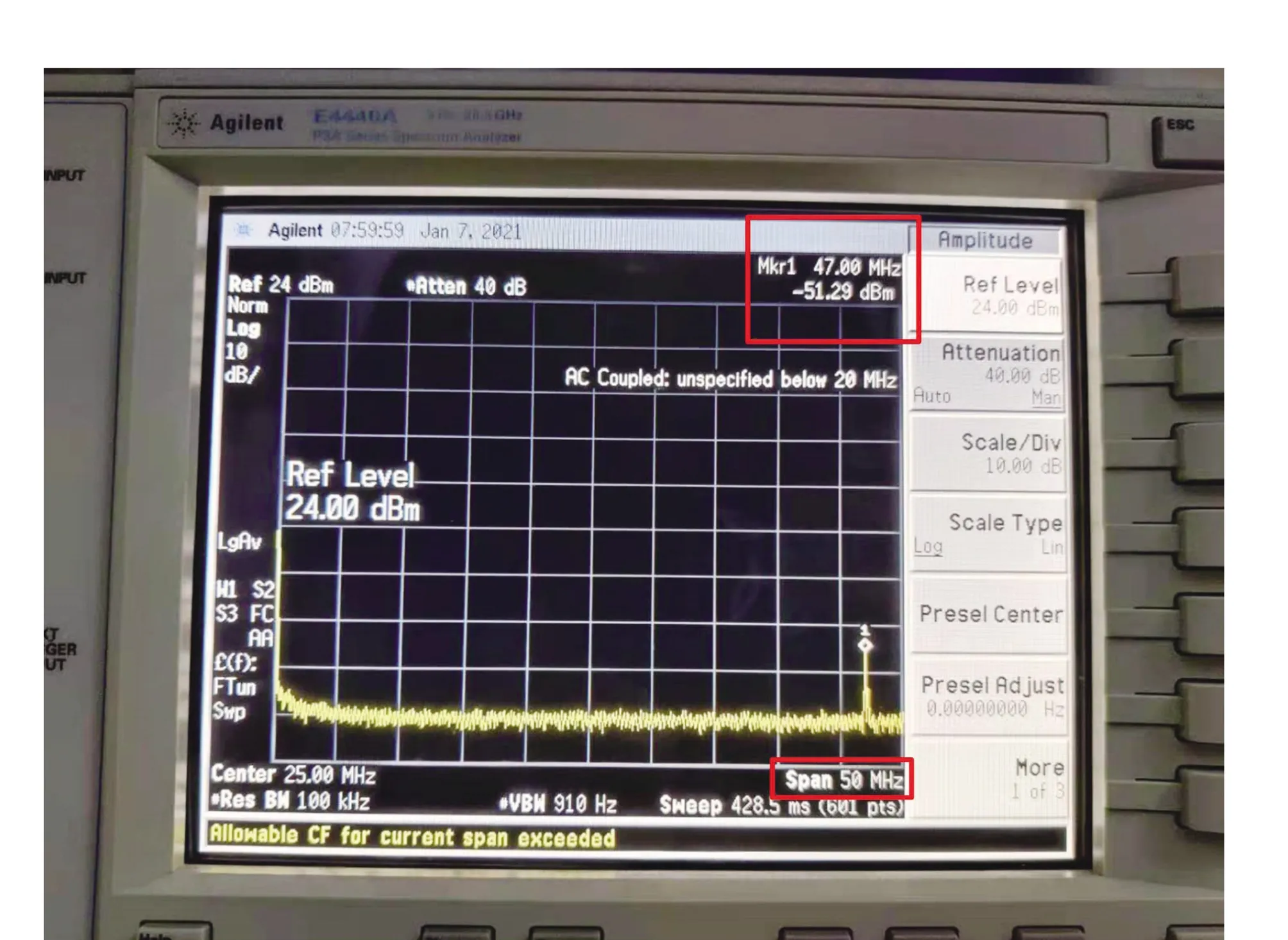

在5~30 pm范围内每次固定双路激光波长间隔后,调整ADF4351本振信号发生器输出信号的频率值,使得经光电探测器探测产生的射频域拍频信号与本振信号在混频电路中发生混频后,通过E4440A频谱仪能观测到50 MHz以内的拍频信号。波长间隔为30 pm时,当调整本振信号发生器输出3.407 GHz的信号时,频谱仪中出现了47.0 MHz的中频信号,见图11。由于实验室环境信号干扰,频域仪中加入了40 dB衰减,在0~50 MHz内无其他频率干扰信号,在高频域有经混频器输出的和频以及其他组合频率的信号,通过通带截止频率为50 MHz的椭圆低通滤波器滤除即可。

图11 频谱仪读取混频信号频率值Fig.11 Spectrometer reads frequency value of mixing signal

现固定双路激光信号波长间隔为5~30 pm内的某个值,连续调整ADF4351本振信号发生器输出信号的频率值,当频率为1.013 GHz时,经混频滤波后上位机频谱图内含有50 MHz以内的频率信号,在该条件下得到的频谱图见图12,由于采样频率为125MSPS,FFT变换点数为16 384点,根据下式:

图12 上位机实时解调频谱Fig.12 Real time demodulation spectrum of upper computer

Δf=fs/N

(2)

可计算出频率分辨率约为7.6 kHz。可见,存在一定噪声,但仍能够清晰地分辨出25.7 MHz信号的频率谱峰,将其与本振信号的频率值相加即可解析出双路激光信号的频差信息。

3 结 论

将模拟与数字、混频技术与FFT时频变换相结合,设计了一种小型化、低成本、高分辨率、实时性好的基于FPGA的双路光纤激光拍频信号解调电路。经实验证明,本电路可以实现5~30 pm内双路光纤激光波长间隔的实时解调,应用于光纤传感系统中,能够准确推测出外界传感信息作用的大小。