一种宽温度范围的低温度系数带隙基准源设计

2021-09-02安景慧吴晨健

安景慧,吴晨健

(苏州大学 电子信息学院,江苏 苏州 215000)

近年来,物联网飞速发展,其产品已涉足工业监控、智能家居、运输物流、智慧医疗等多个领域,实现了万物广泛互联、人机深度交互,改变了人们的生活、工作和娱乐方式。半导体芯片是物联网产业链不可或缺的重要部件之一,随着物联网应用场景越来越多样化,芯片的精度和可靠性成为急需解决的问题。

带隙基准源是物联网系统中模拟芯片和数模混合芯片的基本组成单元,其主要作用是输出一个不受工艺、电源电压和温度变化影响的稳定电压。评判带隙基准源性能好坏的指标有温度系数、电源抑制比、直流功耗、面积等。指数曲率补偿、对数曲率补偿等各种曲率补偿技术被用来改善输出基准电压的温度特性[1-2],从而降低带隙基准源的温度系数。但是这些电路通常只能在-40 ℃~125 ℃甚至更窄的温度范围内工作,无法满足军工级芯片的要求。线性稳压器、套叠电流镜等电路结构被用来提高带隙基准源的电源抑制比[3-5]。亚阈值设计、衬底驱动技术等被用来减小带隙基准源的直流功耗[6-8]。然而这些电路在优化电源抑制比、减小直流功耗的同时牺牲了电路的温度系数。

针对工作温度范围较大的物联网应用场景对芯片温度适应能力及可靠性的要求,笔者设计了一种在宽温度范围内正常工作的低温度系数带隙基准源电路,同时兼顾了电源抑制比和功耗等其他性能。基于改进后的Banba型带隙基准源结构,电路利用工作在亚阈值饱和区晶体管的漏电流特性对双极性晶体管的基极发射极电压进行高阶温度补偿,降低电路的温度系数。利用分段温度补偿技术对较高温度范围内输出基准电压作进一步曲率补偿,扩展整个电路的工作温度范围。

1 改进的Banba型带隙基准源电路分析

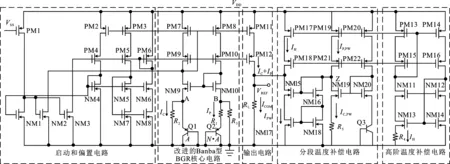

传统的Banba型带隙基准源利用运算放大器的钳位功能确保两点的电势相等[9]。这要求运算放大器具有较高的增益,从而增加电路的功耗和复杂性,且运放的失调会影响输出基准电压的精度。因此,笔者提出了无运放的Banba型带隙基准源电路结构,如图1所示。

图1 低温度系数带隙基准源整体电路图

晶体管NM9、NM10、PM7~PM10组成套叠威尔逊电流镜,该结构输出阻抗大,电流传输精度高,其功能是保持A、B两条支路的电流大小相等以及A、B两点电压相等。电阻R2和R3的阻值相同,则流过两电阻的电流相等,可以表示为

(1)

套叠电流镜PMOS晶体管宽长比相等,不考虑沟道长度调制效应,则三条支路的电流大小相等。若晶体管Q1和Q2的发射极面积之比为1∶N,则流过电阻R1的电流为

(2)

其中,VT为热电压,等于kT/q,k是玻尔兹曼常数,值约为1.38×10-23J/K;q为电荷量,值约为1.6×10-19C。

电流IC具有负温度系数,电流IP具有正温度系数。电流IC和电流IP通过电流镜镜像到输出电路,通过电阻RL转换为输出基准电压Vref,其表达式为

(3)

通过调节R2和R1的比值以及N,可以实现对VEB1的一阶温度补偿。

2 低温度系数带隙基准源设计

2.1 高阶温度补偿电路设计

理论上,改进的Banba型带隙基准源电路可以产生一个零温度系数的输出电压。但是,双极性晶体管的基极-发射极电压的温度特性具有高阶非线性,其表达式为[10]

(4)

其中,Vg0是0 K时硅的带隙能量,值约为1.12 eV;T为任意温度,Tr为某一特定温度;η和α分别为载流子迁移率和集电极电流的温度依赖阶数。

式(4)中的第3项表明了VBE的高阶非线性。为了简化分析,将式(4)以泰勒展开,得到

VBE=VG(Tr)-bT-cT2-… 。

(5)

当温度在150 K(-123 ℃)到400 K(127 ℃)之间时,VG(Tr)在1.178 85 V到1.205 95 V之间变化,b介于9.025×10-5到2.733×10-4之间,c介于3.05×10-7到0之间。为了降低高阶温度项对输出基准电压的影响,设计了高阶温度补偿电路,如图1所示。

当晶体管的栅源电压小于其阈值电压但大于其本征电压时,半导体表面已经反型,所以当外加漏源电压后,MOS管也能导电,只是少子浓度较小,MOS管处于亚阈值区,对应的电流称作亚阈值电流(I),表达式为

(6)

其中,C0是单位面积氧化物电容,μ是沟道载流子的有效迁移率,W/L是MOS管的宽长比,m和n是工艺相关的参数,VDS是晶体管的栅源电压。当VDS≥4VT时,式中含VDS的项可以被忽略。

晶体管NM13和NM14工作在亚阈值饱和区。忽略晶体管体效应,根据式(6)可以得出流过电阻R4的电流为

(7)

其中,参数n不仅与工艺相关,也是温度T的函数。将n用泰勒级数展开,n与温度T的关系可以表示为

n(T)=E+FT+GT2,

(8)

其中,E、F都是正的常数。假设[(I14/I13)(W/L)13/(W/L)14]=α(α>1),将式(8)代入式(7)中,得到高阶温度补偿电流IH的表达式为

(9)

从式(9)可以看出,电流IH具有正温度系数的高阶项,通过电流叠加可以实现对电压VBE的高阶温度补偿。

2.2 分段温度补偿电路设计

与一阶温度补偿相比,经过高阶温度补偿的带隙基准源输出电压曲线通常接近正弦曲线,输出电压的温度特性得到改善。随着温度的升高,输出电压会急剧增大;为了扩展带隙基准源的工作温度范围,设计了分段温度补偿电路,如图1所示。

电流IC,PW是由双极性晶体管Q3产生的CTAT电流,电流IP,PW是通过电流镜镜像得到的PTAT电流。若定义电流IP,PW等于电流IC,PW时的温度为TPW。当温度低于TPW时,IP,PW小于IC,PW,节点Z的电压降低,导致晶体管NM7工作在线性区,NMOS电流镜中没有电流流过。当温度高于TPW时,IP,PW大于IC,PW,节点Z的电压上升,从而在NMOS电流镜产生补偿电流IPW,其表达式为

(10)

2.3 整体电路设计

笔者提出的低温度系数带隙基准源由启动和偏置电路、改进的Banba型带隙基准源核心电路、高阶温度补偿电路以及分段温度补偿电路组成,如图1所示。

最终的输出参考电压等于总补偿电流ICOM乘以负载电阻RL。总补偿电流ICOM是电流IC、电流IP、高阶补偿电流IH和分段补偿电流IPW的线性加权总和。因此,输出参考电压可以表示为

VREF=RL[k1(IC+IP)+k2IH+k3IPW]=RL[k1(IC+IP)+k2IH+k3(IP,PW-IC,PW)]。

(11)

通过改变权重k1、k2、k3可以使电路在宽温度范围内实现低温度系数,且电压值可以通过改变电阻RL进行调节。

3 芯片测试结果与分析

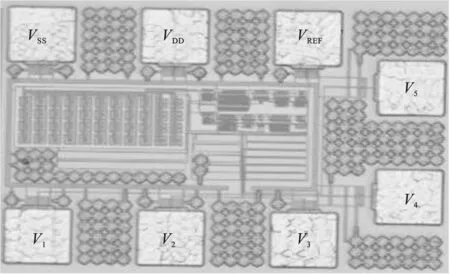

利用Cadence Spectre仿真软件对提出的带隙基准源电路进行了前仿真、版图设计以及后仿真,最终采用TSMC 180 nm CMOS工艺进行流片。芯片显微镜照片如图2所示。

图2中V1~V5为电阻修调网络控制开关焊盘,VREF、VDD、VSS分别为输出参考电压、电源、地焊盘,芯片核心面积为0.025 mm2。将带隙基准源裸片用金线键合到测试PCB 板上,封黑胶加以固定,再对芯片进行测试。芯片测试环境如图3所示。

图2 带隙基准源芯片显微镜照片

图3 芯片测试环境

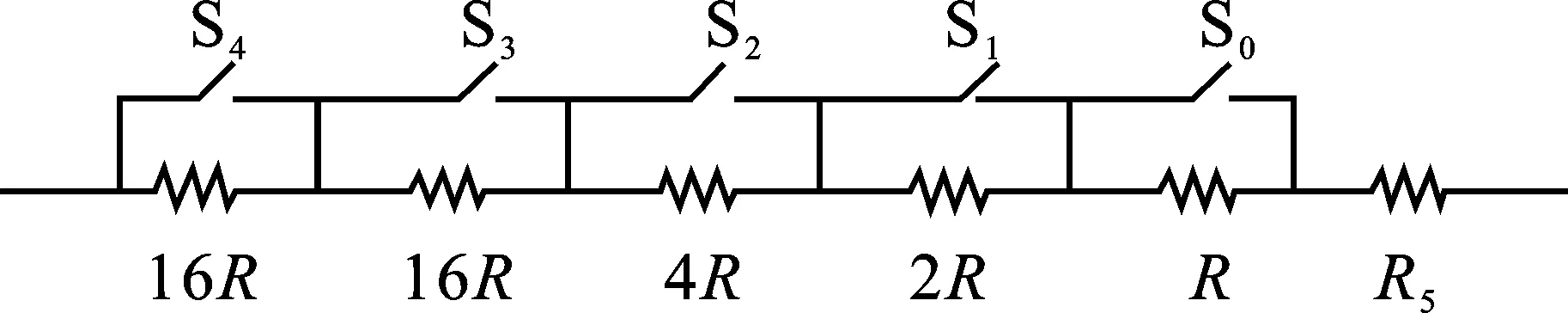

图4 电阻修调网络

为了减小工艺角变化对输出基准电压的影响,设计了一个5位电阻修调网络,如图4所示。通过控制开关S0~S4的开闭实现对电阻R5的修调,从而使带隙基准源在较高温度范围内仍具有良好的温度特性。当开关断开时,修调电阻与电路串联,分段补偿电流IC,PW减小,由于式(11)中的系数k3小于0,因此输出基准电压减小。相反,当开关闭合时,修调电阻与电路断开,输出基准电压增大。

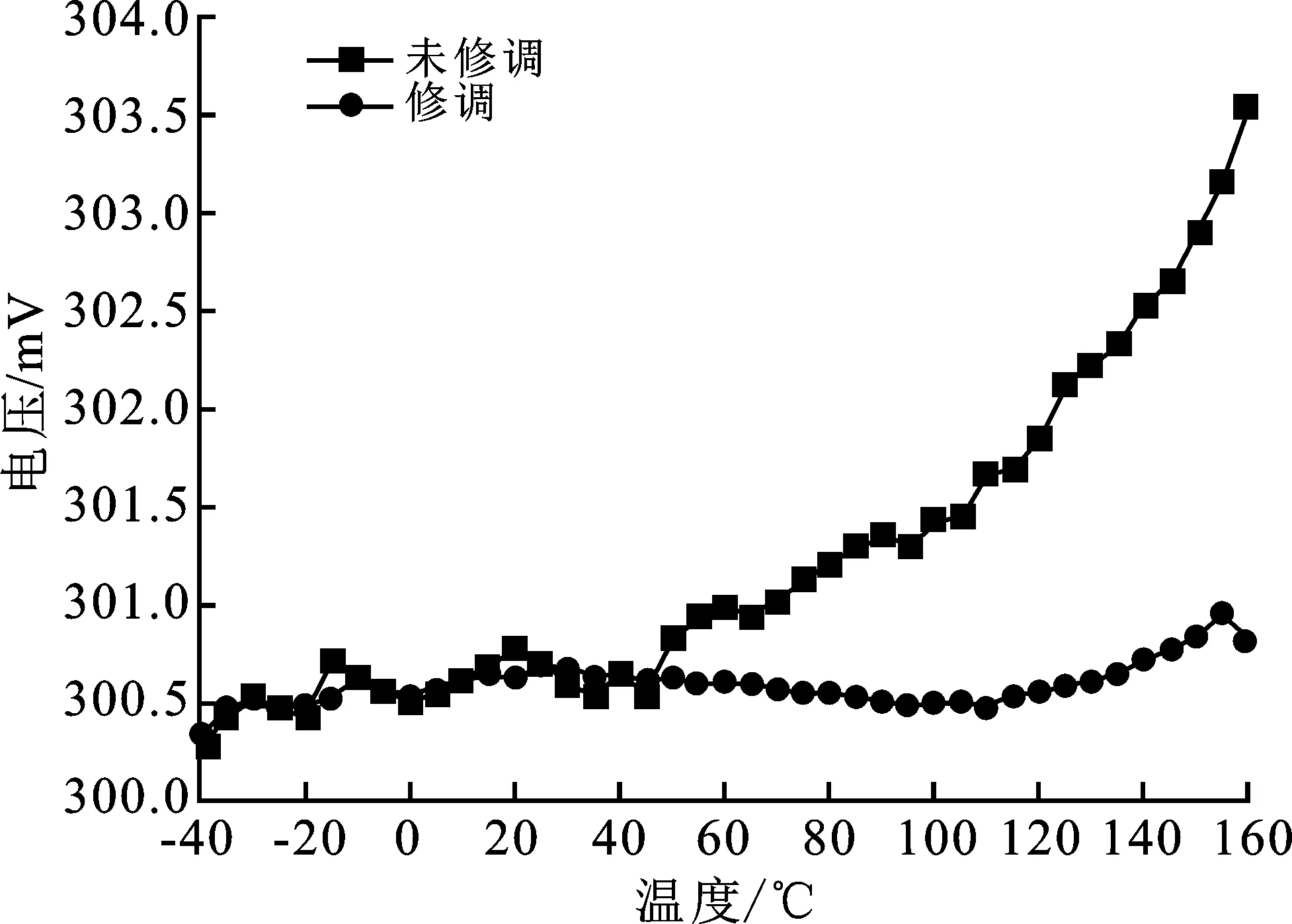

图5 修调前后输出参考电压的温度特性线

图5展示了一个样本芯片修调前后的温度特性曲线。在低温度范围时,分段补偿电路不工作,修调前后输出电压的温度曲线接近。在高温度范围时,分段补偿电路开始工作,电阻修调网络使输出电压的温度特性曲线得到了明显改进,输出电压修调前后的变化最大为3 mV。

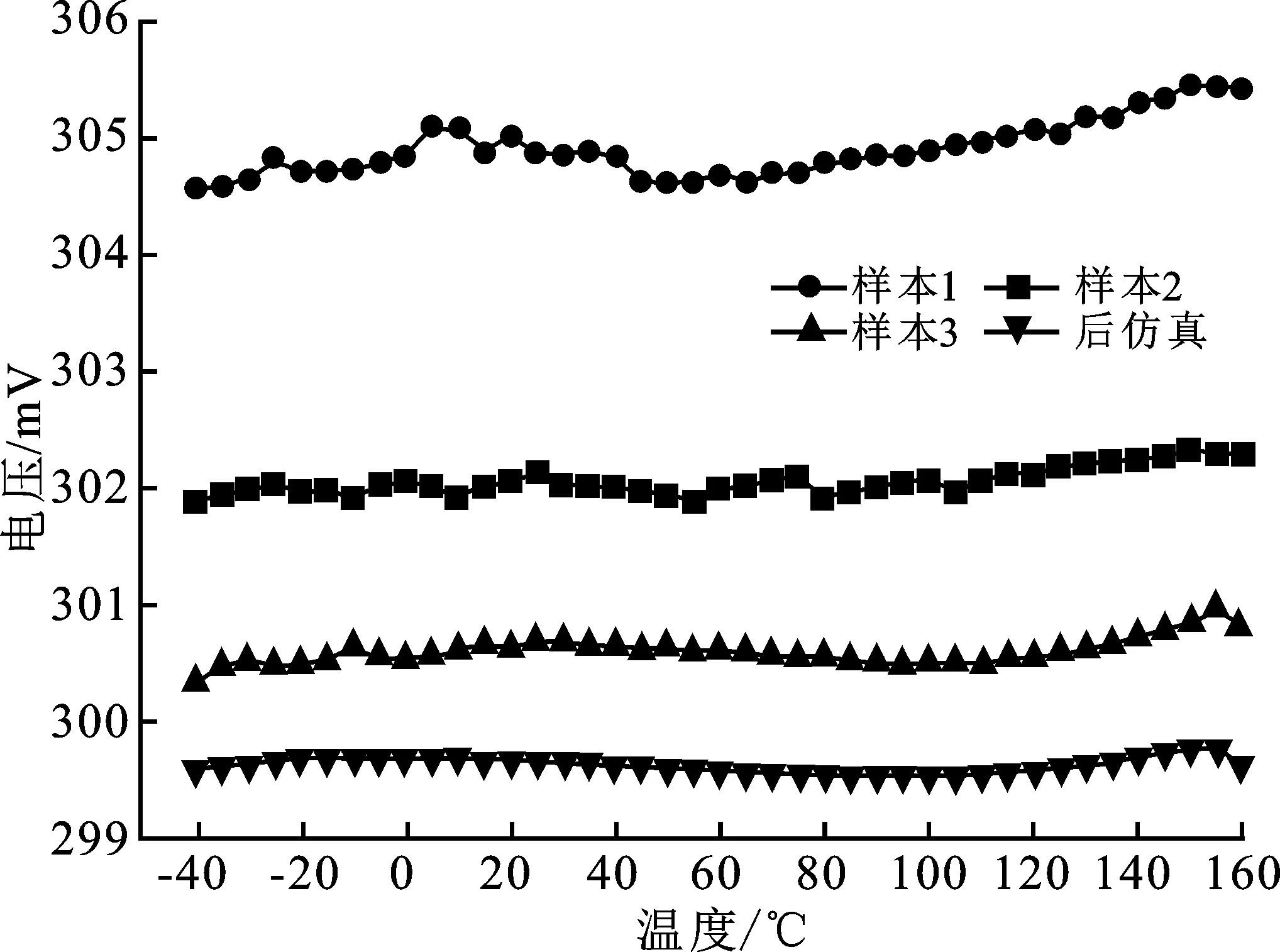

图6给出了3个样品芯片在-40 ℃~160 ℃温度范围内输出电压随温度变化的曲线。3个样品在 -40 ℃~160 ℃宽温度范围内的温度系数分别为14.5×10-6/℃、7.2×10-6/℃、10.3×10-6/℃,平均温度系数为10.6×10-6/℃。从带隙基准源的样品测试曲线和后仿真曲线的对比可以看出,笔者提出的高阶补偿电路和分段补偿电路得到了验证。但是芯片实测的温度系数比后仿真结果高2.6×10-6/℃,造成这一差异的原因有电流镜失配、电阻失配和沟道长度调制效果等。

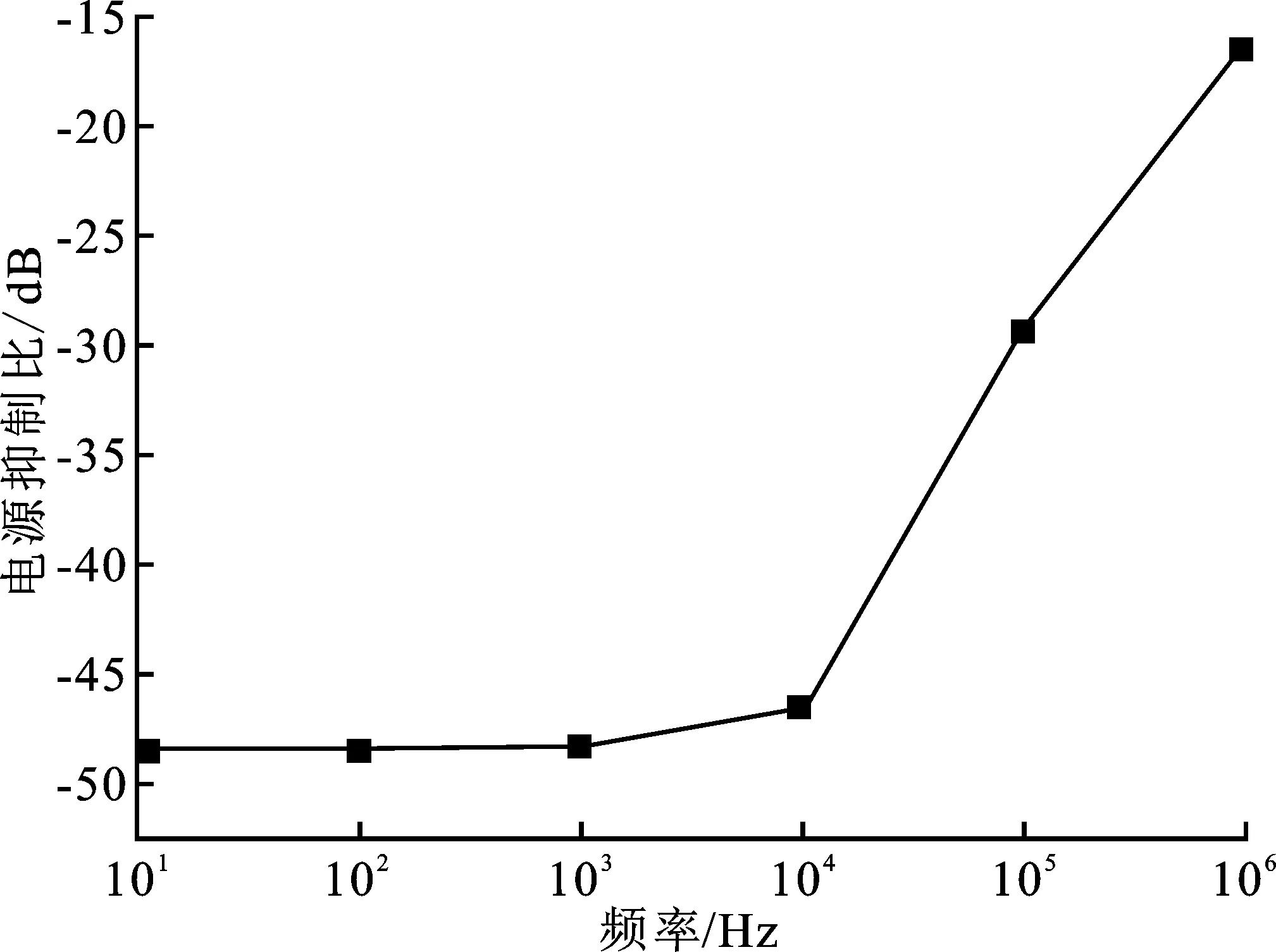

图7给出了带隙基准源的电源抑制比测试曲线。低频时电源抑制比为-48.52 dB,随着频率增加到 1 MHz 时,电源抑制比减小至-15 dB。测试结果表明,电源电压的噪声对提出的带隙基准源具有一定影响。

图6 带隙基准源温度系数测试曲线

图7 带隙基准源电源抑制比测试曲线

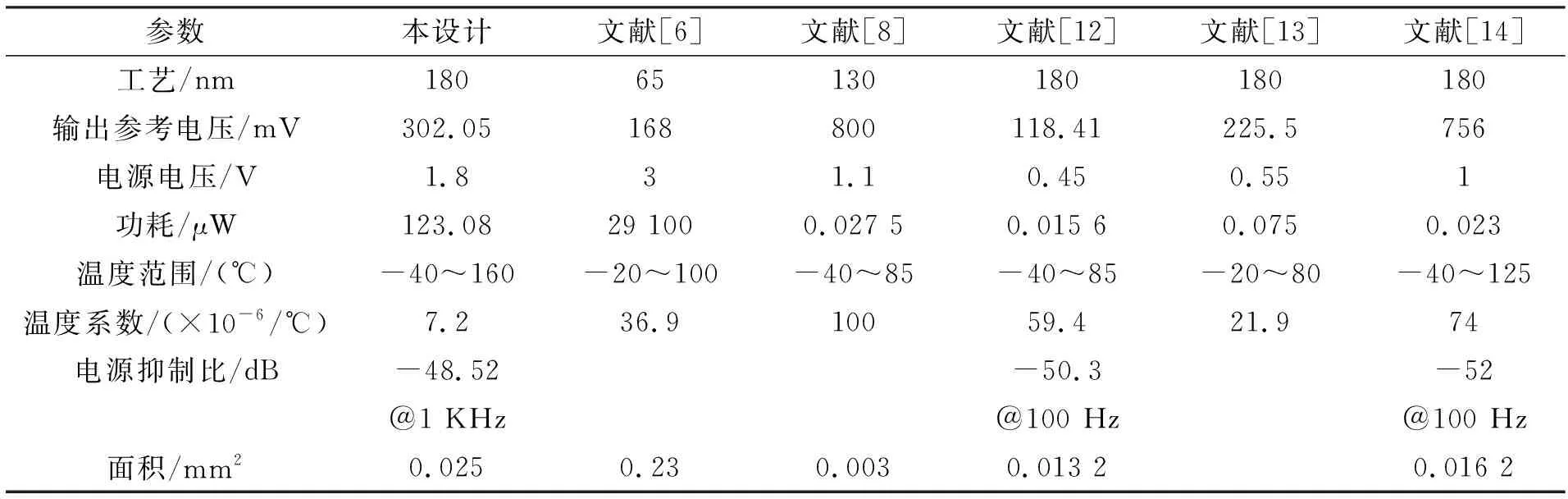

表1总结了本设计与现已发表文献的带隙基准源的性能对比。在保证电源抑制比、功耗、芯片面积等性能指标的前提下,笔者提出的带隙基准源电路的温度系数低至7.2×10-6/℃,明显优于其他电路。值得一提的是,笔者所提出的带隙基准源具有更宽的工作温度范围,其应用场景更加广泛。

表1 本设计与参考文献性能指标对比

4 总 结

笔者提出了一款高精度的带隙基准源,电路利用高阶温度补偿技术和分段温度补偿技术实现了低温度系数,同时扩展了工作温度范围。电路通过CMOS 180 nm工艺进行验证。测试结果表明,在-40 ℃~ 160 ℃ 宽温度范围内输出基准电压的温度系数最低为7.2×10-6/℃,适用于各种物联网领域,包括高温环境下的物联网应用场景。此外,电路采用简单的电阻修调网络以减小工艺角变化对带隙基准源性能的影响。在1.8 V电源电压下,电路总电流为68.38 μA,芯片核心面积为0.025 mm2,低频时电源抑制比为-48.52 dB。