一种基于FPGA的基-8并行脉压实现方法

2021-07-21王冬华孙雪涛

王冬华 孙雪涛

(中国船舶集团有限公司第八研究院 南京 211153)

0 引言

随着雷达技术的日益发展,雷达已经不仅仅局限于目标探测,还应具备目标一维成像、目标识别等能力[1],而目标识别对雷达发射信号带宽提出较高的要求,发射信号带宽可达几百兆,甚至接近G赫兹,中频信号采样率和数字信号数据率均大大提高[2],这种超大带宽、高数据率和大数据量的基带信号处理在数字下变频时一般采用并行多相滤波结构,通过利用以“面积换速率”的方式降低FPGA的处理时钟[3]。但是这种方式输出的基带信号由多个并行支路组成,其脉压实现方法完全不同于单路信号的脉压[4]。若通过FPGA内部的双口RAM将并行多路基带信号存储下来,再按照支路顺序依次读出并拼接成一路完整的基带信号,最后按照单支路脉压方式实现完整信号的脉压,这种方法严重浪费FPGA的存储资源,且大大增强了FPGA时序设计难度[5],本文利用多相快速傅里叶变换(FFT)和频率抽取的逆傅里叶变换(IFFT),在FPGA中利用频域脉压方法,可以不需要对并行基带信号进行缓存,而实现超大带宽信号的实时脉压处理。

1 并行脉压实现

FPGA中实现脉压主要有以下两种方式[6]:第一种方式为时域卷积,利用Matlab产生脉压系数,并将其导入FPGA提供的FIR的IP核,实现基带信号的脉压功能;第二种方式为频域相乘,利用FPGA提供的FFT的IP核,对输入基带信号进行N点FFT处理,然后与经过N点FFT处理的脉压系数复乘,最后利用FFT的IP核实现N点IFFT处理,从而实现基带信号的脉压功能。

在超大带宽中频接收系统中,为了降低模数变换器(ADC)采样率及FPGA的处理时钟,数字下变频采用多相滤波结构,若采用时域卷积方式需要消耗大量存储资源,且FPGA时序设计和匹配滤波器设计均较为复杂,因此,时域卷积不适合实现超大带宽基带信号的并行脉压[7];频域相乘方式无需额外消耗由于存储每个支路的I/Q信号而造成的BlockRAM资源浪费,并行各支路采用FFT和频率抽取IFFT级联方式,既有利于确保各支路的实时运算,又易与旋转系数实现简单复乘,易于实现并行多路基带信号的脉压功能。

1.1 算法架构

在超宽带数字中频接收系统中,为了降低FPGA的处理时钟,一般采用并行多相滤波算法实现数字正交下变频,从而获得并行多路基带信号[8]。根据信号带宽、前端ADC采样率及FPGA处理时钟,可以确认并行总支路个数D。若信号带宽460MHz,前端ADC采样率为1.6GHz,若FPGA处理时钟为200M时钟,则多相滤波后,将获得并行D=8路基带I、Q信号,8路基带信号同时进行并行多相FFT及频率抽取IFFT处理,实现各支路的脉压功能。其算法架构如图1所示。

图1 并行脉压算法架构

从图1中可以看出,采用并行脉压实现方法可以与多相滤波数字下变频算法结构完全契合,不需要对各支路基带信号进行缓存,有效提高超宽带脉压实现的效率。并行脉压实现方式与传统频域脉压实现方式存在差异,并行脉压实现方式存在各支路间的重新组合,这是并行脉压实现方式的难点。

1.2 基-8多相FFT

设时域信号为x(n),经过多相滤波数字下变频后,获得8路基带信号,各支路基带信号时域表达式如式1所示。

x0(n)=x(8n),x1(n)=x(8n+1),

x2(n)=x(8n+2),x3(n)=x(8n+3),

x4(n)=x(8n+4),x5(n)=x(8n+5),

x6(n)=x(8n+6),x7(n)=x(8n+7)

(1)

其中:n=0,1,2,…,N/8-1。直接调用FPGA内部的FFT核对每个支路进行N/8点FFT运算[9],各个支路时域的FFT结果可表示为

X0(k′)=FFT(x0(n)),X1(k′)=FFT(x1(n)),

X2(k′)=FFT(x2(n)),X3(k′)=FFT(x3(n)),

X4(k′)=FFT(x4(n)),X5(k′)=FFT(x5(n)),

X6(k′)=FFT(x6(n)),X7(k′)=FFT(x7(n))。

(2)

其中:k′=0,1,2,…,N/8-1。各支路并行FFT结果需要重新组合才能获得并行多相FFT结构,首先产生各支路的旋转系数,然后各支路并行FFT结果与对应支路的旋转因子相乘,最后各支路再进行一次8点FFT运算,即可获得并行多相FFT结构。旋转因子如式3所示。

(3)

其中:i=0,1,2,…,7表示第i个支路,j=0,1,2,…,N/8-1表示第j个FFT点数。

1.3 脉压系数复乘

频域脉压实现方式需要与经过FFT处理的脉压系数复乘,并行多相FFT结构对应的脉压系数与传统的单路频域脉压系数生成方式不完全相同。线性调频信号对应的脉压系数仅与信号脉冲宽度、带宽、数据率和脉压点数有关,而上述参数均为固定参数,因此脉压系数不需要实时计算产生,因此可以将生成的脉压系数存放在FPGA内部BlockRAM中[10-11]。与并行多相FFT相匹配的脉压系数生成方式如下步骤:

1)根据信号脉冲宽度、带宽、采样率生成时域I、Q信号;

2)根据脉冲重复周期和数据率,对步骤1)中生成的I、Q信号做N点FFT处理;

3)将N点FFT处理结果等分成8段,分别对应并行8路FFT支路的8路脉压系数。

1.4 基-8频率抽取IFFT

从图1中可以看出,要实现并行多路脉压功能,需要将每路的频域信号转换为时域信号,因此需要对每路与脉压匹配系数复乘结果进行IFFT处理,不同于单支路频域脉压处理方式,在进行并行多路频率抽取IFFT时,每个支路先与其相对应的旋转因子相乘,IFFT过程中旋转因子与式(3)是一对共轭关系,其表达式如式(4)所示。

(4)

其中:i=0,1,2,…,7表示第i个支路;j=0,1,2,…,N/8-1表示第j个FFT点数。

接着各支路再进行一次8点IFFT运算,最后对每个支路进行N/8点IFFT处理,运算结果可以表示为

x0(r)=IFFT(X0(k)),x1(r)=IFFT(X1(k)),

x2(r)=IFFT(X2(k)),x3(r)=IFFT(X3(k))

x4(r)=IFFT(X4(k)),x5(r)=IFFT(X5(k)),

x6(r)=IFFT(X6(k)),x7(r)=IFFT(X7(k))

(k=0,1,…,N/8-1),(r=0,1,…,N/8-1)

(5)

其中:X0(k)…X7(k)表示各支路与旋转因子复乘后并做8点IFFT结果。最终可获得并行8路脉压结果。

2 仿真校验

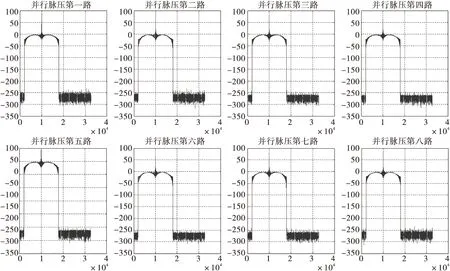

为了进一步说明图1所述并行脉压实现方法,设置仿真参数:脉冲重复周期为300μs,脉冲宽度80μs,零中频信号带宽230MHz,采样率800MHz。全量程I/Q信号采样点数为300μs×800MHz=240000,对于这种大数据量,若在FPGA中采用时域卷积的方法实现脉压,其设计较为复杂,且FIR延时很高;若直接采用频域脉压实现的方式,FFT点数远远超出了FFT的IP核能够支持的最大长度,因此,采用并行脉压实现方法,多相滤波后8路并行的零中频I/Q信号,其时域波形如图2所示。

图2 多相滤波后零中频I/Q波形图

从图2中可知,并行多相单个支路FFT长度减少至原来串行方式的1/8,并且处理延时与运算时间亦缩短至原来的1/8,大大提高处理效率。并行多相实现脉压的过程完全不同于单支路脉压方式,单支路脉压使用频域相乘时不存在并行多路FFT结果之间的重新组合过程,并行多相脉压每个支路在FFT之后,需要与一旋转因子相乘,其表达式如式(3)所示,I/Q波形图如图3所示。

图3 各支路旋转因子I/Q波形图

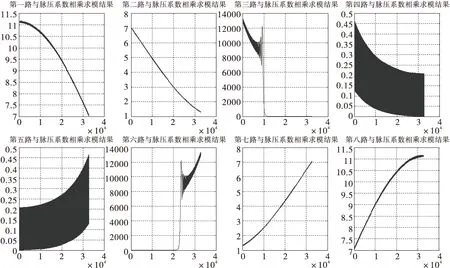

线性调频信号脉压的匹配系数与信号带宽、脉宽、数据率和重复周期有关[12]。并行多相每个支路的脉压系数由串行脉压系数等分得到。仿真中一个重复周期点数为240000,因此串行脉压系数需要做218点FFT,则每个并行支路需要做32768点FFT,如1.3节所述,首先根据信号脉冲宽度、带宽、采样率生成时域I/Q信号,为了提高脉压后主副瓣比,需要进行时域加窗处理,通常选择Hamming窗,然后对加窗后的时域信号进行218点FFT处理,最后将218点FFT结果等分成8路即可获得与每个支路相匹配的脉压系数。并行多相各支路与其脉压匹配系数相乘求模结果如图4所示。

图4 各支路与其匹配系数相乘求模结果示意图

从图1的并行脉压算法架构可以看出,频域到时域的IFFT转换过程与时域到频域的FFT转换过程是一对共轭对称关系,频率抽取IFFT过程各支路每个距离单元先做8点IFFT处理,再与式(5)旋转因子复乘,最后每个支路再进行32768点IFFT处理,即可获得8路并行脉冲压缩结果,其求模结果如图5所示,将各支路信号进行组合即可获得与单支路串行脉压相同的结果。

图5 各支路脉冲压缩求模结果波形图

3 FPGA实现及应用

为了实现对目标的一维距离成像,采用超宽带雷达接收系统,数字收发模块由FPGA电路、ADC电路、DAC电路、时钟电路、电源电路等组成,其中FPGA采用XINLINX公司的kintex-7 系列的xc7v690t,实现并行多相滤波及并行多路实时脉压功能。根据第1节所述并行脉压实现方法,FPGA程序框架由FFT模块、旋转因子生成模块、FFT并行支路合成模块、脉压系数存储模块、IFFT并行支路合成模块、IFFT模块以及时钟延迟模块组成,如图6所示。

图6 FPGA实现并行脉压程序框架图

在XX型雷达上,利用上述方法成功实现了对试验船只的高分辨距离一维成像,试验结果如图7所示,充分验证了该方法的可行性。

图7 试验船只高分辨一维距离成像

4 结束语

在超宽带雷达接收系统中,数字下变频均采用多相滤波结构[13-14],本文提出的方法能够与多相滤波实现流程完美契合,且大大节省了FPGA的存储资源,同时对并行脉压实现流程进行了Matlab仿真,验证了该方法的有效性,最后在XX雷达上,利用FPGA实现了对试验船只的高分辨一维距离成像,进一步验证了该方法的可行性。