卷积编码及Viterbi 译码的低时延FPGA 设计实现

2021-06-30吴倩文高泽峰周志刚

张 健,吴倩文,高泽峰,周志刚

(杭州电子科技大学 电子信息学院,浙江 杭州 310018)

0 引言

近年来,5G 移动通信技术的发展受到人们的广泛关注,高速率、高可靠、低时延的高能效通信成为毫米波通信中的重要因素[1-2]。毫米波频谱宽、频点高的特点对频谱资源紧张的通信系统具有极大的吸引力,并且毫米波频点很高,使得其传输误码率可以达到光纤的误码率量级,能够保证传输的可靠性[3-4]。然而毫米波对环境衰落敏感,传输损耗高使得远距离通信受到限制,为克服这些弱点,高效的信道估计算法成为了关键技术之一,除此之外,常采用信道编码技术来解决接收端出现误码元的情况[5]。常用的信道编码有卷积码、RS 码、Turbo码、交织和伪随机序列扰码等[6-7]。不同类型的纠错码之间有着一定的关联性,如为了克服突发性码元的错误,往往采用卷积码和RS 码相结合的方式来提高通信系统的稳定性[8]。卷积码以其较低的编码复杂度及接近香农限的优秀性能,广泛地应用于卫星通信、无线通信等多种通信系统中[9-10]。Viterbi 译码算法,又被称为最大后验概率方法,是卷积编码最佳的译码算法[11]。卷积编码和Viterbi 译码是广泛使用的信道编码技术,具有一定的克服突发错误的能力,可以减少信道引入的误码,带来较高的编码增益,实现数据的高可靠性传输[12-13]。

在实际通信系统中一般会根据不同的信道特性而采用不同码率的纠错码来进行信道编码,以达到传输效率和传输可靠性之间的平衡[14-15]。根据所需传输速率,本文选择了1/2 码率的(2,1,7)卷积码进行编解码,在选择最小路径中采用流水线形式的32 路比较器并行运行,减少了延时时间,提高了译码速度。

1 毫米波信道编译码

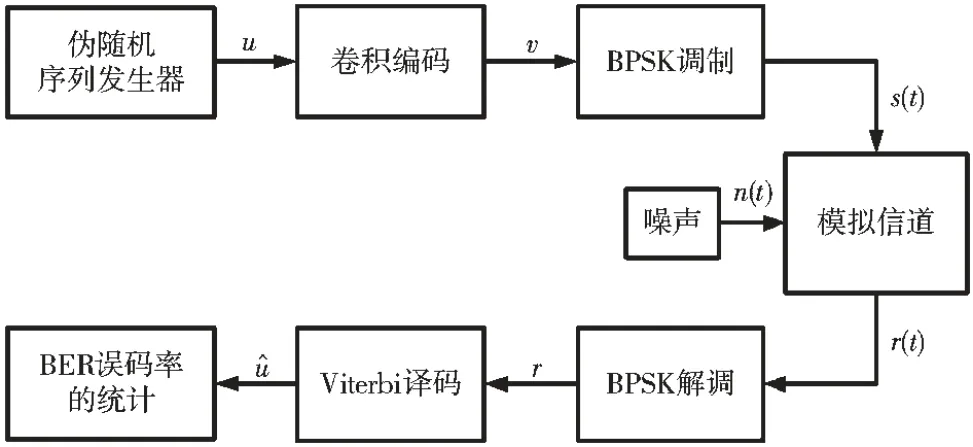

图1 是毫米波通信系统的编译码实现框图。在发送端,随机序列数据源u 经过卷积编码及BPSK 调制后输出s(t),s(t)经过模拟的毫米波通信信道后变为r(t),在接收端,r(t)经解调后由译码器接收,u^即为实际的接收数据,并进行误码率的统计分析。

图1 毫米波通信中的编译码实现框图

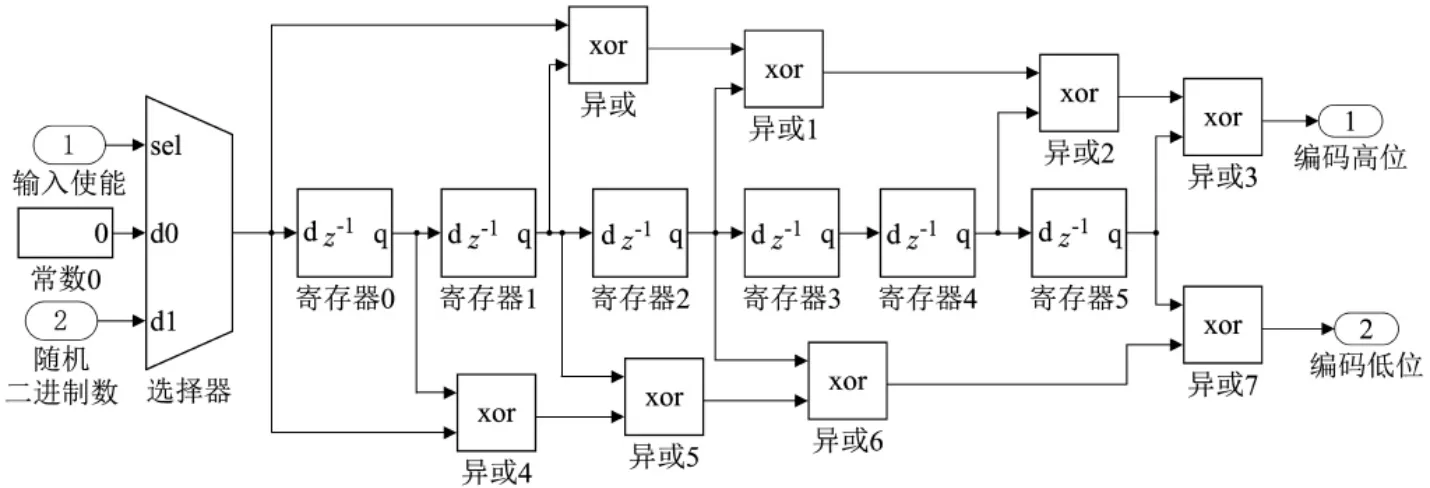

典型的(n,k,m)卷积编码器是指将k 个信息比特编码成n 个比特,其中约束长度为m,编码速率为k/n。本设计选用的(2,1,7)卷积编码器,其生成多项式为g0=1338和g1=1718,码率为1/2。如图2 所示,每1 比特数据经过6 个移位寄存器和模二加法器后生成并行的数据,再经过并串转换进入QPSK 调制、信道、QPSK 解调及串并转换进入译码器。

图2 (2,1,7)卷积编码模块图

2 卷积码低时延译码设计

本设计中选定译码器的译码深度L=36,译码器存储器的最小容量应该满足64×L 个路径节点及其路径的长度。译码器的设计包括汉明距离计算模块、ACS 加比选模块、路径存储模块、最小值选择模块、路径回溯模块及控制模块等。

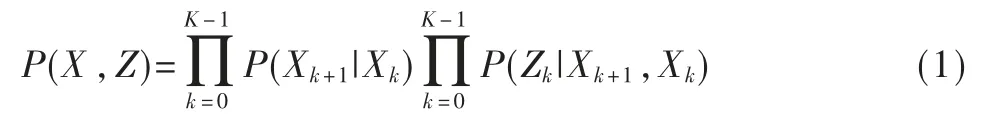

译码器设计的关键在于如何选择概率最大的路径,这里定义路径长度为-lnP(X,Z),其中X 为与该路径所对应的状态序列,Z 为所接收的序列,最终是要寻找P(X,Z)的最大化后验概率。所谓“后验”,是指根据接收到的编码数据,推测出各个移位寄存器所对应的状态,找出所有路径中最有可能的一条[16]。根据定义,等价于求-lnP(X,Z)的最小路径,公式如下:

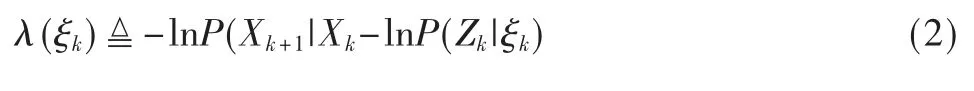

定义路径分支长度为λ(ξk),表达式为:

其中ξk是Xk到Xk+1状态的转换,总体的路径长度表达式如下:

因此任意时刻的各分支路径和的最小路径就是当前时刻的最短路径,又称幸存路径。

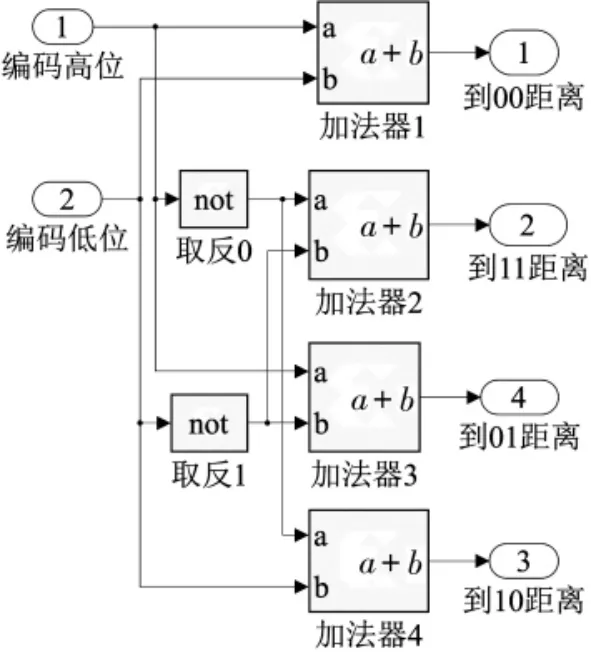

汉明距离计算主要负责计算编码后的状态与当前编码器状态下可能的编码之间的汉明距离值。为简化设计,直接求出输入数据与4 个固定编码状态(00,01,10,11)之间的距离,如图3 所示。

图3 汉明距离计算模块

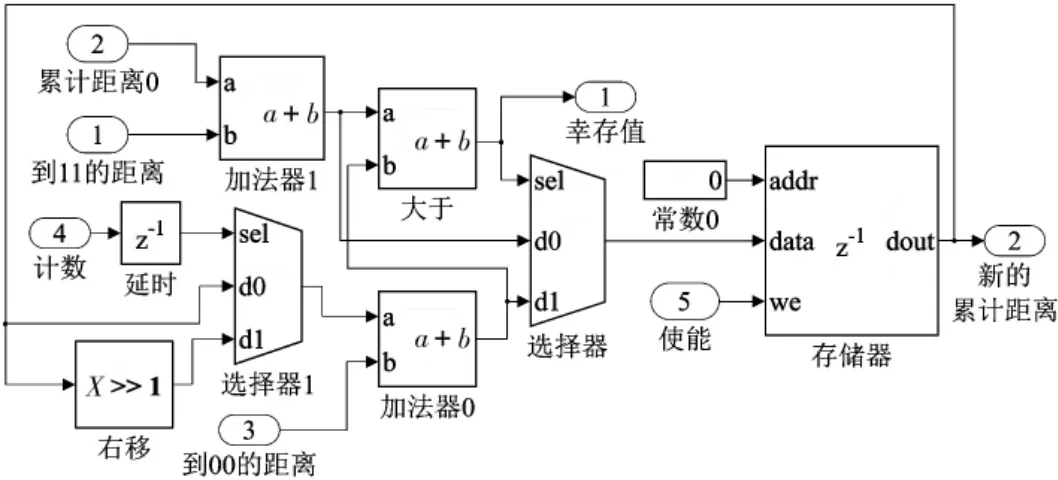

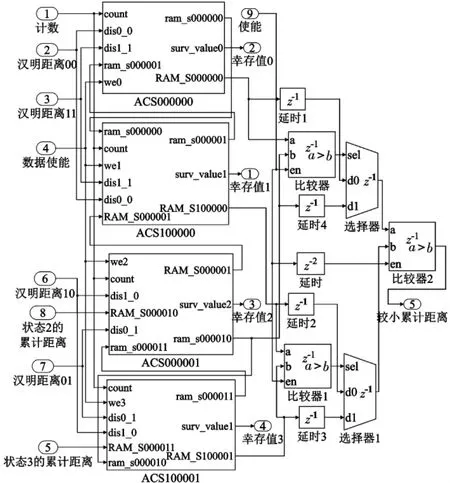

ACS 模块用来计算当前状态的分支路径距离和前一时刻的累计距离累加,比较、选择并保存为新的累计距离,并将新的累计距离存储在RAM 里,为回溯模块做准备。图4所示是一个ACS 模块的蝶形运算,采用全并行的算法需要64 个ACS模块,即在一个时钟周期内完成所有状态的分支路径距离的更新迭代,其中为防止累计距离溢出,把每个状态的累计距离右移一位。

图4 ACS 加-比-选模块

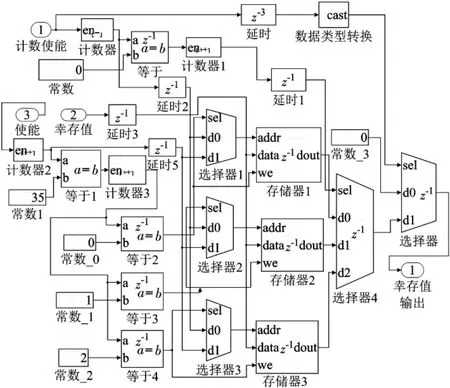

路径存储用来存放幸存路径值,此模块采用乒乓操作,这种方式提高了译码器的译码效率。具体原理如图5所示,通过控制信号来控制三块RAM 的轮流工作,在译码开始,回溯还未开始之前,先向一块RAM 中写入数据,存储幸存路径;当回溯开始之后,需要从另一块RAM中读取路径信息,由于不能同时轮流使用两块RAM,需要第三块RAM 提供新的写操作,用计数器控制三块RAM的工作过程。

图5 路径存储模块

最小值选择根据ACS 模块得到64 条累计距离来确定到达译码深度时的最小路径值和最后一个状态。如图6所示,本设计中选用32 路比较器并行运行,64 条路径两两进行比较,只需要6 个时钟周期就能完成比较,相比802.11a 标准中规定的路径比较降低了17 个时钟周期的时延。按照一定的顺序选择较小累计距离,每次选择的结果决定着最后的状态。

图6 最小值选择模块

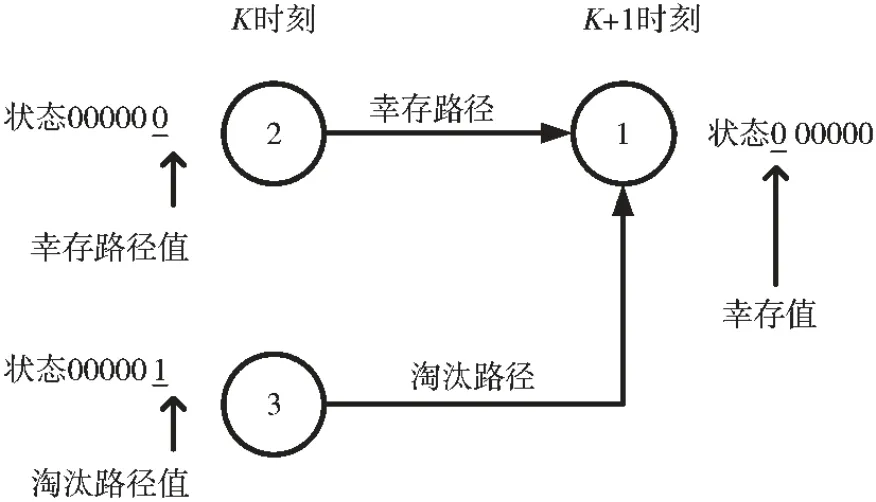

路径回溯是由最小路径的最后一个状态值和存储的幸存路径值来确定回溯点的。如图7 所示,到达K+1时刻的状态只有两种,状态的不同只有最低位不同,最低位代表着K-5 时刻输入编码器的值,K+1 时刻的最高位代表该时刻进入编码器的值,也是幸存值。两条路径中较小的一条存为幸存路径值,所以可将最后态的低五位作为高位,幸存值作为最低位,形成选择最后状态的判决条件,然后进行回溯。利用回溯计数器计时,直到到达译码深度,回溯完毕,即可找到完整的路径信息,再经过反序就是译码结果。

图7 路径回溯说明图

3 实现验证

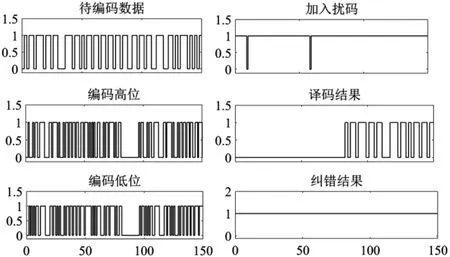

从图8 可以看出,输入一定的比特序列进入编码器,编码后翻转其中的几个码元,形成误码送入到译码器,测试结果表明,译码器实现了预期的纠错功能。

图8 编译码仿真图

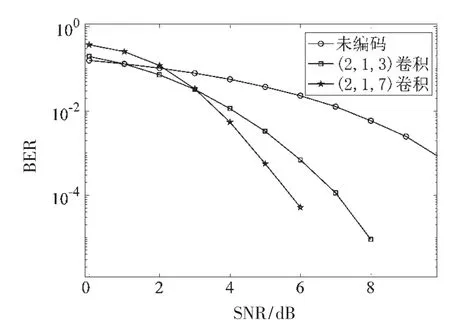

对于码率一定的卷积码,其约束长度一般为3~9。从图9 中可以看出,当信噪比大于约2 dB 时,编码后的性能比未编码性能要好,信噪比大于3 dB 左右时,随着约束长度一定的增加,系统的误码率明显降低。

图9 卷积编译码的误码率仿真图

Vivado 布局布线后的仿真结果如图10 所示,其中clk 为125.6 MHz 的工作时钟,data_in 为输入的伪随机二进制序列,i_en 为数据有效信号,encode 为编码后的数据,state 为每次到达译码深度后的最后一个状态,viterbi_o 为译码后的数据。由图中的输入数据与译码数据对比,显示编译码后的数据是一致的,仿真结果证明该译码模块可行。另外,该设计中的译码器的数据传输速率可达到1 256 Mb/s,想要获得更高的数据传输速率可以选择更多的数据位宽进行多路并行输入,这样数据传输速率可以成倍地提高。对于时延,该译码器利用更多的选择器进行比较,大大减少了时延,经计算译码输出总共延迟约708 ns 的时延。

图10 Viterbi 译码器仿真结果

4 结论

本设计利用毫米波通信系统来实现数据的短距离保密通信,完成全并行处理的(2,1,7)卷积编译器,该编译码器性能优异,在一定程度上加强了毫米波通信的抗干扰能力。另外,通信系统中利用system generator 平台实现对各个模块的功能及性能的仿真测试。后来经Xilinx 公司的Vivado2019.1 平台进行综合验证,反复实验表明,该卷积码具有前向纠错能力强、编译码速度快、时延较小等特点,其译码速度达到了预期设计目标。