双向多路快跳频载波发生器的设计与实现

2021-02-24陈雷王涛韦靖田晓燕张锁良

陈雷,王涛,韦靖,田晓燕,张锁良

(1.河北大学 电子信息工程学院,河北 保定 071002; 2.北京邮电大学 电子工程学院,北京 100876)

跳频分为快跳频和慢跳频2种,慢跳频是指跳频频率低于信元码率,即持续传输几个比特的信息跳频一次;快跳频是指一次发射信号期间有多次频率跳变,即跳频频率高于信元码率[1].跳速越快,抗跟踪和干扰的能力就越强.

在近几年的研究中,文献[2]提出了一种使用非均匀正弦加权数模转换器的低功耗直接频率合成器DDS技术,降低了信号杂散和系统功耗,可以输出不同频率的信号,但输出频率有限,信号带宽较窄.文献[3]提出一种多路并行DDS技术,可以产生大带宽信号,频率分辨率高,且频率转换速度快,但没有考虑对系统硬件资源消耗的问题,实际应用存在一定的局限性.文献[4]提出一种基于坐标旋转数字算法(CORDIC)的DDS技术,利用CORDIC算法替代了ROM查找表,降低了相位截断误差和幅度量化误差,提高了信号的频谱纯度,但算法迭代数较多,计算复杂,信号延迟较高.

针对以上问题,本文提出一种双向多路快跳频载波产生方法,通过并行设计实现了大带宽快速跳频,利用双向跳频算法将原本的跳频带宽一分为二,以中频载波频率为中心向正负2个方向跳变.保证了跳频载波质量,同时降低了硬件资源消耗.结果表明,利用该方法,在系统信元码率为10 kHz、扩频速率10 MHz的前提下,产生了跳频速率20 000 hops/s、跳频带宽327.52 MHz的快跳频载波.相比于单向跳频,在产生载波质量相同的条件下,节约了系统53%的Block RAM资源.

1 系统结构

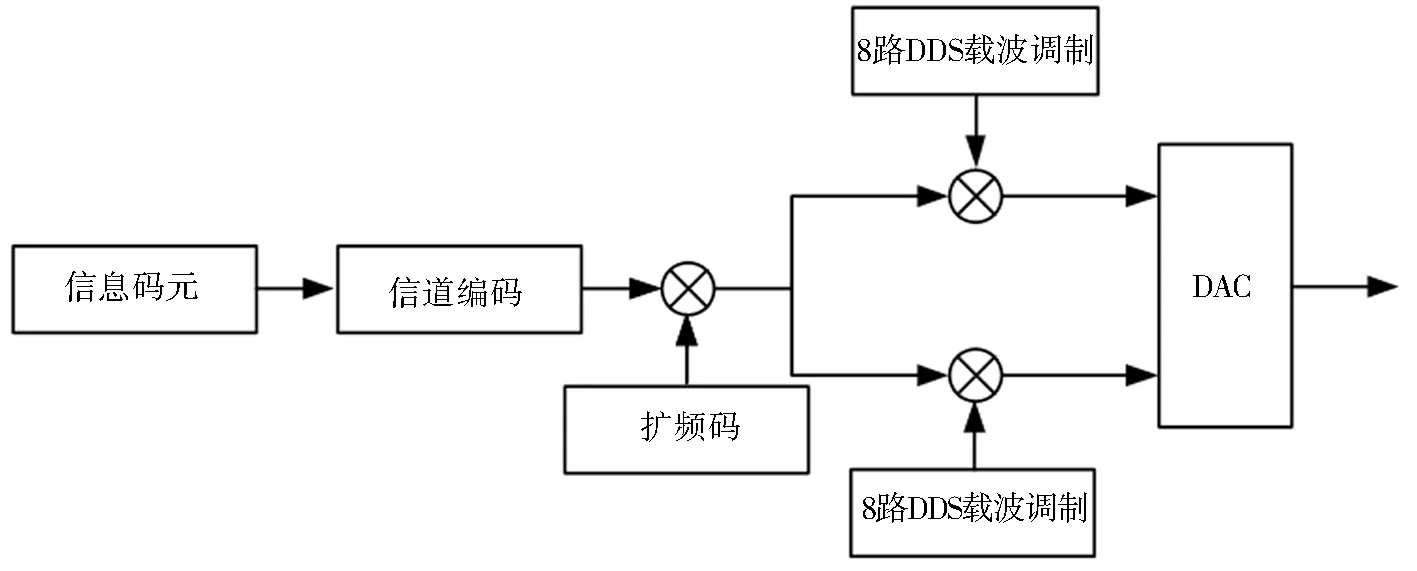

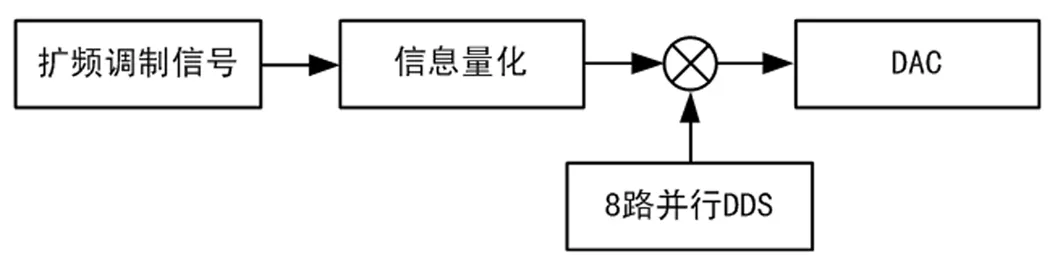

本系统中,信息码元首先完成信道编码,随后利用伪随机序列作为扩频码进行扩频调制,再利用多路并行DDS产生的本地载波完成BPSK调制,最后调制信号进入DAC中进行720 MHz中频调制.系统整体结构如图1所示.

图1 快速跳扩频系统发射端结构Fig.1 Transmitting structure of fast DS/FH system

2 设计原理

2.1 多路并行DDS设计原理

工程设计中DDS通常以串行的形式出现[5].根据奈奎斯特采样定理可知,单路串行DDS的输出频率会受到时钟频率限制,最高输出频率为时钟频率的一半[6].本设计中,时钟板卡提供给现场可编程门阵列(FPGA)的时钟频率为80 MHz,理论上DDS能够输出的最大频率为40 MHz,但是在实际工程中认为它只能达到系统时钟的40%左右[7].由于FPGA时钟频率有限且提升空间很小,串行DDS不能满足系统327.52 MHz跳频带宽的要求,需采用并行DDS设计.

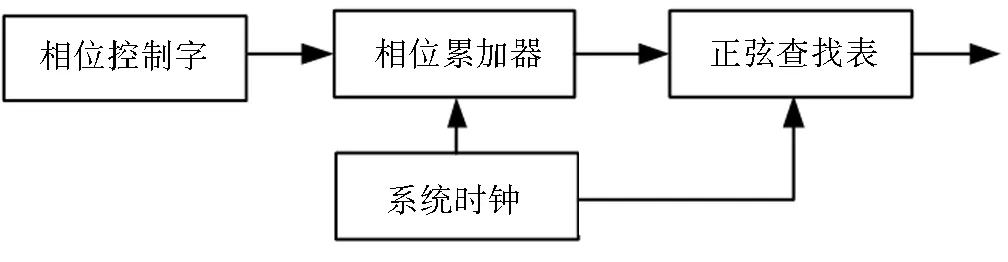

图2所示为传统单路DDS结构,通过对相位控制字进行线性累加,累加结果经过正弦查找表进行相幅转换,形成数字形式的正弦波.

多路并行DDS的每一路也同样基于单路串行DDS的设计原理,只是在每一路相位累加间隔相同的条件下,其初相是不同的[8].图3所示为8路并行DDS结构,利用寻址多相的结构对各路初始相位控制字Ki进行累加,其中i=0,1,2,3,…,7,每路对应的初始相位Ki为相位累加间隔d的i倍.而各路相位累加器的累加值与并行DDS的路数成正比,若系统n路并行DDS的相位累加间隔为d,则各路的相位累加器中的累加值为nd.各路初始相位控制字在经过相位累加之后,累加的结果通过正弦查找表进行相幅转换,将原本串行的数字载波以并行的形式输出. 采用n路并行,可将DDS的频率输出范围提高n倍,满足系统设计需要.

图2 单路串行DDS结构Fig.2 Structure diagram of single-channel serial DDS

图3 多路并行DDS结构Fig.3 Structure diagram of multi-channel parallel DDS

快跳频载波的产生需要利用并行DDS输出不同频率的载波,不同的频率对应着不同的相位累加间隔d,对于一个深度为N的正弦查找表,目标输出频率为fo,系统时钟频率为fclk,则需要的相位累加间隔计算公式为

(1)

2.2 跳扩频调制原理

对于混合跳扩频通信系统而言,在进行跳频调制之前需要对信号进行扩频调制,用来扩宽信号带宽,降低接收端对信噪比的要求[9].本系统使用直接序列扩频的方法进行调制,扩频序列采用伪随机序列产生的伪随机码[10].伪随机码具有很强的相关性,有利于系统接收端对信息的捕获跟踪.

系统信息码元速率为10 kHz,采用卷积+RS级联码的形式编码,编码后速率为20 kHz,扩频码的速率为10 MHz.设信息码元速率为Rc,扩频码速率为Rm,则对应的信息码元宽度Tc和扩频码宽度Tm可表示为

(2)

(3)

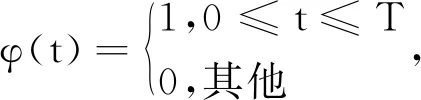

从而可得到信息码元C(t)和扩频码M(t)表达式为

(4)

(5)

(6)

其中,cn与mn分别为信息码序列和扩频码序列.将上述信息码与扩频码相乘,可得到扩频调制信号D(t),即

(7)

考虑到接收端跳频载波的同步问题,在产生跳频载波时需要保证载波相位连续,减小信息传递过程中产生的误差.本设计中的跳频信号F(t)共有2 048个跳频点,跳频带宽327.52 MHz,频率间隔为160 kHz,起始点频率为80 kHz.其中,频率间隔和起始点频率均与跳频速率呈倍数关系,可以保证产生的跳频载波相位连续,其表达式为

(8)

其中,fn为F(t)中的跳频点集,对应的跳频调制为固定频点循环,不同的跳频点对应着不同的相位控制字[11],更新频率为20 kHz,可以产生跳速为20 kHz的跳频载波.

由于硬件资源有限,为了保证信号增益和幅度不受影响,需要对D(t)进行量化,量化后得到信号

L(t)=A×D(t),

(9)

其中A为量化参数.

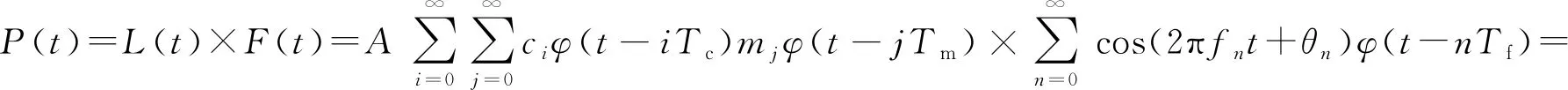

将量化后的信号与跳频信号F(t)相乘,完成BPSK调制,得到发射端调制信号为

(10)

其中ωt和θt是时域上当前时间的载波频率和相位.

2.3 双向跳频信号设计原理

寻址多相结构的DDS是基于正弦查找表实现的.在一定跳频带宽下,随着跳频频率逐渐升高,相位地址的间隔也会变大.在正弦查找表位宽和深度相同的表情况下,产生的数字跳频载波的相位截断误差会上升,系统性能也会受到影响.加深正弦查找表的位宽和深度可以降低相位截断误差,但是会占用更多的硬件资源.针对此问题,以中频频率为中心,产生双向跳频频点,可以保证跳频带宽不变,使跳频载波的最高频率降低一半,从而降低了对正弦查找表位宽和深度的要求,节省硬件资源.系统需求跳频带宽为327.52 MHz,采用双向跳频将中心频点搬移到720 MHz,向720 MHz±163.76 MHz 2个频率方向跳变,跳频带宽不变,DDS最高频率需求由327.52 MHz降为163.76 MHz.

系统设计中,载波调制分别利用余弦和正弦函数产生I、Q 2路信号,每路信号由8路并行DDS产生,调制过后的信号以并行的形式进入DAC进行720 MHz中频调制,2路相加后进行数模转换送入射频模块.

信号P(t)分为I、Q 2路进入DAC,2路数据分别进行中频正余弦载波调制.设I、Q 2路载波频率为ωx,相位为θx,中频载波频率为ωy,相位为θy,可以得到2路中频调制后的信号

TXI(t)=D(t)cos(ωxt+θx)cos(ωyt+θy) ,

(11)

TXQ(t)=D(t)sin(ωxt+θx)sin(ωyt+θy) ,

(12)

相加后得

TX(t)=TXI(t)+TXQ(t)=D(t)cos(ωxt+θx)cos(ωyt+θy)+D(t)sin(ωxt+θx)sin(ωyt+θy)=

D(t)cos((ωy-ωx)t+(θy-θx)),

(13)

即可以得到ωy与ωx频率之差.

若将Q路的数据取反后输入DAC,相加后得到

TX(t)=TXI(t)-TXQ(t)=D(t)cos(ωxt+θx)cos(ωyt+θy)-D(t)sin(ωxt+θx)sin(ωyt+θy)-

D(t)cos((ωy+ωx)t+(θx+θy)).

(14)

即可以得到ωy与ωx频率之和.

综上所述,利用DAC的功能,可以在FPGA中通过调整不同跳频点Q路的极性,实现以中频调制信号频率为中心,左右跳变的双向跳频信号,达到系统设计要求[12].

3 设计方案实现

通信系统的设计在确保稳定性的同时,运算速度也要有保障.FPGA在硬件上可以达到此要求,并且具有软件可编辑的功能,能很好地适应不同系统的要求,为系统测试提供了便捷的功能,具有很强的灵活性. 本设计采用Xilinx公司的Zynq-XC7Z100系列FPGA芯片,在ISE14.7软件环境中进行逻辑编辑,同时利用高性能的16位数模转换DAC9164芯片进行中频调制和数模转换.

信道编码采用卷积+RS级联码形式,利用ISE14.7环境下的独立IP核实现.扩频调制利用频率10 MHz、周期500码片的扩频码与编码后频率20 kHz的信息进行异或运算实现,扩频码频率与信息频率的比为500∶1.

图4 基带信号处理结构Fig.4 Structure diagram of baseband signal processing

在跳频调制前,为了保证信号增益和幅度不受影响,需要对扩频调制后的信号进行高电平为“+1”、低电平为“-1”的量化处理,再利用跳频载波对其进行BPSK调制.具体实现是利用DDS产生的数据与量化后的信号进行相乘运算.其实现方式图4所示.

并行DDS利用只读存储器ROM来实现,首先需要在MATLAB软件中产生需要的N个采样点M位宽的正弦余弦数据,然后生成内存初始化文件 (memory initialization file,MIF),将其导入ROM中作为基本载波样本,将此作为基础载波,通过相位控制字,对ROM中的数据进行寻址读取,实现并行DDS.

4 结 果

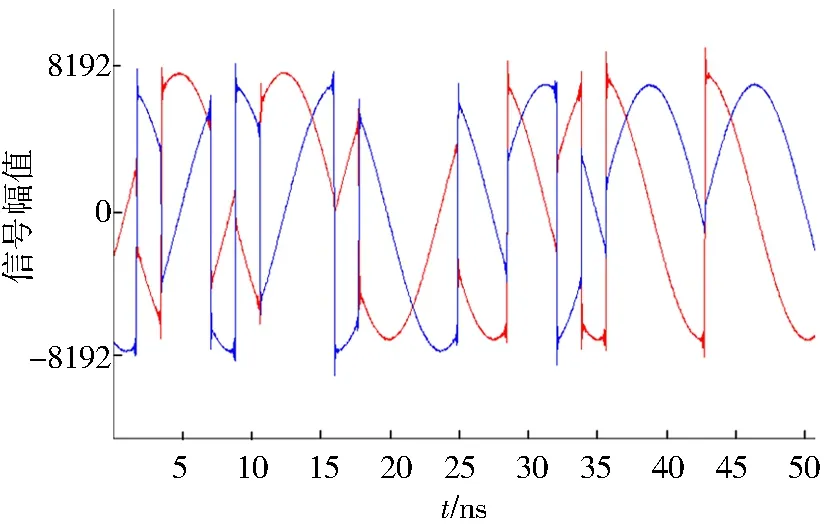

跳频载波利用Modelsim工具进行仿真,采用位宽16、深度215的ROM作为正弦查找表,图5为并行DDS产生72 MHz载波的仿真波形.

图5 72 MHz信号Modelsim仿真Fig.5 Simulation diagram of 72 MHz signal Modelsim

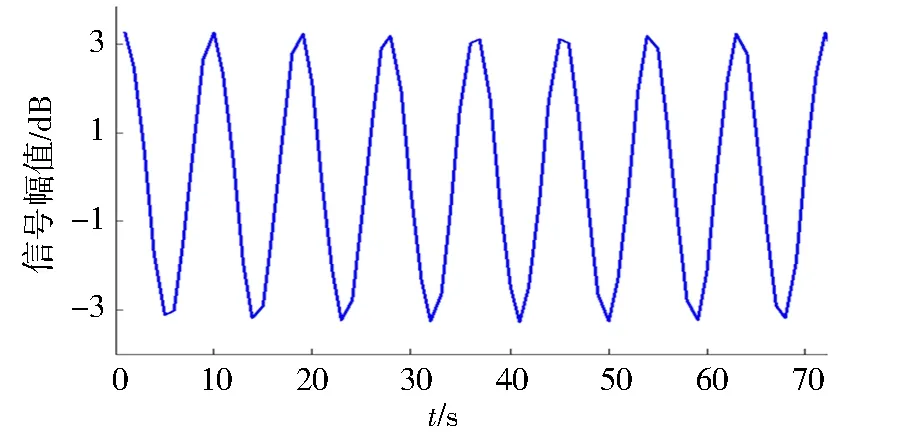

信号clk为系统时钟,周期12 500 ps,频率80 MHz;信号dds_out0~dds_out7为DDS的8路并行输出.利用MATLAB工具将8路输出信号以串行的方式依次排列后得到的结果如图6所示.可以看出,并行数据以串行的方式排列后,形成了周期性载波,8路并行DDS成功产生72 MHz载波.

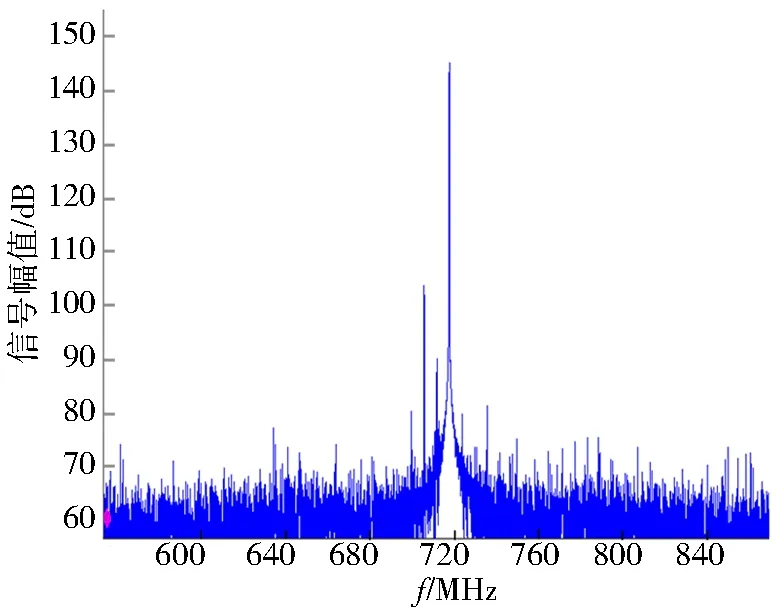

图7、图8所示为本设计通过上位机界面观察到的频谱图和输出信号图.可以看出,在上行设备没有任何调制信号输出时,只有DAC产生的720 MHz中频信号.

图6 MATLAB串行处理波形Fig.6 MATLAB serial processing waveform

图7 720 MHz单载波输出信号频谱Fig.7 Frequency domain diagram of 720 MHz single carrier output signal

图8 720 MHz单载波输出信号Fig.8 Time domain diagram of 720 MHz single carrier output signal

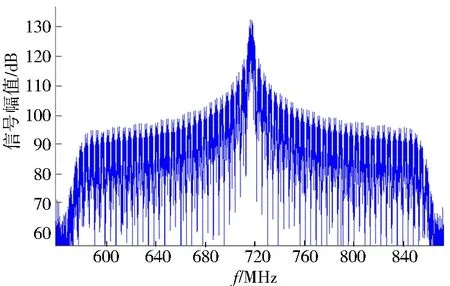

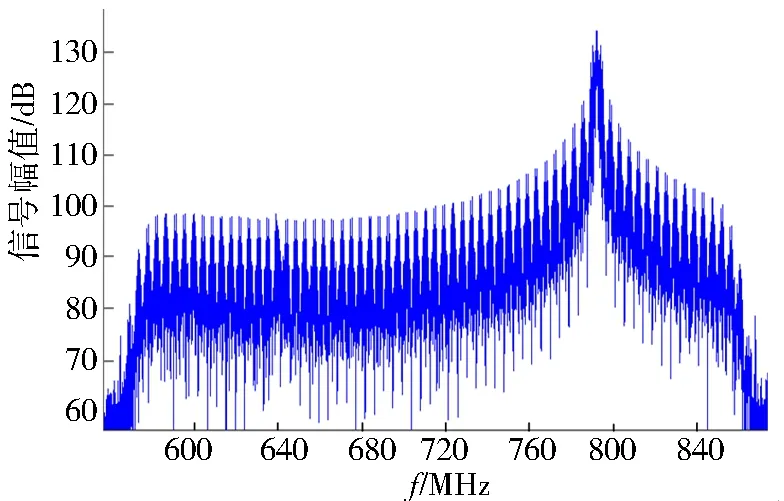

图9、图10所示为信息码元经过扩频调制、DAC的中频调制之后的频谱图与输出信号图.可以看到,以720 MHz为中心频率的输出信号的频谱被扩展.

图9 扩频后输出信号频谱Fig.9 Frequency domain diagram of outputsignal after spreading

图10 扩频后输出信号Fig.10 Time domain diagram of outputsignal after spreading

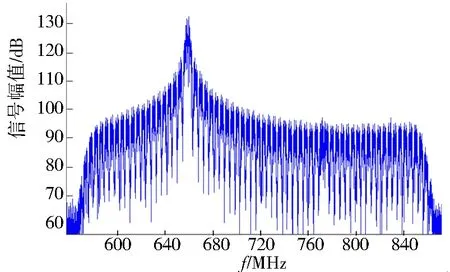

通过不同的跳频点可以产生双向跳频,图11为正向跳频72 MHz的频谱图,图12为反向跳频57 MHz的频谱图.可以看出,输出信号的中心频点随着跳频调制向正、负方向搬移.

图11 正向频率跳频输出信号频谱Fig.11 Frequency domain diagram of positivefrequency hopping output signal

图12 反向频率跳频输出信号频谱Fig.12 Frequency domain diagram of negativefrequency hopping output signal

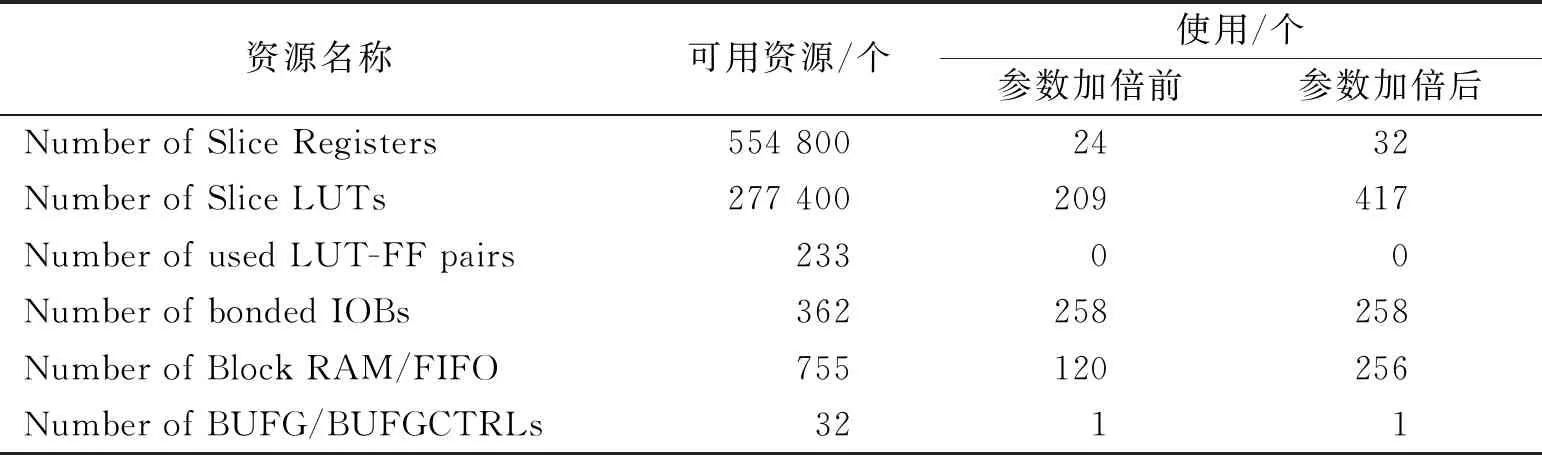

如果使用单向跳频产生同质量载波,为保证载波质量,需要将正弦查找表的位宽和深度增加1倍以上.以本次实验参数为基础,将ROM的位宽和深度增加1倍,经过仿真后得到表1所示的资源消耗对比.表1数据可以得出,相比于参数加倍后产生的单向跳频,在双向跳频的设计中主要存储模块Block RAM/FIFO的资源降低了53%.

表1 资源消耗对比

5 结 论

本文提出一种双向多路快跳频载波产生技术,基于FPGA平台,在系统信元码率10 kHz、扩频速率10 MHz的前提下,通过多路并行DDS技术产生了跳速为20 000 hops/s、跳频带宽为327.52 MHz的快跳频载波,利用双向跳频的设计思路,在确保带宽不变的情况下,进一步节省了硬件资源的消耗.相比于单向跳频,节约了系统53%的Block RAM资源,具有更高的实际应用价值.本文暂未对此方法中的幅度量化误差进行分析,下一步将建立幅度量化误差模型,展开进一步的研究.