基于双绞线型四层PCB罗氏线圈的碳化硅器件开关电流测量

2021-02-22许震明磊石亚飞辛振卢保聪

许震, 明磊, 石亚飞, 辛振, 卢保聪

(1.河北工业大学 省部共建电工装备可靠性与智能化国家重点实验室,天津 300130;2.香港中文大学 电能变换实验室,香港 999077)

0 引 言

在电力电子系统中,功率器件的开关电流信息在开关特性评估、器件保护、结温提取、寿命预测以及系统状态监测等场合必不可少[1-2]。与传统硅基器件相比,碳化硅(silicon carbide,SiC)器件具有更高的耐压、更快的开关速度和更低的损耗,可有效提升系统功率密度,因此正在稳步地进行市场替代[3-4]。然而,SiC器件更快的开关速度造成了较高的di/dt和dv/dt,也使其对电路中寄生参数更加敏感。因此,相应的电流传感器需同时具备高带宽、强抗扰、低侵扰和小体积等特性。

用于器件开关特性测试的同轴分流器具有极低的插入电感(<10 nH)和极高的带宽(>1 GHz),但其体积较大且非隔离[5-6],因此不适合集成于实际产品。霍尔电流传感器虽然具备隔离特性,但其带宽通常低于300 kHz,难以用于开关电流的测量[7-8]。作为霍尔传感器与变压器的组合,电流互感器显著提升了带宽,但其较大的体积降低了系统的功率密度[9]。此外,磁芯引入的寄生电感恶化了SiC的开关性能[10]。罗氏线圈电流传感器由于采用空心线圈,具备天然的高带宽和低侵扰特性[11-13]。此外,通过采用印制电路板(printed circuit board, PCB)设计,可进一步减小体积[14]。因此,PCB罗氏线圈电流传感器在开关电流测量中具有较大潜力,近年来引起了业内的广泛关注。

文献[15]报道了一种两层PCB罗氏线圈用于检测SiC MOSFET的开关电流。然而,由于缺乏回线和屏蔽层设计,其电流测量受到邻近载流体产生的磁场噪声以及邻近开关产生的电压噪声的严重干扰。文献[16]报道了一种四层PCB罗氏线圈,其中间层采用单回线设计可有效抵御邻近载流体产生的磁场噪声,但由于缺乏屏蔽层设计,其仍受到邻近电场噪声的影响。为同时抵御磁场与电场干扰,文献[17]在文献[16]的基础上额外增加了屏蔽接地层。这种六层PCB罗氏线圈虽能增强抗扰性能,但其额外的层间电容(屏蔽层与中间线圈的寄生电容)会降低带宽。此外,六层PCB设计也会显著增加系统成本。从性能与成本角度考虑,四层PCB罗氏线圈在SiC器件的开关电流测量中具有较大潜力。然而目前尚未有能同时抵御电、磁干扰的四层PCB线圈。

为此,本文首先分析罗氏线圈中回线和屏蔽层抵御磁场和电场干扰的机制。然后,对三种典型PCB罗氏线圈的抗扰性能进行对比分析。基于此,本文提出一种双绞线型四层PCB罗氏线圈。通过在中间层采用双绞线设计,使其具备“隐形回线”结构;通过在最外层增加屏蔽,可有效抵御电场干扰。仿真和实验表明,所提方案兼具强抗扰和高带宽特性,适合用于碳化硅器件的开关电流测量。

1 碳化硅器件开关电流测量

1.1 碳化硅器件开关电流测量的要求

图1所示为SiC MOSFET的物理、电气特性[18]及其对开关电流测量的要求。

图1 SiC MOSFET的特性及其对开关电流测量的要求Fig.1 Characteristics of SiC MOSFET and its requirements for switch current measurement

由图1可知,适用于SiC MOSFET开关电流测量的传感器需同时满足以下4个要求:

1)高带宽。电流传感器的所需带宽BW[5]可表示为

BW=0.35/tr。

(1)

式中tr为电流上升时间[5]。以Wolfspeed公司的C2M0080120D为例,其tr=20 ns[5]。由式(1)可求出所需电流传感器的最低带宽为17.5 MHz。为保证测量精确度,实际带宽一般选取该值的3~5倍。

2)强抗扰。一方面,SiC MOSFET开关过程产生的dv/dt会通过容性耦合传导至测量系统(即电场干扰);另一方面,邻近载流体会通过耦合磁场对测量造成干扰[19]。

3)低侵扰。SiC MOSFET开关时间在数十ns之内,因此,具有较高di/dt。由Ldi/dt可知,寄生电感(电路走线及由于测量引入的电感)会引起较高的电压尖峰和振荡,增加损耗,甚至造成器件过压损坏[20]。

4)小体积。SiC MOSFET开关频率高,可显著减小无源器件的尺寸。为实现高功率密度的电力电子装置[21],电流传感器需具有较小体积。

1.2 基于PCB罗氏线圈碳化硅器件开关电流测量

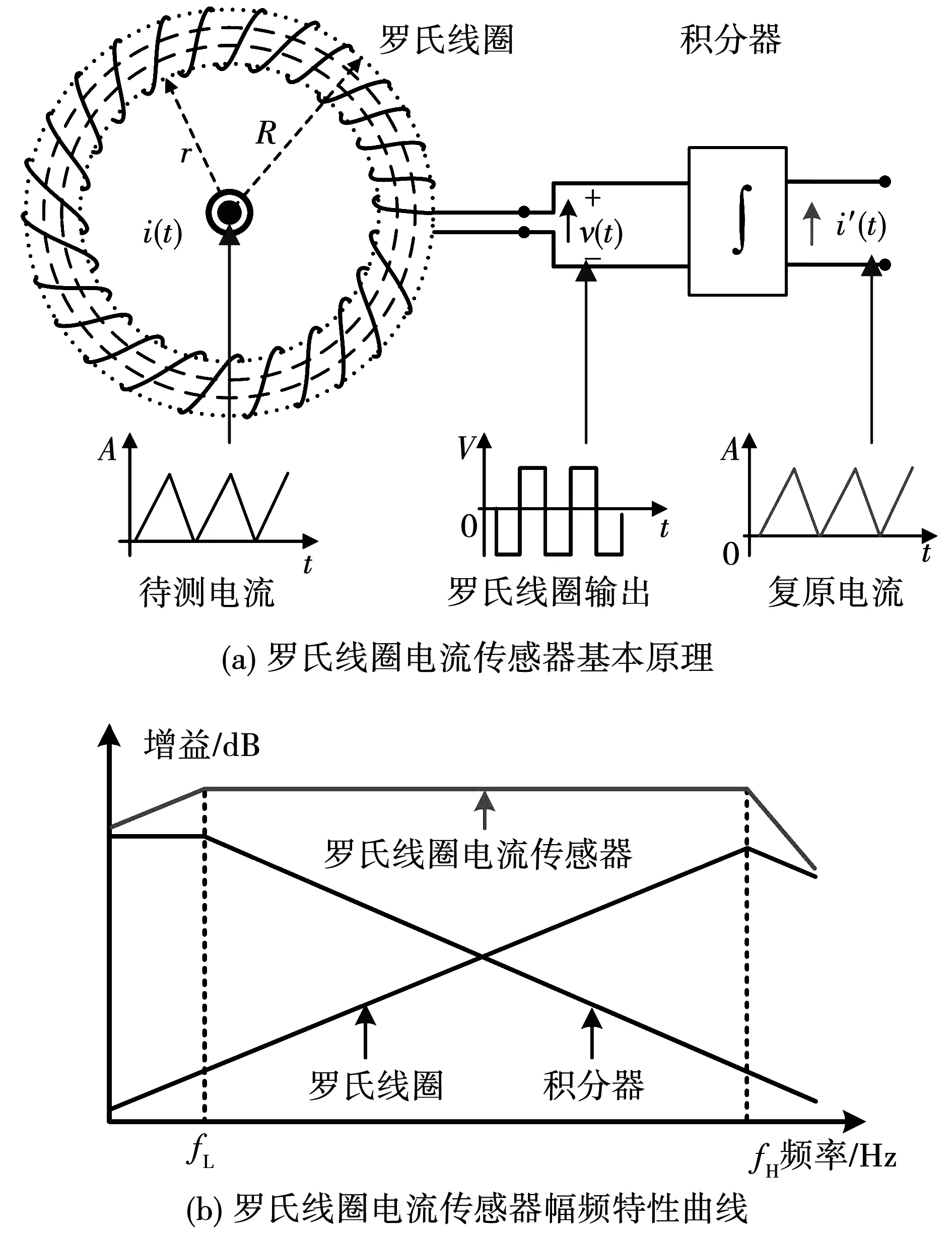

罗氏线圈电流传感器包括罗氏线圈和积分器两部分。如图2(a)所示,待测电流i(t)置于罗氏线圈中心位置处,根据法拉第电磁感应定律,i(t)产生的磁场与罗氏线圈交链,可在其端口处得到感应电压v(t),经过积分后即可得到复原电流i′(t)。罗氏线圈电流传感器的幅频特性曲线如图2(b)所示,其中fL和fH分别为传感器的低频和高频截止频率。从图中可以看出,传感器的低频特性主要取决于积分器,而高频特性主要受限于罗氏线圈。积分器主要分为无源积分和有源积分[5],目前已有很多成熟方案可借鉴,不再赘述。为测量SiC MOSFET的开关电流,需提高传感器的高频带宽。因此,本文主要围绕罗氏线圈展开讨论。

图2 罗氏线圈电流传感器基本原理及其幅频特性曲线Fig.2 Principle of Rogowski current sensor and its amplitude-frequency characteristic curve

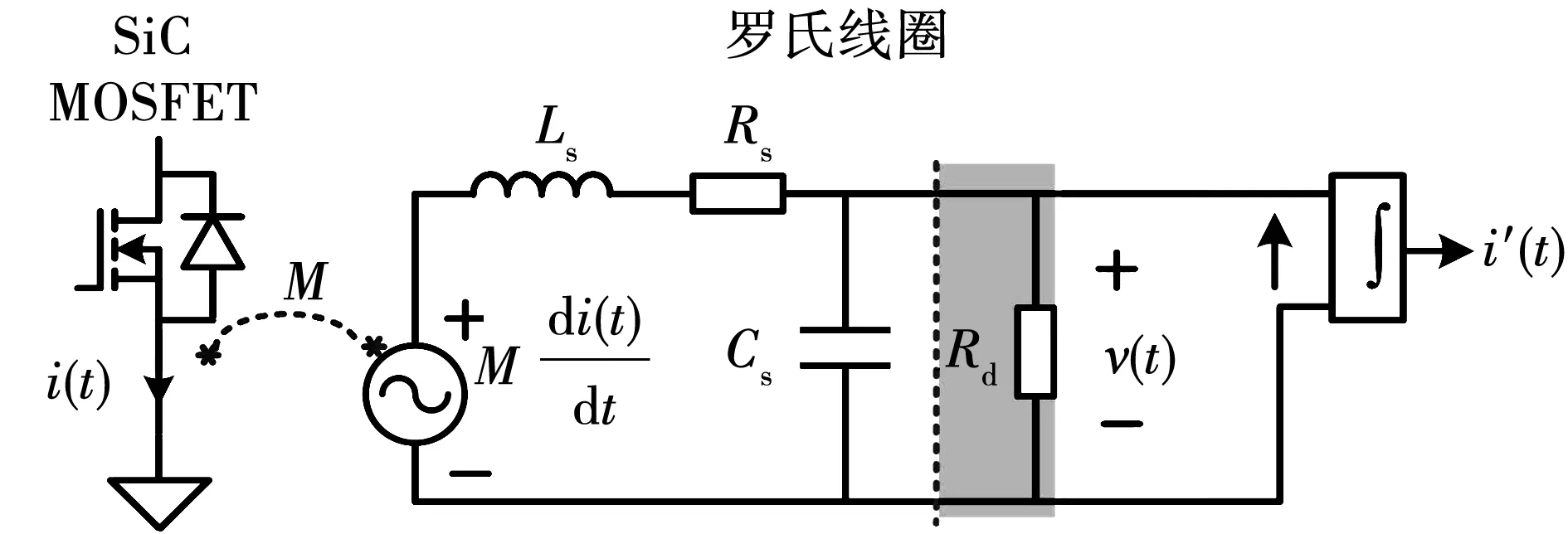

罗氏线圈采用空心线圈,具备天然的高带宽和低侵扰特性。此外,通过采用PCB设计,可进一步减小体积。因此,PCB罗氏线圈在SiC MOSFET的开关电流测量中具有较大潜力。图3所示为PCB罗氏线圈的集总参数模型。

图3 PCB罗氏线圈应用于SiC MOSFET开关电流测量Fig.3 Switch current measurement of SiC MOSFET based on PCB Rogowski current sensor

在图3所示的模型中:Ls为线圈自感;Cs为寄生电容;Rs是寄生电阻;M为线圈互感;Rd是阻尼电阻。依据模型,待测电流i(t)至感应电压v(t)的传递函数可以表示为

(2)

根据式(2),可以算出罗氏线圈的高频带宽为

(3)

在式(2)及式(3)中Ls,Cs和M[5]分别为:

(4)

式中:R为线圈外径;r为线圈内径;h为中间层线圈高度;l为线圈布线的总长度;a为导线截面积;A为线圈截面积;εr为相对介电常数;ε0为真空介电常数。

由式(3)和式(4)可知,罗氏线圈的电参数(Ls和Cs)由其物理参数决定,可以通过减小罗氏线圈的尺寸、匝数或调整其结构的方式提高带宽。除带宽外,SiC器件开关过程产生的电场和磁场干扰也影响了线圈测量开关电流的精确度。下文将分析罗氏线圈的抗扰机制并讨论现存方案的抗扰性能。

2 PCB罗氏线圈抗扰性能分析

2.1 罗氏线圈抗扰原理分析

在SiC器件的开关电流测量中,PCB罗氏线圈电流传感器受到的干扰可分为两类:1)器件开关过程中的dv/dt通过电容耦合产生的电场干扰;2)邻近载流体通过磁场耦合产生的磁场干扰。通过调整罗氏线圈的结构,可有效抑制上述两类干扰,其作用机制进行如下分析。

2.1.1 电场干扰分析及抑制

罗氏线圈中利用屏蔽层抑制电场干扰的原理,如图4所示。

图4 罗氏线圈中屏蔽层抑制电场干扰的原理Fig.4 Principle of shielding to suppress electric field interference in Rogowski coil current sensor

电场干扰的噪声源是器件开关过程中的dv/dt, 在图4中用vnoise(t)表示。若罗氏线圈无屏蔽层,则噪声电压通过耦合电容(CX1)影响电流测量,即噪声电流沿路径1传导。若罗氏线圈配备屏蔽接地层,则噪声电流沿着路径2传导至系统地,即测量电流i′(t)免受影响。

2.1.2 磁场干扰分析及抑制

邻近载流体iadj(t)产生的磁场干扰可通过在罗氏线圈中增加回线进行抑制,其作用原理如图5所示。

在图5中,待测电流i(t)置于罗氏线圈中心位置处,根据法拉第电磁感应定律,在线圈端口感应出电压。但在实际测量中,待测电流周围不可避免地存在其他载流体(如PCB走线),因此抵御邻近载流体产生的磁场干扰是必要的。如图5所示,干扰电流iadj(t)产生与线圈平面垂直相交的磁场(绿色“×”)。若线圈中无回线,则会在端部感应出噪声电压vadj(t),进而影响测量结果;如果线圈中存在回线,则回线中会产生与vadj(t)大小相等、方向相反的电压,从而相互抵消,总的噪声电压为0。

图5 罗氏线圈中回线抑制磁场干扰的原理Fig.5 Principle of return wire to suppress magnetic field interference in Rogowski coil current sensor

综上,在罗氏线圈中,通过增加屏蔽层可有效抑制因dv/dt造成的电场干扰;通过增加回线可有效抑制邻近载流体造成的磁场干扰。据此,对现有三种典型PCB罗氏线圈的抗扰性能进行分析。

2.2 传统PCB罗氏线圈抗扰性能分析

根据罗氏线圈PCB的层数,可将传统PCB罗氏线圈分为三类:两层、四层和六层。下面分别对其抗扰性能进行分析。

2.2.1 两层PCB罗氏线圈

图6所示为两层PCB罗氏线圈的平面图。

图6 两层PCB罗氏线圈的平面图[15]Fig.6 Plan of two-layer Rogowski coil

如图6所示,PCB罗氏线圈主要由顶层和底层的走线以及连接顶层与底层的过孔组成。待测电流i(t)产生的磁场与线圈截面交链,在线圈端部感应出电压v(t)。然而,由于在结构上缺乏回线和屏蔽层,两层PCB罗氏线圈极易受到电场和磁场的影响。

2.2.2 四层PCB罗氏线圈

与两层PCB相比,四层PCB罗氏线圈具有了设计自由度,因此,可以增加屏蔽层或者回线设计提升线圈的抗扰性能。传统的四层PCB罗氏线圈的平面图如图7所示。

图7 四层PCB罗氏线圈的平面图[16]Fig.7 Plan of four-layer Rogowski coil

在图7(a)所示的四层PCB罗氏线圈中,其中间两层构成线圈结构,而最外面两层作为屏蔽接地层。根据2.1节分析,此结构能抵御电场干扰,但仍受到附近载流体的干扰(即磁场干扰)。为抵御磁场干扰,图7(b)利用最外两层构建线圈,而用中间两层作为回线。为进一步提升回线作用效果,也有学者对走线的形状进行改进(如鱼骨形设计[22]),此举虽能进一步提升对磁场的抗扰性,但因为缺少屏蔽层,仍易受到电场干扰的影响。

2.2.3 六层PCB罗氏线圈

为了同时抵抗电场和磁场干扰,有学者提出通过增加PCB层数的方式使线圈兼具屏蔽层和回线结构。图8为一种六层PCB罗氏线圈的平面图。

图8 六层PCB罗氏线圈的平面图[11]Fig. 8 Plan of six-layer Rogowski coil

在图8所示的六层PCB罗氏线圈中,顶层和底层作为屏蔽接地,而最内两层作为回线。根据2.1节分析,此结构能同时抵御电场和磁场干扰。然而,由于PCB层数的增加,该六层PCB罗氏线圈的带宽将降低,具体分析图9所示。

图9 六层PCB罗氏线圈的装配示意图Fig.9 Assembly diagram of six-layer Rogowski coil

(5)

对比式(3)与式(5)可知,由于六层PCB增加了罗氏线圈的寄生电容,因此降低了传感器带宽。此外,六层PCB的成本远高于四层PCB。

综上,随着PCB层数增加,罗氏线圈设计自由度逐渐提高,即可同时采用屏蔽层和回线来抵抗电场和磁场干扰。但PCB层数的增加引入了额外的寄生电容,降低了系统带宽,且增加了系统成本。从性能及成本角度考虑,四层PCB线圈极具开发潜力。然而,目前的四层PCB罗氏线圈设计方案在电场和磁场抗扰性间存在折中、无法兼具。因此,亟需能同时抵御电、磁干扰的四层PCB罗氏线圈。

3 双绞线型四层PCB罗氏线圈

为同时抑制开关电流测量时的电场和磁场干扰,本文提出一种双绞线型四层PCB罗氏线圈。本节首先从结构角度出发分析了其抗扰原理,然后利用COMSOL软件对其抗扰性能进行了仿真验证。

3.1 双绞线型四层PCB罗氏线圈

3.1.1 结构

双绞线型四层PCB罗氏线圈的三维和二维图如图10所示。

图10 双绞线型四层PCB罗氏线圈Fig.10 Four-layer twisted-pair PCB Rogowski coil

如图10(a)所示,四层PCB中间两层采用往返间隔式布线:从起点处开始利用走线和过孔逆时针构建线圈,每完成一匝构建后间隔一匝,继续逆时针构建线圈,直至完成一周构建;然后顺时针方向间隔式构建返回线圈,直至完成一周。待测电流置于罗氏线圈内部,根据叠加原理,逆时针线圈与顺时针线圈感生的有效电势叠加作为输出。线圈最外两层设计为屏蔽接地层,两层间通过通孔连接,并与系统地相连。其二维图如图10(b)所示。

3.1.2 抗扰性分析

双绞线型四层PCB罗氏线圈能同时抑制磁场和电场干扰。一方面,外部载流体(磁场干扰源)产生的磁场同时与逆时针线圈和顺时针线圈交链。由于两种线圈匝数相同、绕制方向相反,因此,两种线圈中感生出的噪声电压大小相等,方向相反,即净噪声电压为0。因此,双绞线型设计使罗氏线圈具备了“隐形回线”属性。

另一方面,双绞线型四层PCB罗氏线圈的外部屏蔽接地层能对电场干扰进行有效抑制。电路中器件开关过程产生的dv/dt(电场干扰源)通过器件与线圈间的耦合电容传导噪声电压。通过在线圈最外层覆盖屏蔽接地层,可有效将电场干扰诱发的噪声电流传导至系统地,进而使罗氏线圈抵抗电场干扰。除抵御电场干扰外,屏蔽接地层还可以抵御部分高频磁场干扰。

综上,双绞线型四层PCB罗氏线圈的“隐形回线”设计,可以抵抗外部载流体诱发的磁场干扰;通过最外层屏蔽接地设计,能有效抵御电场干扰。

3.2 双绞线型四层PCB罗氏线圈的仿真分析

采用COMSOL软件分别对双绞线设计对磁场干扰的抑制效果以及屏蔽接地层对电场干扰的抑制效果进行了仿真分析。

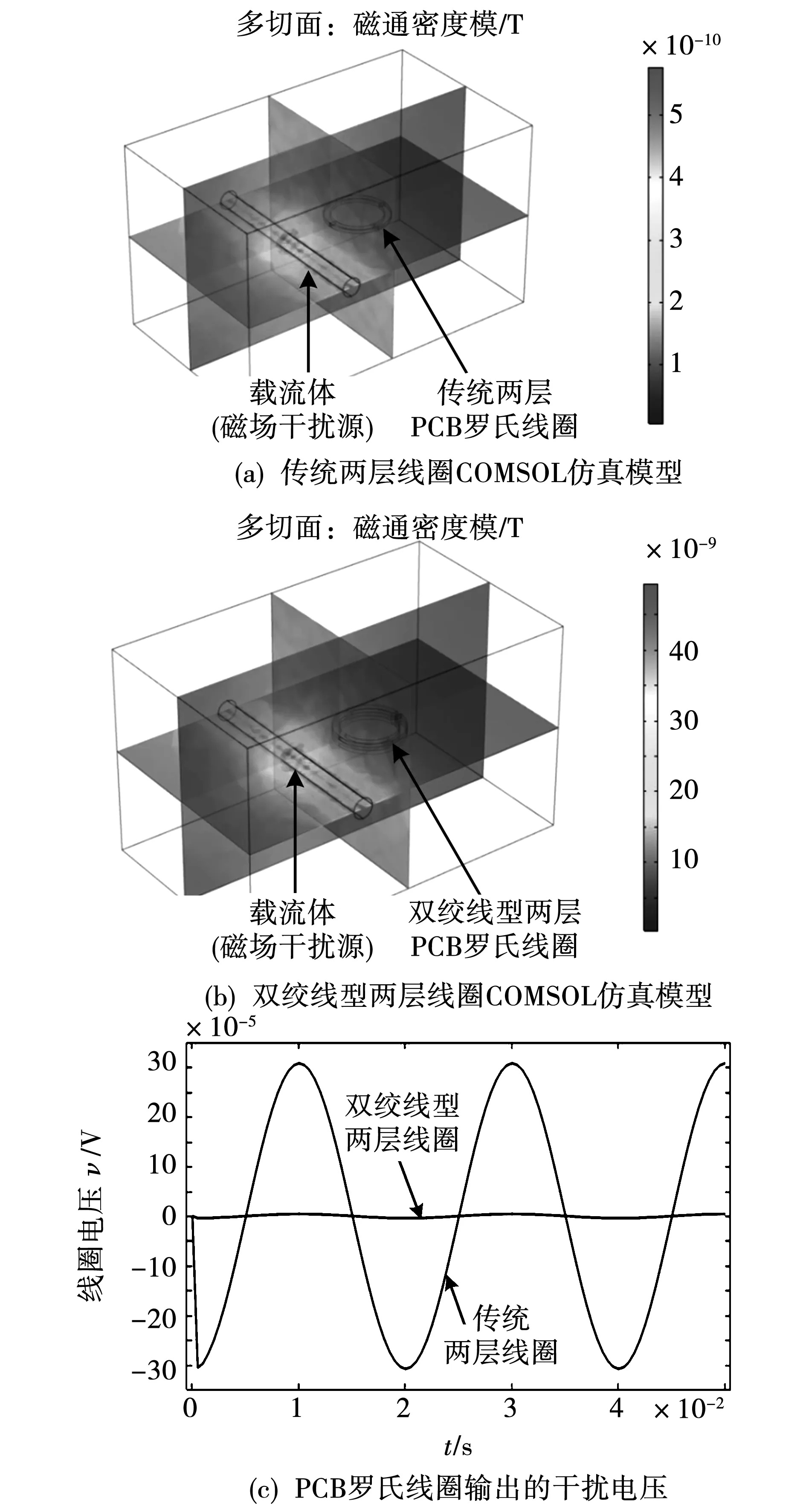

3.2.1 磁场干扰仿真分析

针对外部载流体产生的磁场对线圈的影响,在COMSOL软件中分别建立载流体(磁场干扰源)和两种PCB罗氏线圈(传统两层PCB线圈以及双绞线型两层PCB线圈)的三维模型。线圈模型的各项参数见表1。载流体与线圈平行放置,且与线圈中心水平距离为10 mm。载流体中正弦电流的幅值为1 A,频率为50 Hz。在仿真中,对模型进行网格化处理并以模型尺寸的3倍作为求解域。载流体产生的干扰磁场的磁通密度分布以及两种PCB罗氏线圈在磁场干扰下的输出电压如图11所示。

由图11(a)和图11(b)可以看出,载流导体产生的干扰磁场与PCB罗氏线圈垂直交链。理想情况下,罗氏线圈因磁场干扰产生的电压为0。从图11(c)可以看出,传统两层PCB罗氏线圈受磁场干扰的影响明显,其感生电压的幅值高于30×10-5V。而双绞线型两层PCB罗氏线圈因磁场干扰诱发的感生电压幅值仅为0.43×10-5V。这是因为双绞线线圈具有“隐形回线”设计,即顺时针线圈与逆时针线圈在干扰磁场下的输出电压大小相等、方向相反,可以相互抵消。此仿真说明双绞线设计能抵抗载流导体产生的磁场干扰。

图11 传统两层PCB罗氏线圈与双绞线型两层PCB罗氏线圈的磁场抗扰性仿真结果Fig.11 Simulation results of between traditional two-layer PCB Rogowski coil and twisted-pair two-layer PCB Rogowski coil in terms of magnetic-immune ability

3.2.2 电场干扰仿真分析

针对开关器件dv/dt通过耦合电容对线圈的影响,在COMSOL软件中建立平行板电容器和两种PCB罗氏线圈(双绞线型两层以及四层线圈)的三维模型。线圈置于平行板电容器模型内部,两平行板之间相距10 mm。为模拟器件开关过程中高频的dv/dt,在电容器两端施加幅值为1 V、频率为10 MHz的高频电压。干扰电场的分布以及两种PCB罗氏线圈在电场干扰下的输出电压如图12所示。

图12 双绞线型两层PCB罗氏线圈与双绞线型四层PCB罗氏线圈电场抗扰性仿真结果Fig.12 Simulation results of between twisted-pair two-layer PCB Rogowski coil and twisted-pair four-layer PCB Rogowski coil in terms of electric-immune ability

如图12(c)所示,由于缺少屏蔽接地层,双绞线型两层PCB罗氏线圈在电场干扰下输出电压的幅值为45 mV。当在线圈最外层加入屏蔽接地后,线圈的输出电压降为6 mV。此仿真说明屏蔽接地层能有效地抵抗器件的dv/dt通过容性耦合产生的电场干扰。

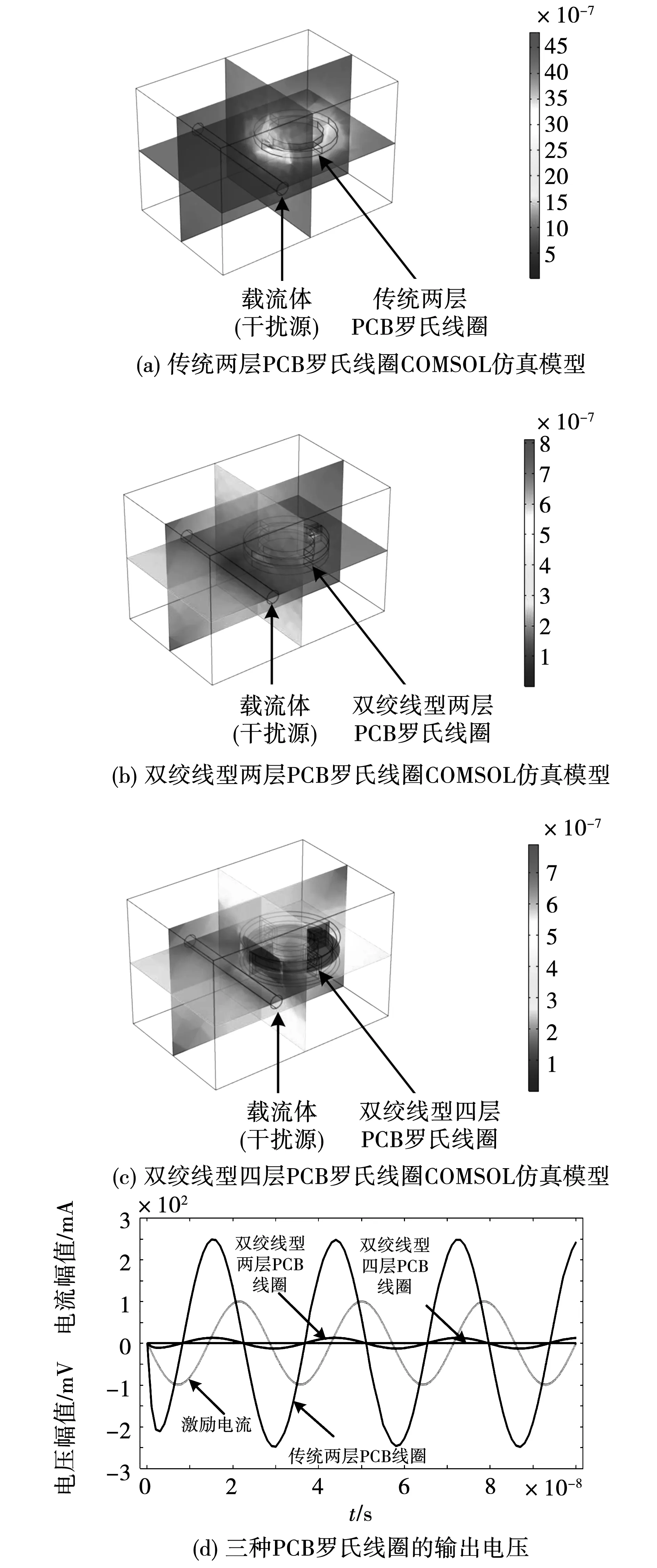

3.2.3 三种PCB罗氏线圈的仿真对比分析

为了进一步说明双绞线型四层PCB罗氏线圈的抗扰效果,本节对三种PCB罗氏线圈(即传统两层、双绞线型两层以及双绞线型四层)进行仿真对比:在COMSOL中分别建立载流体与PCB线圈的三维模型,线圈模型尺寸见表1,设置激励电流幅值为100 mA,频率为35 MHz。载流体与线圈平行放置,且与线圈中心距离为10 mm。在仿真中,以模型尺寸的3倍作为求解域并进行网格化处理。三种PCB罗氏线圈仿真图及在干扰源下的输出电压如图13所示。

图13 三种PCB罗氏线圈的仿真图及其输出电压Fig.13 Simulation diagrams and output voltages of three kinds of PCB Rogowski coils

从图13(d)可以看出:传统两层PCB线圈受到电场与磁场的影响,导致其输出干扰电压幅值较大,约为250 mV;双绞线型两层PCB线圈具有“隐形回线”结构,可以抵消垂直干扰磁场对线圈的影响,PCB线圈干扰电压由原来的250 mV降至13 mV;为了消除电场影响,进行接地屏蔽,双绞线型PCB线圈由两层结构变为四层结构。仿真结果显示双绞线型四层PCB线圈输出干扰电压很小,仅为3.5×10-4mV。因此,上述仿真结果表明双绞线型四层PCB罗氏线圈具有较强的抵抗电磁干扰能力。

4 实验验证

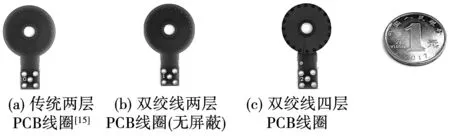

为对比验证所提双绞线型四层PCB罗氏线圈的抗扰性能和测量精度,设计制作了三种PCB罗氏线圈,其实物图如图14所示。线圈的详细参数如表1所示。

图14 PCB罗氏线圈实物图Fig.14 Photos of PCB Rogowski coils

表1 双绞线型四层罗氏线圈层PCB参数

4.1 双绞线型四层PCB罗氏线圈抗扰性能验证

PCB罗氏线圈抗扰性测试示意图如图15所示。

图15 PCB罗氏线圈抗扰性测量示意图Fig.15 Sketch of experimental setups for testing the noise-immunity of PCB Rogowski coil

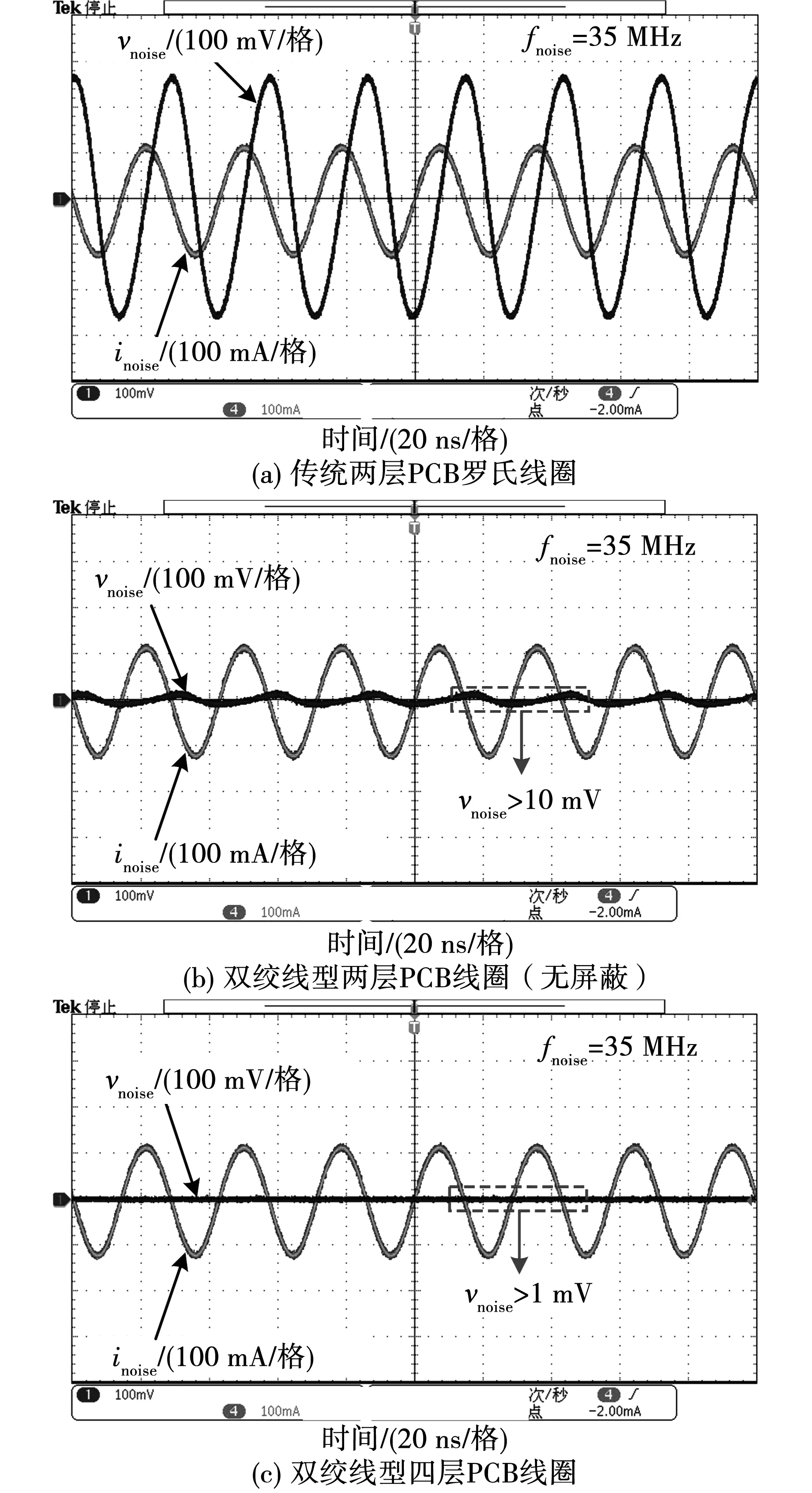

利用信号发生器与10Ω电阻产生干扰电流inoise,并通过带宽为120 MHz的电流钳记录。将三种待测PCB罗氏线圈与inoise平行放置,使inoise的磁场垂直穿过线圈平面。同时,线圈外延与噪声电流载体接触,使线圈处于电场噪声中。通过示波器记录噪声电流inoise和线圈电压vnoise,其结果如图16所示。

图16 PCB罗氏线圈抗扰性测试结果Fig.16 Testing results of PCB Rogowski coils in terms of noise-immunity ability

由图16(a)可以看出传统两层PCB罗氏线圈抗扰能力较差,其感生电压vnoise与噪声电流频率相同inoise(即fnoise=35 MHz),且vnoise幅值较高(高于250 mV)。这是因为其既不具备回线,又不具备屏蔽层,因此,同时受到了电场和磁场干扰的影响。图16(b)采用双绞线型结构,从图中可以看出vnoise显著变小,但其幅值仍高于10 mV。双绞线型结构的回线设计能抑制磁场干扰,但由于缺少屏蔽,线圈仍受到电场的影响。采用双绞线型四层PCB罗氏线圈的效果如图16(c)所示,可以看出,vnoise进一步变小(幅值低于1 mV)。图17进一步展示了三种PCB罗氏线圈输出噪声电压vnoise的快速傅里叶分析结果,可以看出,与其他两种结构相比,双绞线型四层PCB罗氏线圈具有更好的抑制电磁干扰的能力。

图17 PCB罗氏线圈vnoise快速傅里叶分析Fig.17 FFT results of vnoise for PCB Rogowski coil

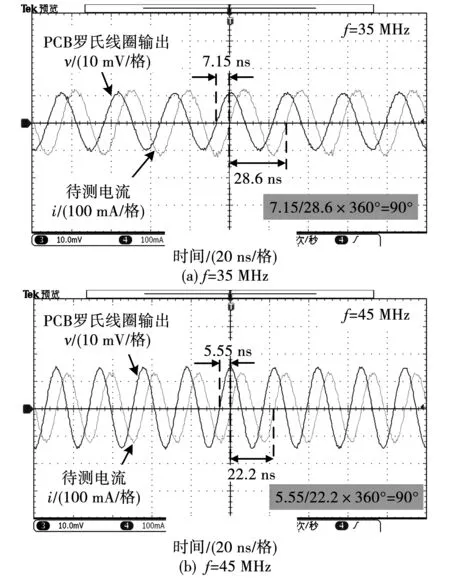

4.2 双绞线型四层PCB罗氏线圈高带宽验证

将图15中信号发生器经电阻产生的电流穿过自制的双绞线型四层PCB罗氏线圈,利用示波器记录线圈的输出电压v,并与带宽为120 MHz的电流钳记录的电流i进行比较,结果如图18所示。可以看出PCB罗氏线圈的输出电压v比待测电流i相位超前90°。这是因为罗氏线圈输出的感生电压与一次侧电流成微分关系,具体分析见式(2)。将待测电流频率从35 MHz升至45 MHz后,此线圈仍能实现准确追踪,即此线圈带宽上限高于45 MHz,满足高带宽的测量需求。

图18 PCB罗氏线圈带宽测试结果Fig.18 Bandwidth testing results of PCB Rogowski coil

4.3 基于双绞线型四层PCB罗氏线圈的SiC MOSFET开关电流测量

双脉冲测试中需测量开关电流用于评估功率器件的开关特性[15]。本节以双脉冲测试为例,说明双绞线型四层PCB罗氏线圈在SiC MOSFET开关电流测量中的应用。双脉冲测试平台的详细参数见表2,图19为双脉冲测试的原理图及实物图。如图19所示,开关电流i穿过PCB罗氏线圈中心感生出电压v,经积分器[15]后得到复原电流i′。此结果与PEM CWT06的测量结果对比如图20所示。可以看出,本文制作的20匝的四层PCB罗氏线圈可以准确测量SiC MOSFET的开关电流。

表2 双脉冲测试平台参数

图19 基于PCB罗氏线圈的SiC MOSFET开关 电流测量Fig.19 Switch current measurement of SiC MOSFET based on PCB Rogowski current sensor

图20 基于双绞线型四层PCB罗氏线圈的开关 电流测量结果Fig. 20 Measured switch current of SiC MOSFET based on a 20-turn twisted-pair four-layer PCB Rogowski coil

5 结 论

本文针对四层PCB罗氏线圈用于碳化硅器件的开关电流测量时无法同时抵抗电场和磁场干扰的问题,提出了一种能同时抑制电、磁干扰的双绞线型四层PCB罗氏线圈。结合理论分析、COMSOL仿真和实验研究得到以下结论:

1)通过采用回线设计,PCB罗氏线圈可有效抵抗邻近载流体产生的与线圈平面正交的磁场干扰;通过采用接地屏蔽层,PCB罗氏线圈可有效抵抗邻近开关通过耦合电容产生的电场干扰。

2)本文提出的双绞线型四层PCB罗氏线圈由于采用双绞线设计,具有“隐形回线”属性,且最外层进行了屏蔽接地设计,因此能同时有效抑制磁场和电场干扰。

3)双绞线型四层PCB罗氏线圈兼具高带宽、强抗扰和小体积特性,适合用于碳化硅器件的开关电流测量。