基于有限元的叠层母排优化设计方法

2021-02-02张鹏程张正卿帅骁睿

张鹏程,张正卿,吴 钫,帅骁睿,李 锐

(武汉第二船舶设计研究所,武汉 430205)

0 引言

船用电力电子变换器正朝着高效率、高功率密度、高电能质量和高可靠性等方向发展。功率半导体器件作为电力电子变换器中的核心部件,其开关速度正逐渐增加,比如SiC等宽禁带半导体器件的开关速度已达到几十ns。较快的开关速度会造成较大的di/dt,从而在开关过程中通过换流回路的杂散电感形成较高的电压尖峰,不利于半导体器件的安全稳定运行以及变换器部件的选型设计。因此,为匹配较快的开关速度,换流回路中母线电容与半导体器件之间的连接部件需具有较低的杂散电感。

相比于传统同轴电缆以及铜条等的回路连接方式,叠层母排由于其低杂散电感特性广泛成为变换器母线与开关器件之间的连接部件。目前有文献针对叠层母排的杂散参数的计算与优化设计开展了研究[1-2]。文献[3-4]推导出了叠层母排杂散参数的解析表达式,但解析表达式并不适用于层数较多、结构较为复杂的叠层母排,同时不能反映过孔、接线柱等部件对杂散电感量的影响。文献[5]探索了两电平结构三层母排与两层母排杂散电感量的区别,并研究了电容排布方式对杂散电感量的影响。文献[6]探索了三电平结构器件排布顺序对母排杂散电感量的影响,提出了较为优化的器件排布方式。

本文以有限元软件为工具,系统地分析了叠层母排各结构参数对杂散电感的影响规律,并通过这些规律提炼出叠层母排优化设计的规则,并以三电平逆变电源为实例,验证这些设计规则的有效性。

1 叠层母排低杂散电感特性分析

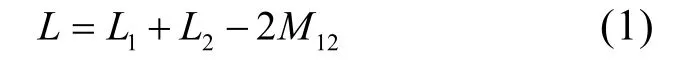

相比于同轴电缆以及铜条,叠层母排具有更小的杂散电感的原因在于叠层母排所具备的交叠特性。叠层母排将多层母排叠压,中间用很薄的绝缘层隔离,利用两层电流方向相反的母排之间的互感,从而减小母排的总杂散电感。从电路模型的角度分析,两层叠层母排等效电路模型如图1所示,L1是上层母排的自感,L2是下层母排的自感,M12是上下两层之间的互感,由于电流方向相反,总电感量为:

通过将上下两层紧密贴合,使两层母排之间的耦合系数接近 1,从而极大地减小叠层母排总杂散电感。

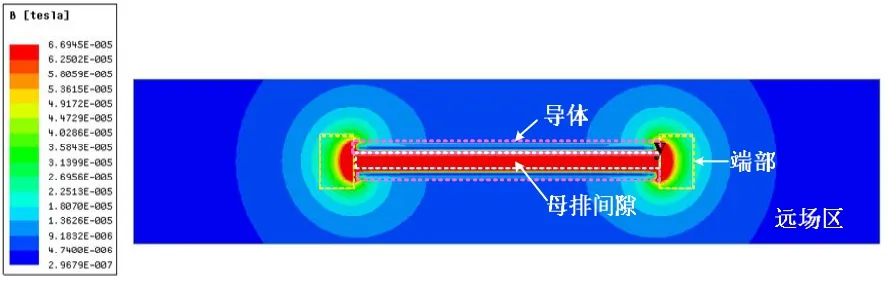

图 1 叠层母排磁场分布

从磁场分布的角度分析,如图 1为两层叠层母排的磁场分布图,从图中可知磁场集中在两层叠层母排之间的交叠区,而在叠层母排以外的空间,磁场由于方向相反而互相抵消,从而极大地减小了空间中的磁场能量JM,而空间磁场能量与电感量有如下关系

表1为厚度T=1 mm,间距d=2 mm,宽度b=200 mm,长度a=200 mm的两层叠层母排内各区域磁能占比,根据表1可知,磁能主要集中于交叠区,而在交叠区以外,磁场因电流的反向交叠相互抵消,从而极大地减小了叠层母排的总杂散电感。

表1 分区磁能占比

根据以上分析可知,叠层母排的低杂散电感特性主要来源于其电流回路的反向交叠。因此在叠层母排的设计过程中,母排之间的交叠程度是最需关切的因素,能够增加交叠程度的措施会减小杂散电感,而减小交叠程度的措施往往会增大杂散电感。

2 叠层母排结构参数对杂散电感的影响

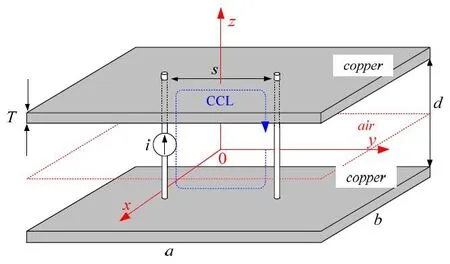

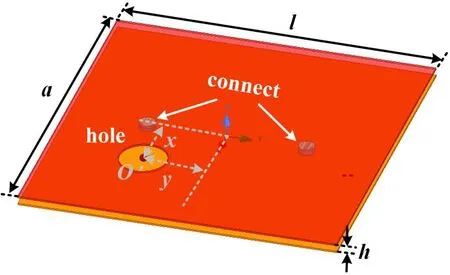

本章以两层叠层母排为例,利用有限元仿真工具,探索各参数对叠层母排杂散电感量的影响。图2为两层叠层母排结构示意图,b为叠层母排宽度,T为厚度,d为两层母排间距,s为换流回路长度。

图2 两层叠层母排结构尺寸

2.1 频率f与厚度T对杂散电感量的影响

频率f指开关过程的等效频率,该频率取决于开关时间Tswitch:

频率主要影响电流在母排内的分布,频率越高,集肤深度越小,电流就越向表面集中,集肤深度δ表达式为:

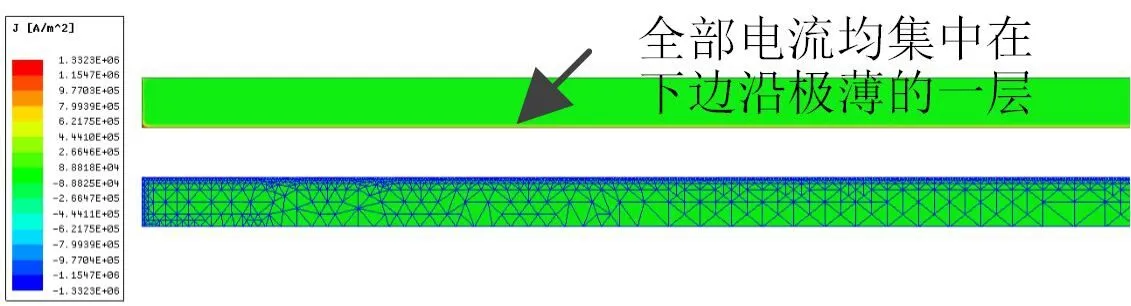

根据式(4),100 kHz的电流在铜排内的集肤深度为0.21 mm,如图3所示为100 kHz电流在母排内的分布情况(电流全部集中在下边沿);当电流频率减小为10 kHz时,电流在母排内的分布情况如图4所示。可以看出当电流频率减小时,电流在母排内的分布更加均匀,而导体中磁通量密度B的分布形式与电流密度的分布相似,因此随着频率的减小,母排的杂散电感逐渐增大。

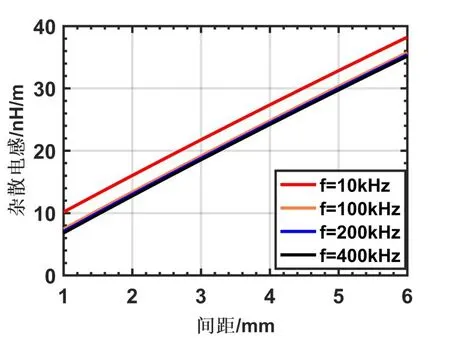

然而频率只影响叠层母排导体区内的磁场能量,根据上文的分析,导体区内的磁场能量只占叠层母排总磁场能量的一小部分,因此频率对叠层母排杂散电感的影响较小,是杂散电感的次要参数。图5是不同母排间距下杂散电感随频率的变化。根据图5可以看到,当电流频率超过200 kHz后,双层叠层母排杂散电感随频率的变化很小,可以近似忽略。

图3 100 kHz电流分布

图4 10 kHz电流分布

图5 叠层母排杂散电感随频率变化曲线

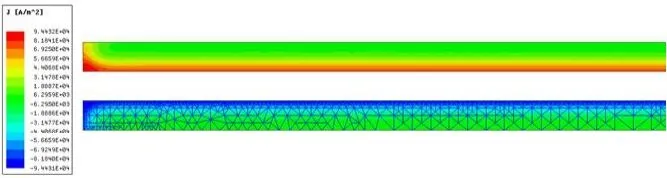

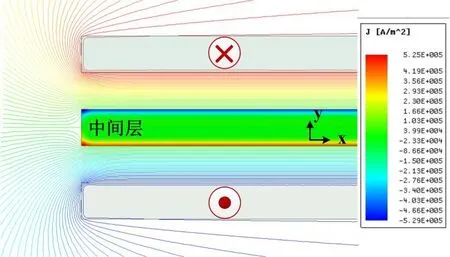

但需要注意的是,在多层叠层母排中,不相邻的两层母排之间的间距同时也包含了母排的厚度,图 6(a)为三层叠层母排,当电流去线与回线分别流经第一层和第三层时,去线与回线的间距也包含了中间层的厚度,为2d+T。因此本文将图6(a)的叠层母排结构与图 6(b)的叠层母排结构对比,以探究厚度T对多层叠层母排杂散电感的影响。经Ansys仿真可得,图 6(a)与图 6(b)的杂散电感量十分接近,这是由于在中间层的上下表面分别感应了与第一层和第三层方向相反的涡流,磁场在中间层导体内部均抵消,如图 7所示。因此厚度T对于多层叠层母排的杂散电感量也几乎没有影响。

图6 中间层对杂散电感的影响

图7 中间层屏蔽效果

2.2 叠层母排间距d对杂散电感量的影响

当母排间距d远小于叠层母排宽度b时,叠层区的磁场强度B主要取决于叠层母排的宽度b,而不随间距d的变化发生改变,叠层区的体积与母排间距d成正比,因此叠层区的磁场能量与母排间距d成正比。考虑到叠层区中磁场能量占总磁场能量的绝大部分,因此叠层母排的杂散电感近似正比于母排间距d,仿真结果也验证了这一结论,如图8所示。

图8 间距对双层母排杂散电感影响

2.3 叠层母排宽度b对杂散电感量的影响

叠层区磁场强度H及磁感应强度B与叠层母排宽度b成反比,而叠层区体积与叠层母排宽度b成正比,叠层区磁场能量公式为:

根据式(5),可以得到叠层区磁场能量与宽度b成反比。考虑到叠层区中磁场能量占总磁场能量的绝大部分,因此叠层母排的杂散电感近似反比于母排间距b,仿真结果也验证了这一结论,如图9所示。

图9 宽度对叠层母排杂散电感影响

2.4 换流回路长度s对杂散电感量的影响

图10 换流长度对杂散电感量的影响

图10为换流回路长度s由25 mm变化到150 mm时的L-s仿真曲线,由图可以看出,当s增加一倍时(从s=75 mm到s=150 mm),叠层母排回路的杂散电感从5.2 nH增大到7 nH。由此可以得到以下结论:当换流回路长度s增大一倍,换流回路杂散电感L近似增大0.3倍。

2.5 过孔对杂散电感量的影响

为了与开关管、二极管以及电容等器件连接,叠层母排各层不可避免需要增加过孔。增设的过孔会削弱母排之间的交叠程度,从而增加叠层母排的杂散电感。

图11 过孔位置坐标图

本文考察处于不同位置的过孔对叠层母排杂散电感影响的大小。如图11所示为双层母排简化三维模型,其中母排尺寸为:宽度b=200 mm,厚度T=2 mm,间距d=2 mm,长度l=200 mm,换流回路长度s=100 mm。过孔直径为30 mm,坐标中心为两个导体柱的中点,过孔圆心位置坐标为(x, y)。

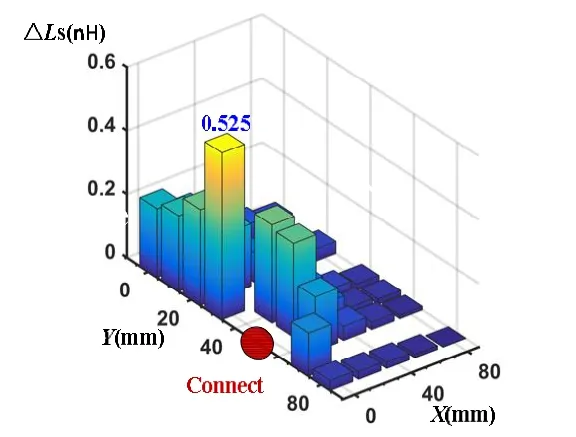

未开孔时,双层叠层母排杂散电感为L=5.98 nH,母排表面电流密度分布如图 12所示。图13表明,导体柱之间的电流密度高于导体柱两边以及外面的电流密度,并且越靠近导体柱,电流密度越高。

图 12 母排表面电流分布

开孔位置对双层叠层母排杂散电感的影响如图14所示,结合图11以及图14可以看出,当过孔位置位于电流密度较大的区域时,其对母排杂散电感的影响就越大。在本模型下,当过孔中心距离导体柱最近(过孔中心坐标(0, 30 mm))时,开孔引入的附加电感ΔLs约为0.525 nH,达到了原叠层母排杂散电感值得 8.8%。在母排实际设计中,为减小杂散电感,过孔应尽量避免处于电流密度较高的区域。

图13 过孔对表面电流分布的影响

图14 过孔对杂散电感的影响

2.6 非交叠连接件对杂散电感量的影响

不同层之间需要导体柱进行连接,以infineon primepack封装为例,IGBT的引出端需要直径为10mm的导体柱连接,经Ansys仿真可得,该导体柱每1 mm长度会引入杂散电感量为0.98 nH。

当部分器件需要叠层母排引出连接条进行连接时,如图15所示,该连接条由于不交叠,也会引入较大的杂散电感量。经Ansys仿真分析,厚度为2 mm,宽度为20 mm的连接条,每1 mm长度会引入0.853 nH的杂散电感量。

图15 叠层母排连接条

3 叠层母排设计规则与优化实例

3.1 叠层母排设计规则

根据上述结构参数与杂散电感的关系,可以提炼出以下叠层母排的设计规则:

1)叠层母排层数是影响杂散电感量的关键参数,需注重对叠层母排层数的优化。

母排间距对杂散电感量有较大影响,母排间距主要取决于母排厚度,绝缘层厚度以及母排层数。根据上文论述,在多层母排中,母排厚度对杂散电感量几乎没有影响,而绝缘层厚度主要取决于耐压需求,因此母排间距主要取决于母排层数的设计。一般而言,对于一个N电平中点钳位电路,其叠层母排层数可以优化至 2(N-1)层[2]。根据下文优化实例可知,通过合理的排布,三电平逆变器母排层数可进一步优化为2(N-1)-1层。

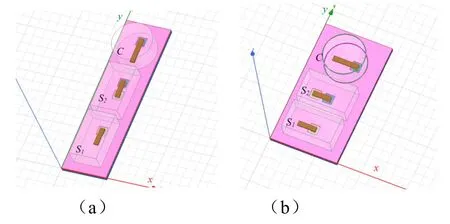

2)电流方向与器件摆放方向应垂直

通过令电流方向与器件摆放方向垂直,可以增大母排宽度b,减小换流回路长度s,从而减小母排杂散电感量。如图 16(a)所示为电流方向与器件摆放方向平行的布置方式,电流路径为S1-S2-C,走向与y轴平行,器件摆放方向同样与y轴平行,从而构成了狭长形状叠层母排。如图16(b)所示为电流方向与器件摆放方向垂直的布置方式(电流走向沿y轴,器件摆放方向沿x轴),相比于图16(a)中的排布方案,换流回路长度s减小,母排宽度b增加,经仿真计算可得图16(b)中的垂直排布方式杂散电感量更小。

图16 电流方向与器件摆放方向(a)平行,(b)垂直

3.2 三电平逆变器母排优化实例

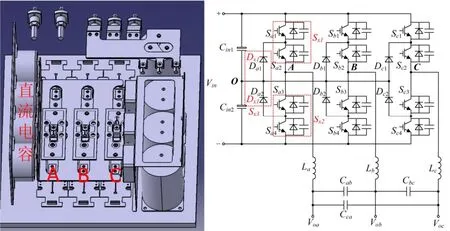

如图17所示为100 kW逆变模块电路图以及三维结构图。在图17中,A、B、C三相依次排列,直流电容布置在A相相临的侧面,直流电容与C相的电流路径最长,因而C相母排杂散电感最大。

图17 逆变模块原始三维结构

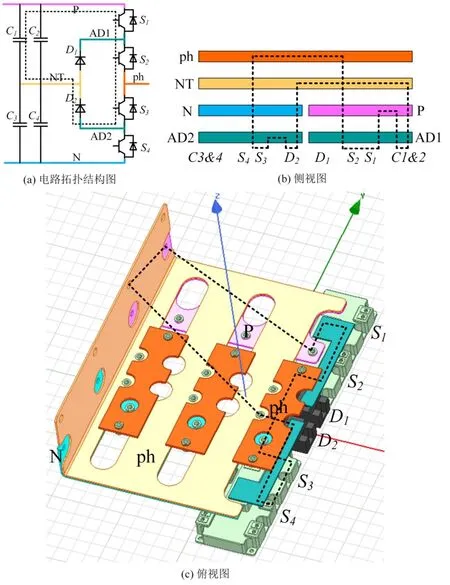

图18 (a)所示为三电平电路拓扑结构,其中虚线部分为长换流路径;图18(b)所示为叠层母排的侧视图;图18(c)所示为叠层母排的俯视图。经Ansys仿真可得长换流路径杂散电感为97.1 nH。根据上文所总结的三个规则,对该母排设计做如下优化:

图18 叠层母排原始布置

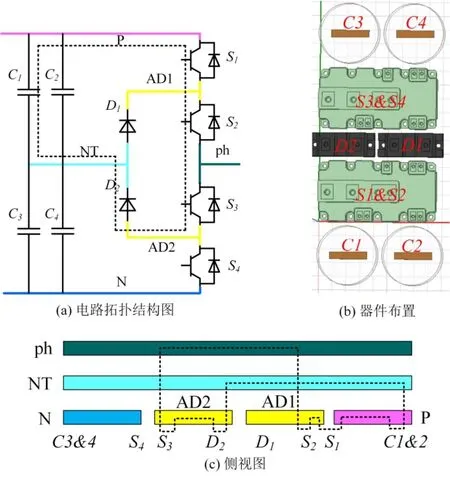

1)通过合理布置,将母排层数由4层优化为3层,母排布置如图19(c)侧视图所示;

2)将器件摆放方向与电流走向垂直,器件布置如图19(b)所示;

图19 叠层母排排布优化

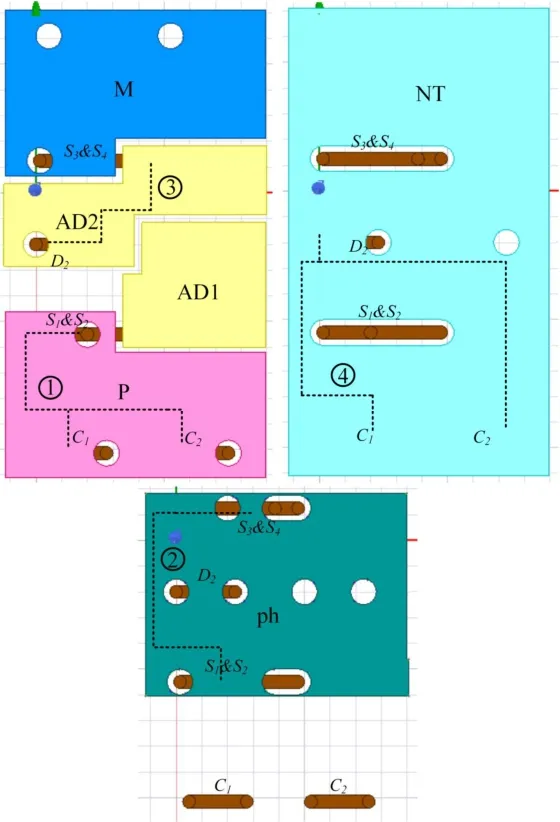

3)尽量平铺各层母排,在保证绝缘的情况下尽量减小过孔面积,各层结构如图20所示。

经上述设计规则进行优化后,通过Ansys仿真可得长换流回路母排杂散电感只有43.77 nH,相比于原设计的97.1 nH,杂散电感量得到了显著优化,验证了上述设计规则的有效性。

4 结论

本文基于有限元方法,得到了叠层母排杂散电感量与结构参数之间的规律,提炼出了叠层母排的设计规则。以三电平逆变电源为典型实例进行对比仿真分析,验证了叠层母排杂散参数规律的准确性以及叠层设计规则的有效性。

图20 优化后叠层母排各层结构图