面向窄节距倒装互连的预成型底部填充技术*

2021-01-26石修瑀贾松良

王 瑾, 石修瑀, 王 谦, , 蔡 坚, , 贾松良

(1.清华大学微电子学研究所, 北京 100084; 2.北京信息科学与技术国家研究中心, 北京 100084)

1 引言

传统的底部填充技术是在完成倒装芯片互连之后进行的, 因此也被称为组装后底部填充技术(Post-assembly Underfill)[1-2]。 应用最为广泛的是毛细底部填充(CUF)和模塑底部填充(MUF)。 近年来随着系统集成度不断提高,倒装芯片上凸点的尺寸和节距也变得越来越小,凸点节距小于100 μm,甚至不大于10 μm, 传统的组装后底部填充技术由于是在凸点互连之后才进行底部填充的,常常会出现凸点间填充不完全到位、产生孔洞等缺陷,使封装互连的可靠性降低[3]。

为了适应倒装芯片窄节距互连的填充需求,产业界提出了一种新型的预成型底部填充技术(Preassembly Underfill)[4-5]。这种方法既能简化工艺,又能对窄节距互连(小于100 μm)进行良好的底部填充。此外,研究机构还提出了一些方法对预成型底部填料的性能进行改进, 从而实现低热膨胀系数(约20×10-6/℃)、低粘度(小于20 Pa·s)以及高热导率[大于1 W·(m·K)-1]等优良性能[6-7],进一步提高了预成型底部填充的可靠性。

本文将聚焦于窄节距倒装芯片互连中的预成型底部填充技术, 介绍该技术的工艺流程以及材料特性,并针对其在实际生产中遇到的问题,总结目前已有的解决方案并预测这种技术未来的发展趋势。

2 预成型底部填充技术

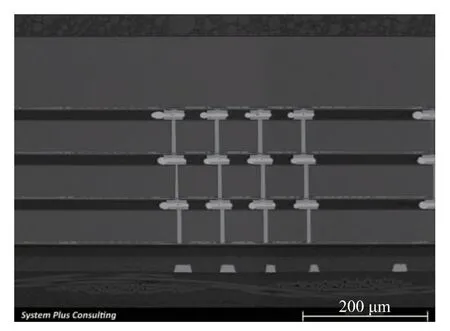

传统的组装后底部填充技术主要适用于大节距凸点互连中, 而对于节距小于100 μm 的倒装芯片凸点互连,如仍采用这种技术,易在填充时产生大量孔洞,如图1 所示。因此,对于窄节距倒装芯片互连,目前产业界多采用预成型底部填充技术。

图1 组装后底部填充技术在应用于窄节距互连时产生的孔洞[3]

预成型倒装芯片底部填充技术是指底部填料在芯片互连之前就被施加在芯片或基板上,在后续的回流或热压键合过程中,芯片凸点互连与底部填充固化同时完成。 该技术主要可以归纳为2 种方法: 非流动底部填充(NUF)和圆片级底部填充(WLUF)。

2.1 非流动底部填充

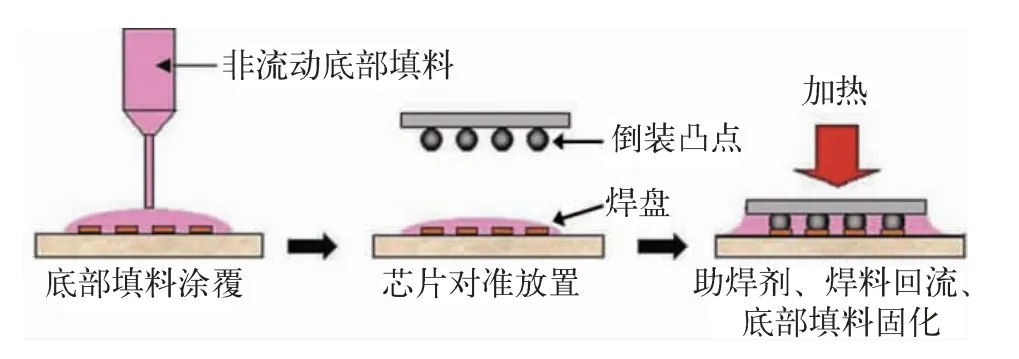

美国佐治亚理工学院于1996 年首先提出了非流动底部填充技术[8]并成功应用于无铅C4 凸点的倒装芯片组装[9],具体工艺流程如图2 所示[2]。 该技术省去了单独的助焊剂涂敷、底部填料的毛细流动注入和助焊剂清洗步骤,将焊料凸点回流和底部填充剂固化结合为一个步骤,从而既消除了底部填充时易产生的孔洞又提高了底部填充工艺的生产效率。

图2 非流动底部填充工艺流程[2]

近年来,针对倒装芯片窄节距凸点的非流动底部填充技术也取得了发展。AMKOR[5]首先提出了利用非导电浆料(NCP)用作非流动底部填料,在实现凸点互连的同时完成NCP 的固化,其工艺流程如图3 所示。

图3 面向窄节距凸点互连的NCP 非流动底部填充技术工艺流程[5]

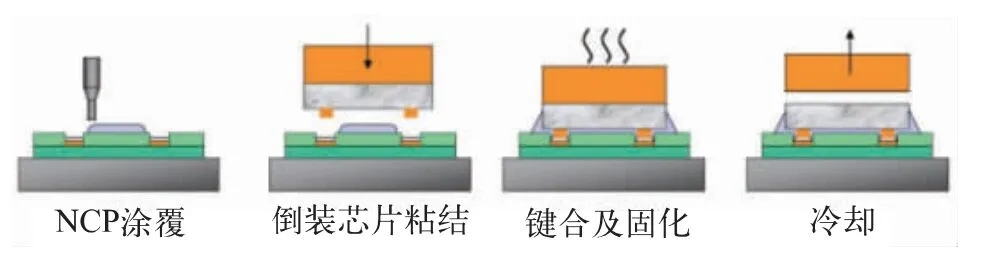

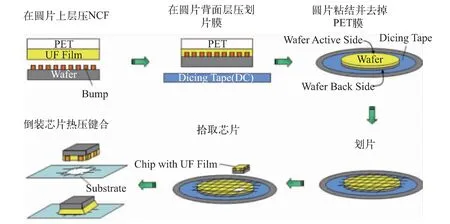

早期针对大节距凸点(图2)的非流动底部填充技术是通过回流来实现凸点互连与底部填料固化的,为了避免底部填料中的SiO2颗粒镶嵌在互连界面影响接头的形成与电互连的可靠性,早期的底部填料中不含或只含很少的SiO2填料。 在基于NCP 的非流动底部填充中(图3),由于在键合过程中施加压力可以减少SiO2颗粒在互连界面的镶嵌, 因此NCP 材料中含有SiO2填料, 同时有研究表明随着NCP 中SiO2填料质量百分比的增加,NCP 材料的热膨胀系数(CTE)会减小,而粘度和杨氏模量会增加,组装的可靠性也随SiO2填料的增加而有所提高[10]。目前NCP 非流动底部填充技术已经成功应用于Samsung 手机处理器的封装中,如图4 所示。

图4 应用于Samsung 手机处理器中的NCP 非流动底部填充技术[11]

2.2 圆片级底部填充

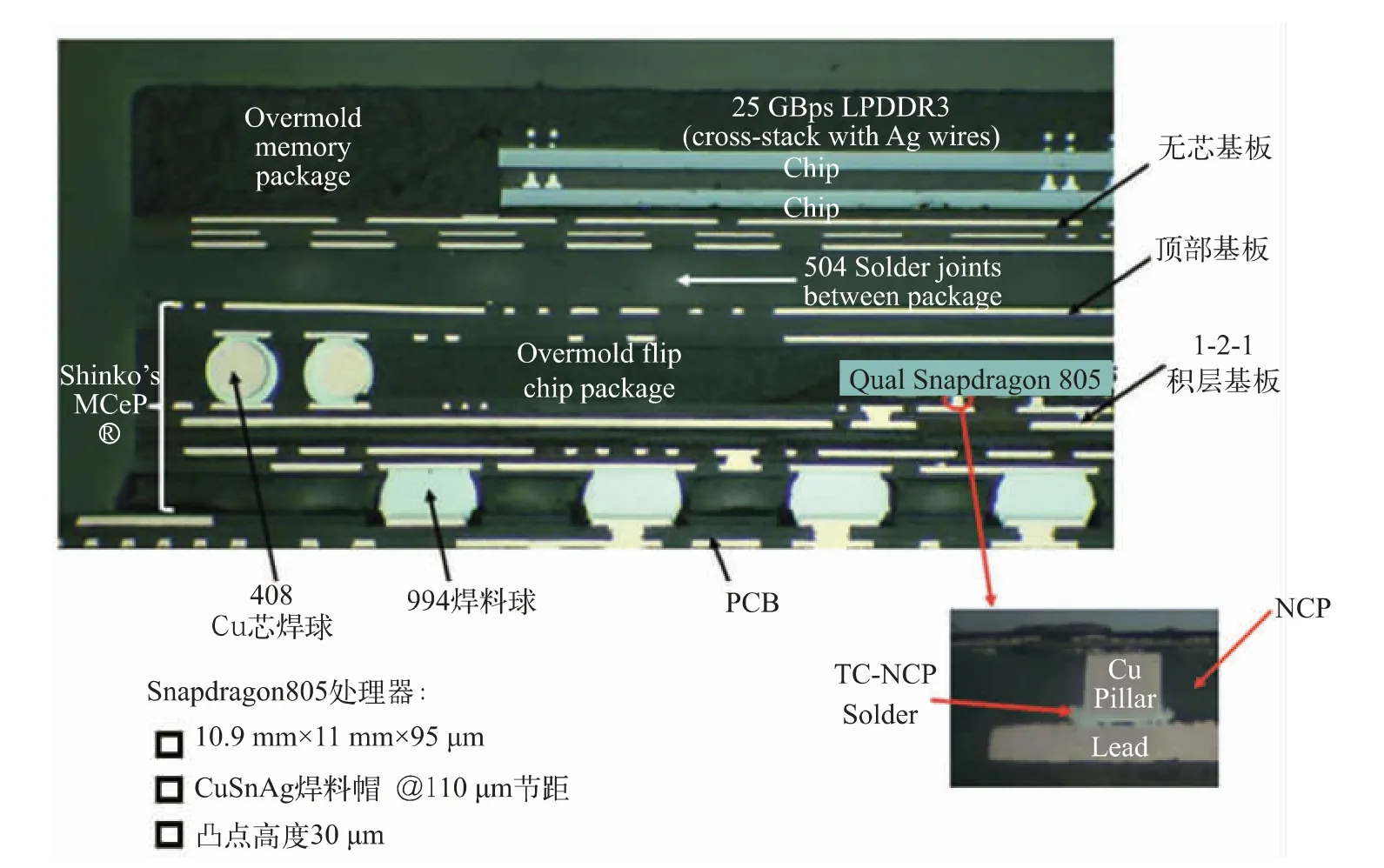

为了进一步提高生产效率,产业界在非流动底部填充技术的基础上提出了圆片级底部填充技术。 通过旋涂或层压的方式将底部填料施加在整个圆片上,然后将圆片划片切成单颗的芯片,最后通过回流或热压键合来实现芯片与芯片/基板之间的凸点互连与底部填料固化。

目前应用较为广泛的圆片级底部填料是非导电薄膜(NCF),NCF 是以膜的形式存在,可以通过夹在聚对苯二甲酸乙二醇酯(PET)之类的塑料薄膜中以卷材形式使用。这种特性有利于NCF 在圆片级底部填充工艺中的应用,其工艺流程如图5 所示[12],首先在圆片正面真空层压NCF,然后在圆片背面贴划片膜,通过划片将圆片切成单颗芯片,最后倒装芯片经过热压键合实现互连与固化成型。这种基于NCF 的圆片级底部填充技术多应用于节距为40~80 μm 的微凸点互连中。

图5 NCF 圆片级底部填充工艺流程[12]

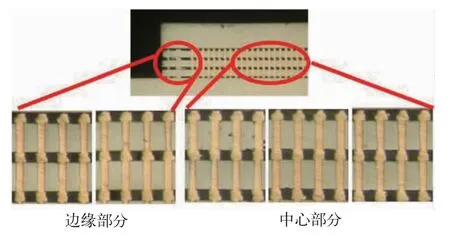

圆片级底部填充工艺成功的关键是要保证在划片之前,圆片上的底部填料处于半固化状态(B-Stage,或称B-阶), 具有足够的机械强度和稳定性以满足后续划片、 储存等的需求, 图6 为划片后的芯片边缘照片,没有发现底部填料的变形[13]。 同时处于B-阶的底部填料也具有“ 可回流性”,即具有熔化和流动的能力,从而在后续互连过程中焊料帽能够浸润焊盘并形成焊点。 因此,对于成功的圆片级底部填充而言,保证底部填料处于B- 阶以及控制后续的热压固化工艺是至关重要的。

同为预成型底部填充,NCF 的生产效率要比NCP高很多,因为NCF 可以在整个圆片上进行层压;同时NCF 工艺也较NCP 更好控制, 如热压过程中NCP 的溢出较难控制,限制了其在三维封装方面的应用。 但NCF 的缺点是流动性较NCP 差, 导致互连界面残留的底部填料较多,降低了接头的电互连可靠性;同时它不能灵活应对具有不同凸点高度的芯片,只能考虑配以不同厚度的膜。 目前,Sanyo[14]、Hitachi[15-16]、Tohoku[17-18]、DOW[19]、Hynix[20]、KAIST/Samsung[21-22]、Amkor/Qualcomm[23]和Toray[24-26]等都对基于NCF 的圆片级底部填充技术进行了研究, 并应用于2.5D/3D 集成中。 图7 为Samsung 在其动态随机存储器中应用NCF 底部填充技术的实例[15,27],它实现了基于硅通孔(TSV)的4 层存储芯片的互连与底部填充。

图6 涂有NCF 圆片在划片后芯片边缘的SEM 照片[13]

图7 Samsung 动态随机存储器中应用NCF 底部填充实例[27]

NCP 和NCF 材料主要由基体胶、稀释剂、增韧剂和其他添加剂组成。 基体胶主要有环氧树脂、酚醛树脂、聚酰亚胺及热塑性塑料等;稀释剂通常主要包括醇类、酯类稀释剂等;增韧剂包括低分子液体改性剂等非反应性增韧剂。 NCP 材料的主要供应商有Henkel、Namics、Nagase、Hitachi、Panasonic 等,NCF 的供应商有Henkel、Hitachi、Toray、Nitto Denko、Namics、Sumitomo 等。

3 预成型底部填充技术的最新进展

目前, 利用NCP/NCF 作为底部填料的预成型底部填充技术在窄节距倒装互连的三维堆叠存储芯片以及图像传感器芯片等方面都得到了较为广泛的研究与应用,但是在面向大规模量产和未来进一步的窄节距倒装互连时还存在一定的技术挑战,未来还需要在提高量产生产效率、提升电互连的可靠性以及开发纳米级高热导率填料等方向继续发展。

3.1 提高量产生产效率

预成型底部填充技术多用于节距小于100 μm 的凸点互连, 与传统的C4 凸点大批量回流之后进行底部填充相比,一般一次热压过程只能完成一个芯片的键合与底部填充,因此整体的生产效率较低。

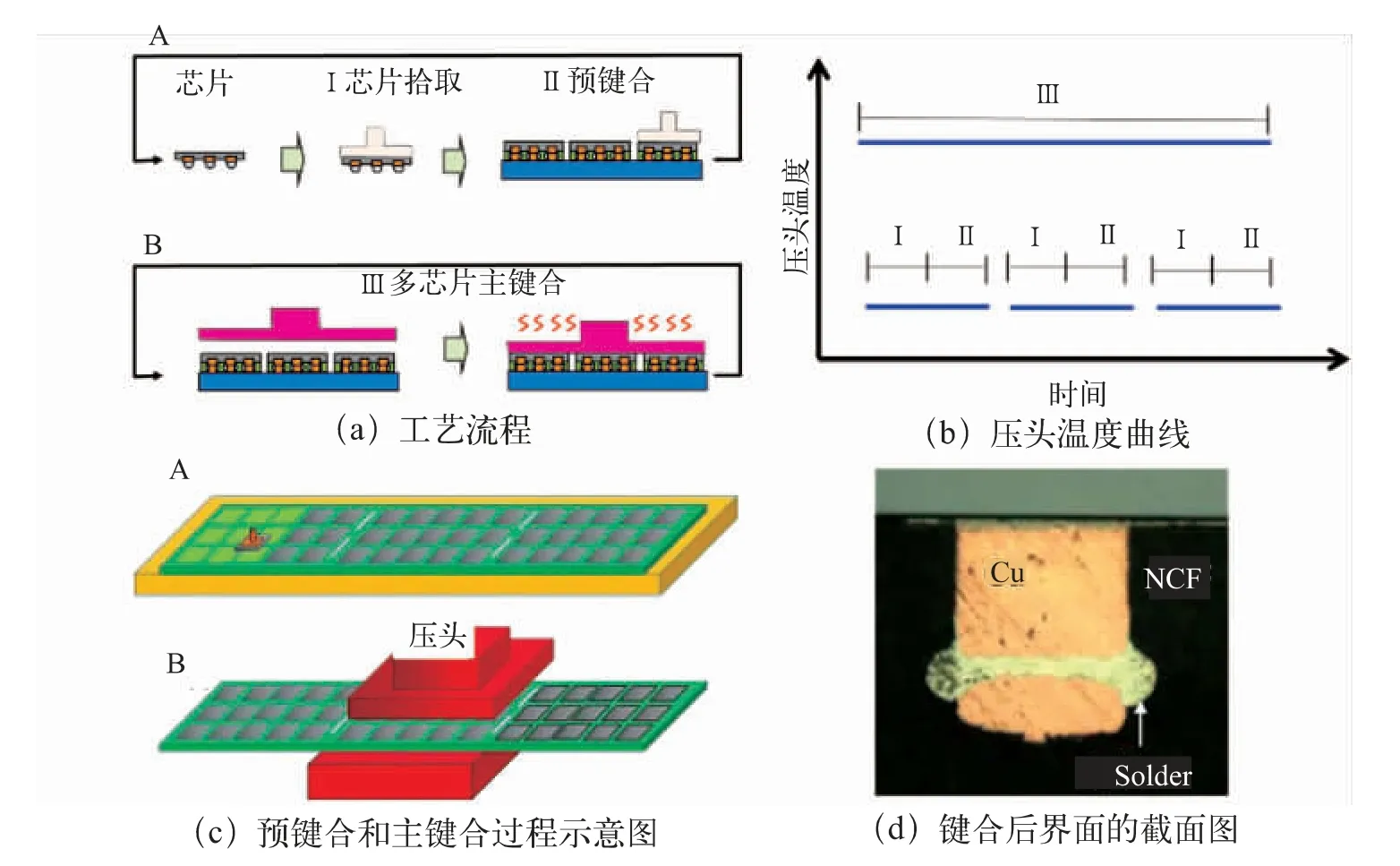

为了提高生产效率,TORAY[24]提出了将热压键合过程分为2 个过程进行:第一步是预键合,主要实现芯片的拾取和放置;第二步是主键合,通过一次热压过程完成多个芯片在基板上的键合。 这种将预键合和主键合分步(PMD)进行的方法能够较好地提高生产效率。PMD 工艺流程如图8(a)所示。它由A 和B 的2 个并行工序组成, 通过分步预键合A 和主键合B 的方法, 压头的温度在整个过程中始终保持恒定, 如图8(b)所示,省去了压头升温和降温的时间,从而提高了生产效率。 此外,预先施加的NCF 也能够防止在从过程A 到过程B 的基板传输过程中芯片的移动。 图8(d)展示了键合后的互连界面截面图。

TORAY 这种分步键合的方法也可以用在芯片堆叠中以提高生产效率,如图9 所示[26,28]。 图10 为用这种方法键合后的三维芯片堆叠截面示意图,可以看到能够实现良好的三维堆叠互连。

3.2 提高电互连可靠性

预成型底部填充技术在实际应用中的另一个主要问题是凸点处的电互连可靠性。 由于底部填料在凸点互连之前就已经铺展在芯片载体上了,因此在凸点互连过程中,底部填料中的SiO2填料很容易残留在凸点之间,如图11 所示[10],从而降低互连的导电性能和载流能力,影响在高温/高湿或热循环下的可靠性。

针对以上问题,很多公司及研究机构都提出了相应的解决方案,主要包括双层工艺、两步工艺、混合键合以及自组装技术等。

佐治亚理工学院[29]、HITACHI[30]等提出了使用两层非流动底部填料的方法。 双层底部填充方法工艺流程如图12 所示: 首先在基板上施加一层底部填料,这种材料具有相对较高的粘度且不含SiO2填料,然后在其上面再滴涂一层含有SiO2的底部填料,最后将芯片放置在基板上进行键合,实现凸点互连与底部填料的固化。已有文献报道用含65%(质量分数)的SiO2填料的顶层底部填料可以实现100%的互连良率[29]。使用这种双层工艺虽然可以避免SiO2颗粒的嵌入,但是在实际工艺过程中,需要对各工艺参数以及材料参数进行精确的控制,如底层材料的厚度和粘度对焊料凸点的润湿性起至关重要的作用,键合过程中的压力以及温度直接影响了2 种材料的融合固化以及焊料凸点的互连等,因此实际生产中工艺窗口很窄。 此外,由于该工艺中使用了2 种底部填料, 大大增加了工艺步骤和工艺成本。

图8 基于NCF 底部填充PMD 的键合工艺[24]

图9 基于NCF 底部填充的分步键合方法应用于芯片堆叠中[26]

图10 三维芯片堆叠键合截面图[26]

图11 底部填料中的SiO2 填料残留在凸点的键合界面[10]

图12 双层底部填充方法[29]

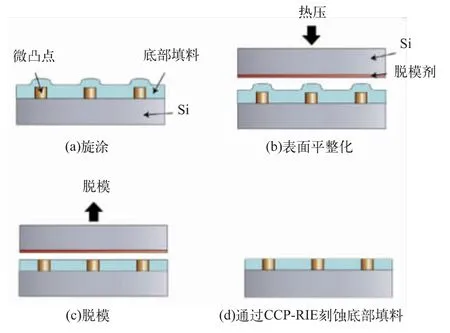

TORAY[32]、IMEC[33-36]等还提出了2 步工艺的方法解决互连可靠性问题。 即在圆片上施加NCF 之后,通过化学机械抛光(CMP)、快速切割等方法,对凸点和底部填料的表面进行处理, 一方面实现表面的平坦化,另一方面也可以去除凸点表面的底部填料,从而解决SiO2填料的嵌入问题。利用快速切割的方式去除凸点上的底部填料工艺流程如图13 所示[32]。 图14 展示了表面处理后的效果[33],可以看到CMP 之后凸点能够完全暴露出来。 该方法的缺点是增加了工艺成本和工艺难度。 在化学机械抛光中,需要选择合适的抛光液,从而同时实现Cu/Sn 凸点与底部填料的平坦化。研究表明, 对于嵌入底部填料中Sn 凸点的化学机械抛光,其对抛光液的酸碱性有很强的依赖性,选择酸性-中性的抛光液能够实现更加平坦的表面[33]。此外,利用快速切割的方法,容易在凸点及底部填料表面产生比较大的划痕。 为了简化工艺、降低成本,早稻田大学[37]提出了一种更为简单的结合等离子刻蚀的热压平整化工艺,如图15 所示,也可以达到预期的效果。

图13 利用快速切割的方式去除凸点上的底部填料[32]

图14 CMP 后得到的凸点/ 底部填料表面SEM 照片[33]

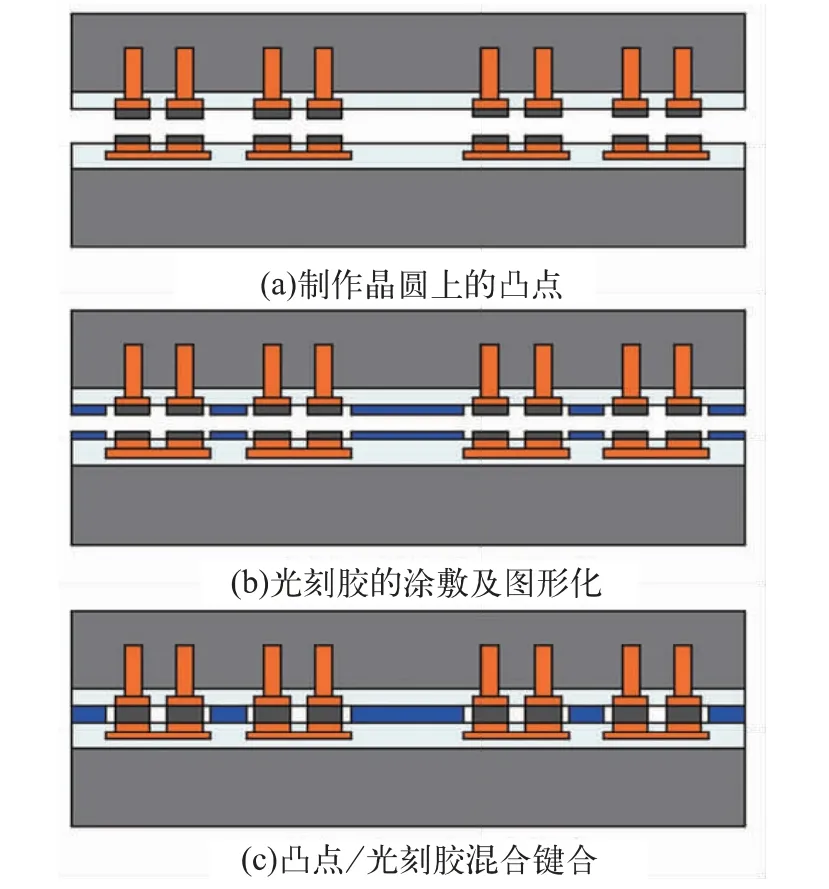

为了去除凸点表面的底部填料,提出了采用光敏光刻胶作为底部填料的方法[38-40]。 在完成圆片上的凸点制作之后, 先旋涂一层光敏光刻胶作为底部填料,然后利用光刻技术对光刻胶进行图形化处理,去除凸点上的光刻胶,工艺流程如图16 所示[38]。 由于凸点键合与光刻胶固化同时实现, 该方法被称为混合键合。常用的光敏光刻胶有BCB、PI、SU-8 等。目前有许多研究机构都对混合键合技术进行了研究。 大连理工大学利用Cu-SnAg 固液扩散键合技术来实现凸点互连,并采用B-阶干膜作为光敏光刻胶来实现底部填充,其键合工艺参数(温度/ 时间/ 压力) 为240 ℃/10 min/10 kN,最终通过控制凸点厚度与有机物厚度同时实现了凸点互连以及光刻胶的固化[39]。 台湾交通大学也对混合键合进行了研究,在利用Cu-Sn 固液扩散键合技术实现凸点互连的基础上,对比优化了使用不同光敏光刻胶(PI、SU-8 以及BCB)对应的最佳键合工艺参数[38]。清华大学采用了独特的非对称混合键合结构,即只在顶部圆片上进行光刻胶的旋涂、光刻等,而不对底部圆片进行任何工艺操作,从而保护了底部圆片上的器件结构,使其适用于MEMS 圆片键合中[40]。 但由于光刻胶中一般不含SiO2颗粒, 其CTE 值较常规底部填料高,因此使用混合键合方法对封装体整体可靠性的影响还需深入研究。

图15 热压-等离子刻蚀方法去除凸点表面的底部填料[37]

图16 凸点/ 光刻胶混合键合工艺流程[38]

佐治亚理工学院WONG 等[41]还提出了一种新的自组装技术来解决SiO2颗粒的嵌入问题,通过对焊盘及钝化层的表面预处理,使铜焊盘表面疏水而钝化层Si3N4表面亲水,从而实现底部填料的自组装,如图17所示。 研究结果表明,表面处理后的焊盘和钝化层表面的水接触角差值可以达到119.9°(或底部填料接触角差值可以达到91.6°),从而实现了自组装,解决了凸点互连中底部填料嵌入的问题。 图17 通过扫描电镜及能谱测试也展示了表面处理后铜焊盘上几乎没有SiO2颗粒,成功地实现了底部填料的自组装。 文中还提出该自组装技术能够与市场上的商业底部填充剂相容。

图17 底部填料在铜焊盘及阻挡层表面的自组装效应[41]

3.3 开发纳米级高热导率填料

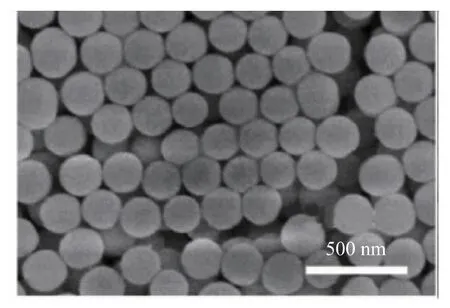

预成型底部填充技术主要应用于倒装芯片窄节距互连中,芯片与基板之间的高度也比较小,传统底部填料中的微米级SiO2颗粒难以满足节距及高度不断缩小的需要, 很容易出现孔洞, 因此利用纳米级SiO2作为填料成为了新的发展趋势[2,41-42],图18 所示为制得的纳米SiO2颗粒。市场上也开始出现了一些较为成熟的填充纳米SiO2的底部填料。

图18 纳米SiO2 颗粒扫描电镜照片

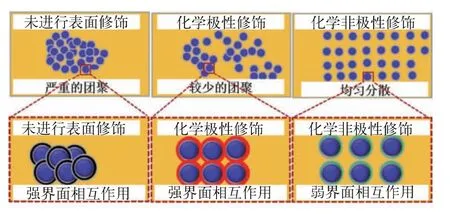

利用纳米SiO2颗粒作为填料还存在一些问题:纳米SiO2具有较大的比表面积和表面自由能,易于产生团聚,导致分散性较差;同时,填充纳米SiO2后底部填料的粘度急剧增加,流动性变差;此外,严重的团聚会使填料与基体之间的界面结合变弱,降低底部填料整体的热机械性能[42]。

研究结果表明,通过溶胶-凝胶法、化学沉淀法等制备得到的SiO2纳米颗粒表面存在大量的硅烷醇,会导致底部填料的粘度增加,热机械性和可靠性也会下降。因此,为制备得到高性能的底部填料,去除SiO2填料表面的-OH 基是非常必要的[43]。 表面改性是一种有效的方法,可消除-OH 的负面影响。 最广泛使用的表面改性剂是硅烷偶联剂。 由于其独特的结构,其一端可以与SiO2填料发生物理或化学键合,另一端与聚合物基体实现优异的相容性,可以显著改善SiO2在聚合物基体中的分散性和界面相容性。 按照硅烷偶联剂的添加方法可以分为物理添加和化学改性。 物理添加是直接将填料和偶联剂混合到环氧基质中,而化学改性是将改性后的SiO2添加到环氧基质中。 相比之下,化学表面改性可以在粘度和热机械性能方面实现更好的改善[44]。 图19 所示为利用化学改性方法对纳米级SiO2颗粒进行表面处理后的效果[45],通过这种方法得到了分散均匀、与聚合物基体界面相容的纳米SiO2填料,该复合材料的各项性能(包括粘度、CTE 等)都满足对底部填料的需求。

图19 化学改性方法对纳米级SiO2 颗粒进行表面处理[45]

此外,随着对底部填料导热性能的需求进一步增加,需要开发新的材料来提高材料的热导率。 目前的研究方向为用其他热导率较高的材料替换SiO2颗粒作为新的填料,从而提高底部填料整体的热导率。 有研究将具有高导热性的陶瓷填料如氮化硼、 氮化铝、氧化铝和碳化硅等掺入环氧树脂,但是因为要实现高导热性能,往往需要填充大量的陶瓷填料,而这可能会导致底部填料的热机械性能变差,粘度变高。 也有研究利用银纳米线(AgNWs)作为填料,但银的导电性能太好, 因此底部填料的绝缘性无法得到严格的保证。有研究者提出了AgNWs@SiO2核壳结构来作为填料[46],如图20 所示。 最终得到的AgNWs@SiO2复合环氧基底部填料既可以实现较高热导率[大于1 W·(m·K)-1],又能满足底部填料绝缘性、粘度小于20 Pa·s 等其他方面的性能需求。

图20 新型底部填充材料中的填料[46]

4 结论

随着倒装芯片底部凸点的节距越来越小,原来的组装后底部填充技术已不能适应100 μm 以下的窄节距工艺,为了窄节距芯片互连的需要开发了预成型底部填充技术,该技术主要包括非流动底部填充和圆片级底部填充两大类。

以NCP 为代表的非流动底部填充和以NCF 为代表的圆片级底部填充均已成功应用于实际工业生产中。 NCP 与NCF 的材料组成基本相同, 但NCP 为液态,NCF 是以膜的形式存在,两者工艺不同。

针对NCP/NCF 预成型底部填充技术生产效率较低、电互连可靠性以及材料性能等方面的问题,产业界提出了多种改进措施:针对提高生产效率,开发了分步键合的方法,该法也能用于芯片三维集成;为解决SiO2颗粒嵌入互连界面的问题,提出了采用双层工艺、两步工艺、混合键合及自组装技术等解决方法,以去除凸点表面的底部填料从而得到更为可靠的电互连。 底部填料性能的改进主要集中在填料的选择上:为适应窄节距互连,采用纳米级SiO2填料并对易发生团聚的纳米SiO2颗粒进行表面改性。 此外,还可以通过将传统的SiO2填料替换成热导率更高的陶瓷粉填料、氧化铝填料、纳米级AgNWs、AgNWs@SiO2等材料来获得导热性能和可靠性更高的底部填料,以满足目前电子产品中更高的散热需求。 今后窄节距倒装芯片的底部填充技术和高性能底部填充料的改进都仍将是微电子封装技术发展中的重要方向之一。