高速CMOS 图像传感器及其应用

2021-01-08窦润江曹中祥李全良刘力源吴南健

窦润江 ,曹中祥,李全良,冯 鹏 ,刘力源 ,刘 剑 ,吴南健 ,

(1. 中国科学院半导体研究所半导体超晶格国家重点实验室,北京 100083;2. 中国科学院大学材料与光电研究中心,北京 100049;3. 中国科学院脑科学与智能技术卓越创新中心,北京 100083)

高速CMOS 图像传感器能将人眼无法分辨的高速现象捕捉下来,广泛应用于科学研究、运动分析、工业机器视觉和航空航天等领域[1-7].高速CMOS 图像传感器的像素性能决定了成像速度和质量.近年来相关研究机构提出了4 个晶体管(4 T)结构、5 个晶体管(5 T)结构以及8 个晶体管(8 T)结构的高速CMOS 图像传感器像素[8-10],这些像素采用具有低噪声、低暗电流和高量子效率(quantum efficiency,QE)特点的掩埋型光电二极管(pinned photodiode,PPD)作为光电转换器件[11-12].但是由于高速图像传感器的像素通常采用大尺寸的PPD 结构,使得像素的设计面临如下两个关键问题.首先,在大尺寸PPD 中,横向电场较弱,电荷的转移只能通过载流子的扩散运动来完成,因此电荷的转移速度较慢,限制了成像速度.其次,当电荷传输管从导通状态切换至关闭状态时,电荷传输管传输沟通中部分电荷会反弹回PPD中,将导致图像拖尾现象.另一方面,像素信号读出电路是高速CMOS 图像传感器的核心模块之一,读出电路的性能决定了图像传感器的速度和质量.设计面积小、功耗低的像素信号处理电路及其阵列需要面对各种设计挑战.

针对上述问题,本文采用了具有梯度掺杂PPD和非均匀掺杂沟道传输管的像素结构设计了像素阵列;采用结构紧凑、功耗低的模拟预处理和逐次逼近型模数转换器(SAR ADC)电路设计了列并行像素信号读出电路阵列;采用0.18µm CMOS 工艺试制了一款高速低功耗CMOS 图像传感器芯片,并对芯片的性能指标进行了测试验证.本文基于此高速CMOS图像传感器芯片试制了高速相机,并应用在高速目标跟踪系统中.针对高速相机采集的800×600 分辨率的8 位灰度图像,本文采用训练好的轻量级卷积神经网络(convolutional neural network,CNN),在较小的候选搜索区域对候选目标窗口进行分类,进而实现高速的目标定位,使跟踪系统实现了550 帧/s 的高速目标跟踪,使目标保持在视场的中间.

1 高速CMOS图像传感器的设计

1.1 高速CMOS图像传感器的架构

本文设计的高速CMOS 图像传感器芯片采用列并行信号处理电路的架构,集成高速像素阵列、低功耗的像素信号读出电路以及控制器等模块,如图1 所示.像素阵列大小为N×M,其中最上方的N1行和最下方的N1行为暗像素,有效像素为(N-2 N1)×M;M×1 个像素信号处理电路阵列分为奇、偶各(M/2)×1个,分别位于像素阵列的上方和下方,奇、偶列的像素输出信号分别经奇、偶像素信号处理电路阵列并行处理;奇、偶列像素信号处理电路阵列输出的全并行数字数据经输出模块分别转化为P×1 路的输出通道,每个通道每个时钟周期输出一个像素的数据.

图1 高速CMOS图像传感器的结构Fig.1 Structure of high-speed CMOS image sensor

芯片控制器产生芯片正常工作需要的所有控制信号,并实现与芯片外的通信,如经SPI 串行接口对像素的积分时间、工作模式等进行配置.芯片控制器产生的像素阵列控制信号,控制像素复位、积分、电荷转移及信号输出等过程.芯片控制器产生的像素信号处理电路控制信号(如选通、启动等),启动像素信号处理电路阵列工作.芯片控制器控制像素阵列和像素信号读出电路阵列协同工作,像素信号读出电路阵列对像素阵列输出的信号逐行并行处理并输出数字信号,量化后的数字信号经数据输出单元多路串行输出.

1.2 高速CMOS图像传感器的像素

本文提出的4 T 高速像素[13],其电路和版图分别如图2(a)和(b)所示,包括梯度参杂掩埋型光电二极管(GD-PPD)、非均匀掺杂沟道传输管(NUDC TG)、浮空扩散(FD)节点、复位管(MRST)、源极跟随器(MSF)和行选择管(MSEL).复位管耗尽GD-PPD 的N区并复位FD 节点,当传输管打开时,GD-PPD 中的光生电子被转移到FD 节点.在FD 节点处,光生电子转换为电压信号.电子电压转换后,源极跟随器用于缓冲FD 节点的电压.当行选择管接通时,缓冲的电压信号被输出像素阵列.

图2 提出的像素电路图及版图示意Fig.2 Proposed pixel circuit and layout diagram of PPD

本文像素的横向截面图和电势分布分别如图3(a)和(b)所示.与传统的PPD 像素相比,本文采用的如图3(a)所示像素分别在PPD 的N 埋层和TG 的P 层都采用两次掺杂工艺,并且对GD-PPD 和NUDC TG 的交叠区域进行了优化.

PPD 的N 埋层采用两次N 掺杂,分别为第1 次形成N 区域以及第2 次形成N- 区域,最终形成GD-PPD.其中N 区域相比N- 区域,掺杂深度浅、掺杂浓度高,这样在PPD 的整个N 埋层内形成横向和纵向的浓度梯度.从而在PPD 内电荷向传输管传输过程中,由于N- 区域和N 区域之间的杂质浓度梯度带来的电势梯度将有利于PPD 中的电荷快速转移到传输管.图3(b)为梯度掺杂PPD 像素工作过程

图3 高速像素的结构Fig.3 High-speed pixel structure

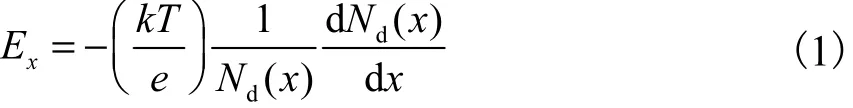

中电荷转移示意图.其中,由梯度掺杂带来的横向电场强度[14]可以表示为

式中:Ex为位置x 处的电场强度;k 为玻尔兹曼常数;T 为开氏温度;e 为电子电量;Nd(x)为位置x 处的掺杂浓度;为位置x 处的杂质浓度梯度.由式(1)可知,PPD 内的横向电场方向由N 区指向N-区,这样N- 区内的电子可以通过横向电场漂移到N区.因此梯度掺杂的结构可以有效增强PPD 内的横向电场强度,减少电荷转移时间.

如图3(a)所示,在TG 的沟道中,P- 和P 两个掺杂层形成NUDC TG.其中P 区沟道掺杂浓度高,P- 区沟道掺杂浓度低.TG 沟道表面的电势与-(VGVT(x))成正比,其中,VG是TG 的控制电压,VT(x)是位置x 处的阈值电压.对于提出的NUDC TG,VT是增加阈值调整注入后的电压,调整后的阈值电压[14]表达式为

式中:VT0是进行阈值电压调整注入之前的阈值,D1(x)为位置x 处阈值调整注入浓度,Cox为栅电容密度.由式(2)可知,掺杂浓度高的沟道区域阈值电压高,P 区的阈值高于P- 区的阈值.因此靠近PPD 一侧的沟道电势始终高于靠近FD 一侧的沟道电势.在TG 由开启状态转到关闭时,沟道内的电荷只移向FD 节点.从而有效地减少由TG 沟道中的反弹电荷引起的图像拖尾.

本文使用计算机辅助设计软件对像素器件的掺杂浓度和电荷转移特性进行了仿真,得出最优的工艺参数.

图4(a)所示为像素的杂质浓度分布图,其中N区的长度为LN,N 区与传输管沟道的交叠长度为L0,P 区的长度为LP.

图4(b)给出了仿真得到的PPD 内残留电荷随N区离子注入剂量的变化.当N 区离子注入剂量大于2.2×1012cm-2时,PPD 内的残留电荷急剧增加.因此,N 区的最佳离子注入剂量为2.2×1012cm-2,这时的电荷转移时间是40 ns,能够满足高速图像传感器的要求.

图4(c)给出了改变N 区的长度LN时PPD 内光电子电荷转移特性的仿真结果,其中横坐标为电荷转移时间,N 区和N- 区的离子注入浓度为固定值.由仿真结果可以看出,当LN从1.4µm 增加到2.4µm时,电荷转移时间逐渐减少.但是,当继续增加LN到2.9µm 时,转移时间开始增加.因此,LN为2.4µm时,电荷转移时间最小.

图4(d)给出了沟道反弹电荷数量与P 区离子注入剂量的关系,其中P- 区的离子注入浓度为固定值.由图中可以看出,当离子注入剂量大于6.0×1012cm-2时,反弹电荷数量减少的速度明显变慢.因此,P 区的最佳离子注入剂量为6.0×1012cm-2.

根据式(1)可知,GD-PPD 内的横向电场强度与N 埋层内2 次离子注入区的浓度梯度成正比.采用高掺杂的N 区可以提高PPD 内的横向电场.然而,高掺杂的N 区可能会在靠近TG 的沟道区域引起电荷势阱[15],造成图像拖尾.此外,随着N 区掺杂浓度的增加,FD 区域与N 埋层之间的电势差减小,导致沟道内的电荷转移速度下降.因此需要选取合适的N 区与传输管沟道的交叠长度L0,使得N 区与传输管沟道形成有效的电子转移路径.本文中,L0选取0.26µm.

根据式(2)可知,传输管沟道内P 区与P- 区的掺杂浓度差异的大小决定了沟道内电势梯度的大小.如果P 区与P- 区掺杂浓度差异越大,沟道内靠近PPD 一侧的沟道电势与靠近FD 一侧的沟道电势差异也就越大,因此传输管沟道内电荷向PPD 反弹越小.然而,随着P 区掺杂浓度增加,靠近PPD 一侧的沟道电势与靠近FD 一侧的沟道电势之间的电势差会减小,会增加电荷转移时间.因此,传输管沟道内P 区掺杂需要进行优化设计使得减少电荷反弹的同时不影响PPD 内电荷向FD 的传输.另外,图4(a)中所示P 区长度LP需要尽可能的短,因为如果P 区长度过长,P 区内的沟道电荷也会向PPD 内反弹.本文中,LP选取工艺设计规则允许的最小长度0.26µm.

图4 像素仿真Fig.4 Simulation of pixel

1.3 高速CMOS图像传感器的读出电路

本文设计了一个适于高速CMOS 图像传感器的列并行像素信号读出电路,其由模拟预处理电路和12 bit SAR ADC 及读出控制单元构成[16],如图5 所示.模拟预处理电路实现相关双采样(CDS)、可编程增益放大器(PGA)等功能.相关双采样对像素输出的复位电压和信号电压VPIX进行相减操作,减小固定模式噪声(FPN).可编程增益放大器,放大像素输出的信号,增强图像的对比度和图像传感器的动态范围.

图5 像素信号读出电路结构Fig.5 Block diagram of pixel signal readout circuit

CMOS 图像传感器根据应用的场合不同会改变输出帧率,由于模拟预处理电路和SAR ADC 的工作时间是固定的,随着帧率的减小,读出电路的功耗线性减少.本文设计的模拟预处理电路和SAR ADC 都采用了开关功耗控制(SPC)技术,在其不工作时关断二者的直流通路,以降低读出电路的平均功耗.图像传感器的帧率降低,空闲时间变长,关断时间变长,模拟预处理电路和SAR ADC 的平均功耗随之降低;反之则二者的平均功耗增加.像素信号读出电路控制器由图像传感器的芯片控制器触发启动,启动后控制模拟预处理电路和SAR ADC 完成一次操作,之后等待下一次触发信号启动.在空闲时间控制逻辑电路不发生翻转,因而像素信号读出电路的平均功耗随等待时间的增加即帧率的下降而线性下降.于是,像素信号读出电路的平均功耗随着图像传感器帧率的降低而线性下降.

2 高速CMOS图像传感器芯片及测试

本文采用0.18µm CMOS 工艺制造设计和试制了一款高速低功耗列并行CMOS 图像传感器芯片,像素阵列大小为816×600,其中最上方的8 行和最下方的8 行为暗像素,有效像素为800×600;600×1个像素信号处理电路阵列分为奇、偶各300×1 个,芯片尺寸为20.5 mm×10.5 mm,芯片的电子显微照片如图6 所示.

图6 高速CMOS图像传感器Fig.6 High-speed CMOS image sensor

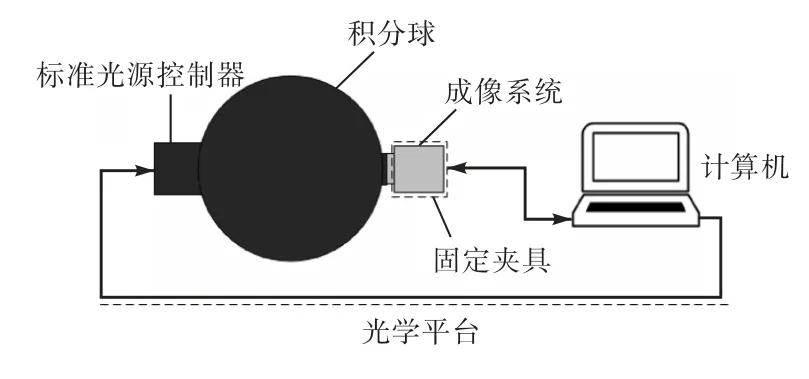

为了测试高速图像传感器芯片,本文设计了在暗室环境下的光电测试系统和高速CMOS 成像系统,如图7 所示.计算机通过USB 接口发送指令到光源控制器来控制光源头的输出强度.本文采用标准的线性LED 光源,光源头搭配积分球在出光口处输出均匀光.高速CMOS 成像系统置于升降台上,使均匀光照射在传感器的感光面板上.成像系统输出的图像数据通过USB 接口传输到计算机.

图7 光电测试系统Fig.7 Photoelectric test system

图8 测试的电荷转移特性和图像拖尾特性Fig.8 Measured charge transfer characteristics and image lag characteristics

像素的图像拖尾测试时序如图8 所示.VSEL是行选择管控制电压,VRST是复位管控制电压,VTG是传输管控制电压.LED 表示LED 光源的控制信号.LED 光源只有在LED 控制信号高电平期间才打开.在一定的积分时间之后,PPD 内产生一定数量的光生电荷,所产生的光生电荷在第i 帧被转移.如果在第i 帧PPD 内电荷没有被完全转移,那么残留的电荷将在第i+1 帧被转移,在第i+1 帧所测得的信号即为图像拖尾.经过测试,没有采用优化措施的像素图像拖尾为7.1%,本文设计的高速像素图像拖尾小于0.5%.

光强响应用来表征图像传感器的灵敏度R,是通过对光响应曲线的线性拟合求得[17-18].固定传感器的曝光时间texp,单位:s,改变光照强度E,单位:lx,以不同的光照强度条件下取得的图像所有像素平均灰度值µy-µdark为纵坐标(µdark为无光照条件下传感器所有像素输出的平均灰度值),单位:DN(digital number),辐照度 H 为横坐标,单位:lx·s,绘制光响应曲线.对光响应曲线的线性部分进行线性拟合,拟合直线y(如式(3)所示)的斜率 a1即为灵敏度R.

时域暗噪声 σy,dark是传感器在积分时间最短条件下的暗噪声值,单位:DN,即本底噪声.在无光照、最短积分时间条件下,取多帧图像S,计算所有像素输出灰度值的时域方差(式(4)),并取均值(如式(5)所示),即可得到时域暗噪声[18].

式中:L 为采集图像的数量;M 和N 分别为图像的行和列数;m 和n 为像素的坐标索引.

动态范围DR,单位:dB,表现了图像Hab,ab传感器芯片可探测的信号范围.根据式(6)计算得到[18],其中,μy,sat是饱和灰度值,单位:DN,σy,dark是时域暗噪声,单位:DN.

传感器芯片的信噪比SNR 定义为输出图像的有效平均灰度值µy-µdark与噪声σy的比值[18],单位:dB.固定传感器的曝光时间,改变光照强度,以不同的光照强度条件下取得的图像所有像素平均灰度值µy-µdark为横坐标,噪声σy(单位:DN)为纵坐标,绘制光子转移曲线(photon transfer curve,PTC).PTC的顶点记为SNR 点,根据式(7)计算SNR.

图 9(a)和(b)所示分别为测试得到的高速CMOS 图像传感器光响应曲线和光子转移曲线.根据式(7)计算得到信噪比约为45.8 dB.根据此顶点的位置确认图像传感器光响应曲线的饱和灰度值,选取饱和灰度值以内0~70%范围的光响应曲线线段进行线性拟合,得到拟合直线的斜率即灵敏度约11 V/(lx·s).根据式(4)和式(5)计算得到时域暗噪声的值约为1.075 6 DN.结合饱和灰度值,根据式(6)计算得到动态范围约65 dB.设置图像传感器芯片的增益和输出帧率为最高时,使芯片的感光面板工作在饱和状态一段时间以后,测试得到图像传感器芯片的总功耗约为830 mW.

图9 CMOS图像传感器的光电测试曲线Fig.9 Photoelectric test curve of CMOS image sensor

本文对设计的高速CMOS 传感器芯片做高速成像测试.设置芯片工作在1 000 帧/s 时拍摄的4 张连续原始图像如图10 所示,图像的间隔时间为20 ms,清晰记录下了高速旋转的扇叶及硅胶模型与桌面碰撞的过程,可以看出图像没有明显的拖尾现象.

如表1 所示,本文的高速CMOS 图像传感器与传统结构设计的高速CMOS 图像传感器[19-20]相比,虽然功耗比文献[19]大,灵敏度比文献[20]小,但在更高的分辨率下帧率分别提高了约6.6 倍和1.5 倍.

图10 1 000 帧/s时图像传感器拍摄的原始图像Fig.10 Raw images taken by image sensor at 1 000 frames per second

表1 与其他高速CMOS图像传感器的性能比较Tab.1 Performance comparison with other high-speed CMOS image sensors

3 高速CMOS相机及快速目标跟踪

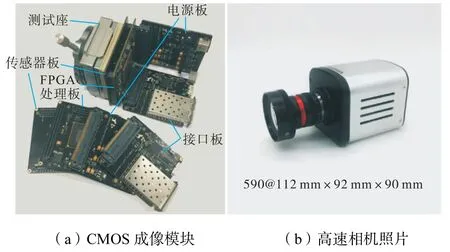

基于设计的高速图像传感器芯片和FPGA,本文设计了模块化的高速CMOS 相机,包括供电板、FPGA 处理板、CMOS 传感器板和接口板,如图11(a)所示.FPGA 处理板实现图像传感器的控制、数据格式转换、图像数据输出等功能.接口板设计有USB3.0 接口和2 路SFP+光纤接口,图像传感器的成像参数可以通过USB3.0 接口配置,也可以通过光纤接口在远端的主机配置.相机照片如图11(b)所示,相机前面板上的镜头安装法兰兼容标准的C 卡口工业镜头.为保障高速相机长时间的稳定工作,相机内部采用风冷散热,FPGA 芯片加装散热铝片,散热片上安装风扇,利用FPGA 内部的内核温度监控控制模块控制风扇的转速.同时外壳的两侧和上下靠近传感器板位置处都做开孔处理加强空气的流动,进一步增强相机内部的散热.高速相机的所有模块(不包括镜头)安装后,质量约590 g,尺寸112 mm×92 mm×90 mm(长×宽×高).

图11 高速CMOS相机Fig. 11 High-speed CMOS camera

在工业机器人自动分拣系统中,分拣的速度影响整个系统的效率,而且需要将一段时间内的自动分拣过程存储起来,方便后期人工分析分拣过程和调试.本文将高速CMOS 相机应用到工业机器人自动分拣系统中,使系统可以实现高速目标跟踪的同时,实时地将高速图像数据存储到计算机的固态硬盘中,跟踪子系统的照片如图12(a)所示.高速相机固定在伺服电机构成的二自由度转台上,2 路光纤通道同时分别输出1 000 帧/s@816×600 的高速图像数据,分别传输到视觉处理器和数据存储器.视觉处理器执行基于卷积神经网络的高速目标跟踪算法,并控制二自由度转台的运动,使视觉目标保持在视场的中心.数据存储器通过光纤接口控制高速相机的工作,将接收到的高速图像数据经过PCIe 接口实时存储到PC 的固态硬盘中.

高速视觉处理器是在一块Arria10 FPGA 开发板上实现,可执行基于卷积神经网络的高速目标跟踪算法.如图12(b)给出了高速目标跟踪流程图,它采用适用于硬件加速的轻量级卷积神经网络,包括3 个卷积层(conv 1~3)、2 个最大池化层(Max Pooling 1~2)和一个全连接层(fc),并在GPU 上完成网络的参数训练.网络的参数如4@28×28,表示这层网络有4 个28×28 的卷积核,可以通过编程写入视觉处理器的参数寄存器,通过训练不同的网络参数,可以实现对不同跟踪目标的分类检测.算法工作时,它将高速图像切片(32×32)送入CNN 网络,CNN 网络对图像切片进行分类并打分,包括目标和背景,分类为目标的切片得分值最高的即为目标的位置.

目标跟踪的结果如图12(c)~(f)所示,可以看出,跟踪系统基本可以保持目标在视场的中心.经过测试,此系统可实现550 帧/s@800×600 的高速目标跟踪,同时存储到主机的高速图像数据(1 000 帧/s@816×600,12 bit)完全正确.为进一步验证高速相机的性能,使存储系统持续工作了24 h 以上,经过验证存储的图像数据完全正确.其中由于硬盘的容量限制(1.92 TB),本文将图像数据循环写满硬盘.

图12 高速目标跟踪应用Fig.12 High-speed target tracking application

4 结 语

本文采用一种适用于高速CMOS 图像传感器的新型像素器件,它具有梯度掺杂掩埋型光电二极管(GD-PPD)和非均匀掺杂传输管(NUDC TG)结构,能够有效减少光生电荷转移时间和图像拖尾.结合采用开关功耗控制技术的像素信号读出电路,设计了一款高速低功耗列并行CMOS 图像传感器芯片.测试结果表明,提出的像素器件有效,能够实现快速的光生电荷转移,减少了图像拖尾.设计的CMOS 图像传感器能够稳定输出最高1 000 帧/s@816×600 的图像数据,并且在最高增益、最高输出帧率的条件下工作时,功耗约为830 mW.