基于FPGA的多码率卷积编码器设计与实现

2020-12-18陈振林唐俏笑梁仪庆

陈振林,赵 利,黄 星,唐俏笑,梁仪庆

(桂林电子科技大学 信息与通信学院,广西 桂林 541000)

由于信号在无线信道中传播会受到噪声、多径干扰和多普勒频移的影响[1],导致接收端进行解码处理时会产生错误的码元。卷积编码是无线通信系统中广泛使用的信道编码技术[2],它可以纠正在无线信道传输中产生的误码,一定程度上降低信道的误码率,提高系统的信噪比,带来一定的编码增益[3]。因此,设计了一种多码率卷积编码器,除1/2码率外,还采用2/3、3/4、5/6、7/8的码率,该编码器能应用在地面数字电视广播系统[4]。

1 多码率卷积编码原理

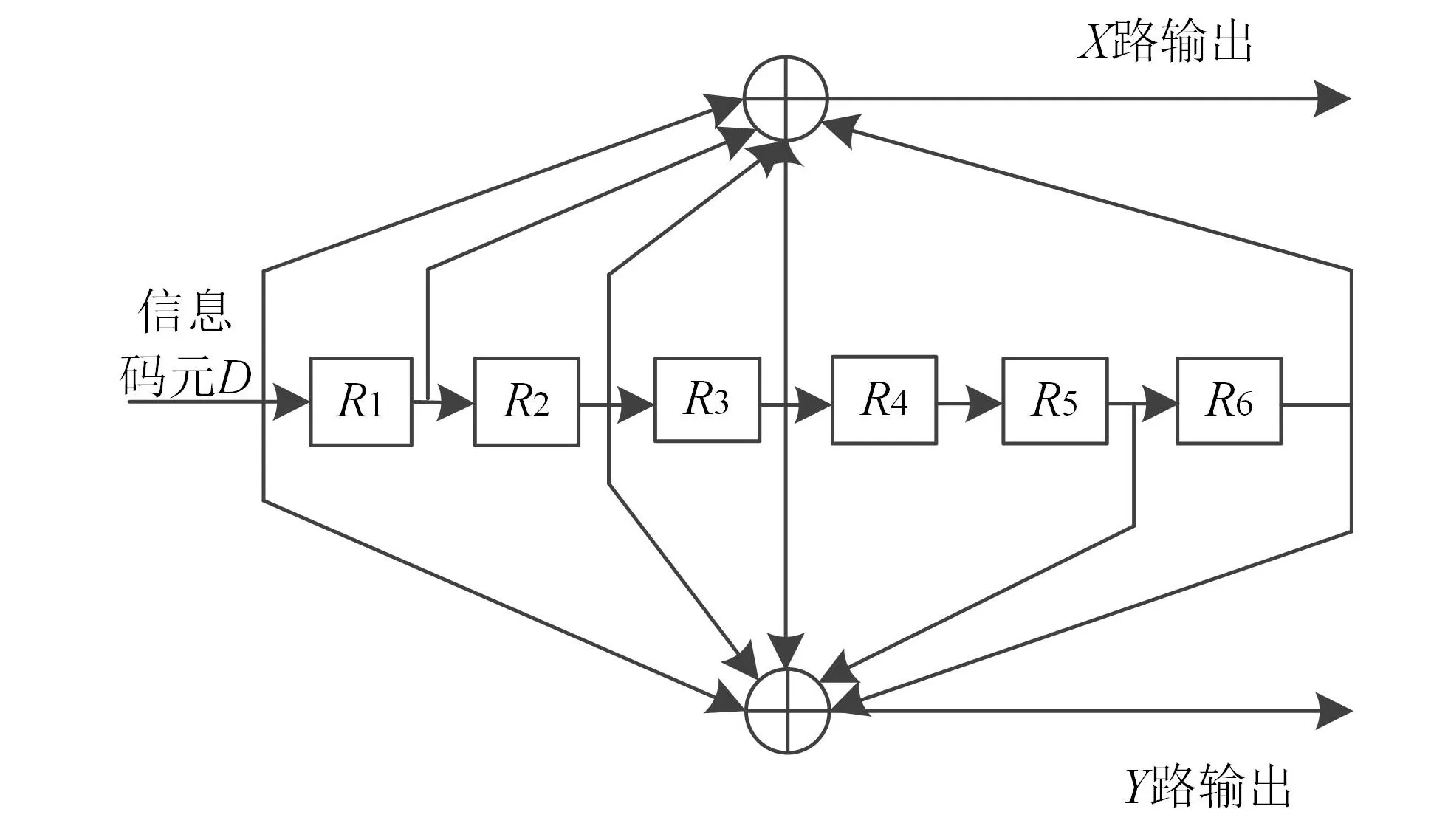

图1 1/2码率卷积编码原理图

卷积码通常用(n,k,N)表示[5],N为编码约束长度,k为编码器输入码元,n为编码器输出编码,卷积码的码率定义为R=k/n。编码器输入k个码元,编码后输出的n个码元不仅与当前输入的k个码元有关,而且还与前面N-1段输入码元有关。1/2码率卷积编码原理图如图1所示。其中:D为输入比特码元数据;R1R2R3R4R5R6为6位移位寄存器;X和Y为输出编码数据。每输入1位的信息码元数据,将会各输出1位的编码数据X和Y,组成2位的编码数据,实现了1/2码率的卷积编码。

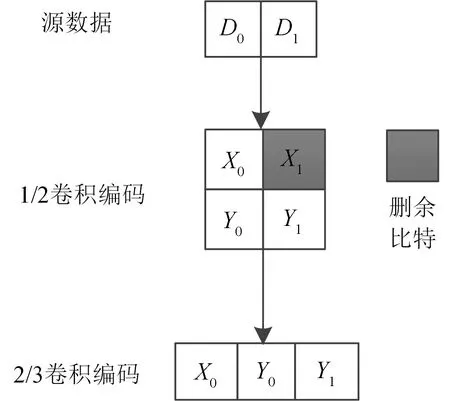

在无线通信基带系统信道编码中,常在卷积编码后采用删余操作。遵照一定的删余规则删除特定位置的数据,可提高通信传输的有效性。因此,在1/2码率卷积码基础上删除一些冗余比特,可实现2/3、3/4、5/6、7/8码率的卷积编码,2/3码率删余过程如图2所示[6]。

图2 2/3码率的删余过程

如图2所示,2/3码率的删余过程为:每输入2 bit数据D0D1,经过1/2卷积编码后为4 bit数据X0Y0X1Y1,再删除固定位置1 bit数据X1,最终输出3 bit数据X0Y0Y1,实现2/3码率的卷积编码,其他码率的删余模式如表1所示。

要实现7/8码率,删余方式为X:1000101、Y:1111010,“1”表示输出,“0”表示不输出,每输入7位D0D1D2D3D4D5D6数据时,删余后输出8位X0Y0Y1Y2Y3X4Y5X6编码数据序列,实现7/8码率卷积编码。

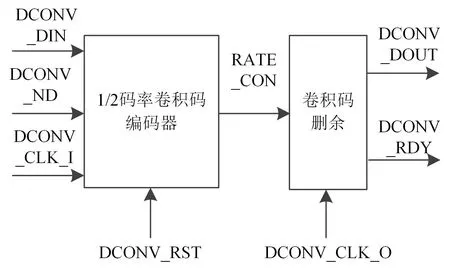

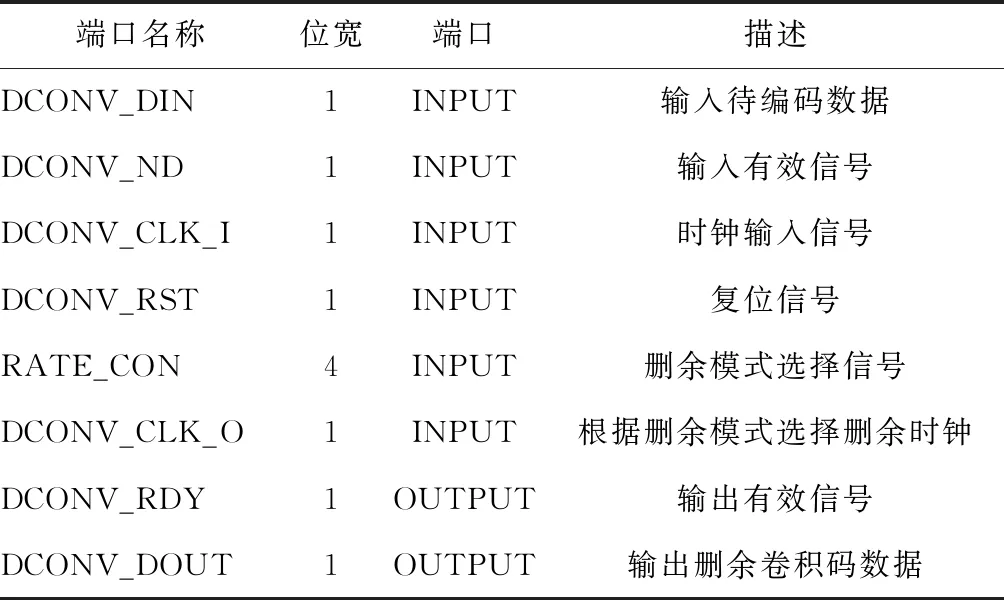

2 多码率卷积编码器的模块化设计

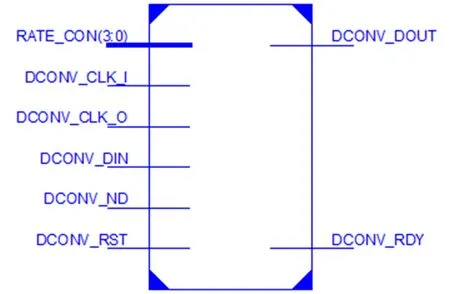

根据无线信道环境来选择不同码率的卷积编码,控制信号(RATE_CON)决定1/2卷积编码器编码后的数据选择何种码率的卷积码删余单元,从而实现多码率卷积编码器的设计。多码率卷积编码器模块设计图如图3所示,多码率卷积编码器模块单元端口说明如表2所示。

表1 删余卷积码模式

图3 多码率卷积编码器模块设计图

端口名称位宽端口描述DCONV_DIN1INPUT输入待编码数据DCONV_ND1INPUT输入有效信号DCONV_CLK_I1INPUT时钟输入信号DCONV_RST1INPUT复位信号RATE_CON4INPUT删余模式选择信号DCONV_CLK_O1INPUT根据删余模式选择删余时钟DCONV_RDY1OUTPUT输出有效信号DCONV_DOUT1OUTPUT输出删余卷积码数据

从图3可看出,输入待编码数据DCONV_DIN,在输入主时钟 DCONV_CLK_I的上升沿进入1/2码率卷积码编码器模块中进行编码处理,该卷积编码模块以串行方式输入,每输入1位数据将会输出2位编码数据,完成1/2码率卷积编码。其余码率在此基础上,根据 RATE_CON控制信号选择相应的删余模块和删余时钟进行删余操作,实现2/3、3/4、5/6或7/8码率的卷积编码。RATE_CON控制信号如表3所示。

表3 RATE_CON控制信号

从表3可看出,如RATE_CON为0001时,选择2/3码率删余模块,对应的删余时钟是输入主时钟DCONV_CLK_I的3/2倍。

3 多码率卷积编码算法

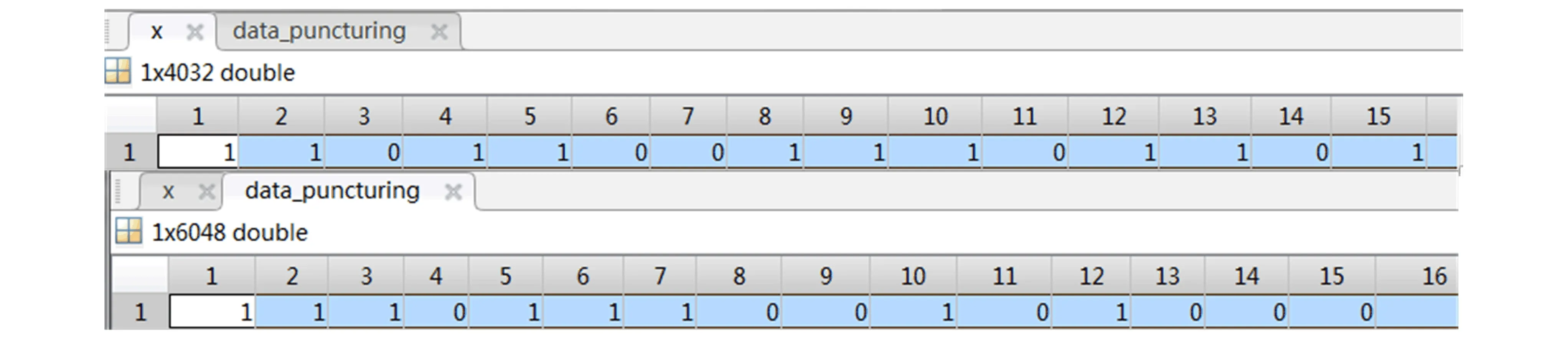

利用MATLAB软件对多码率卷积编码算法进行验证,以2/3码率卷积编码为例,当输入4 032 bit数据x,先进行1/2码率的卷积编码,得到8 064 bit编码数据,选择2/3码率删余操作,输出6 048 bit编码数据data_puncturing,如图4所示。

图4 2/3码率卷积编码MATLAB算法结果

从图4可看出,当输入数据x为1,1,0,1,1,0,……时,进行1/2码率卷积编码后,采用2/3码率删余,得到删余编码输出数据data_puncturing为1,1,1,0,1,1,1,0,0,……,显示的结果符合表1中2/3码率卷积编码的删余规则,因此设计的多码率卷积编码MATLAB算法正确。

4 多码率卷积编码器的时序仿真

根据设计的多码率卷积编码器MATLAB算法,利用Verilog HDL硬件描述语言对多码率卷积编码器进行设计[7],得到多码率卷积编码器模块单元如图5所示。

对多码率卷积编码器Verilog HDL硬件代码进行综合编译通过后,编写顶层测试文件,使用ISE自带的Isim软件进行仿真,以2/3码率卷积编码为例进行分析,其时序仿真结果如图6所示。

图5 多码率卷积编码器模块单元图

图6 2/3码率卷积编码模块时序仿真图

从图6可看出,RATE_CON为0001时,选择2/3码率删余模块,当输入数据DCONV_Din为1,1,0,1,1,0,……时,采用2/3码率删余后,得到2/3码率删余编码输出数据DCONV_Dout为1,1,1,0,1,1,1,0,0,……,与图4中2/3码率卷积编码MATLAB算法结果一致,验证多码率卷积编码器的时序仿真正确。

5 多码率卷积编码器的FPGA实现

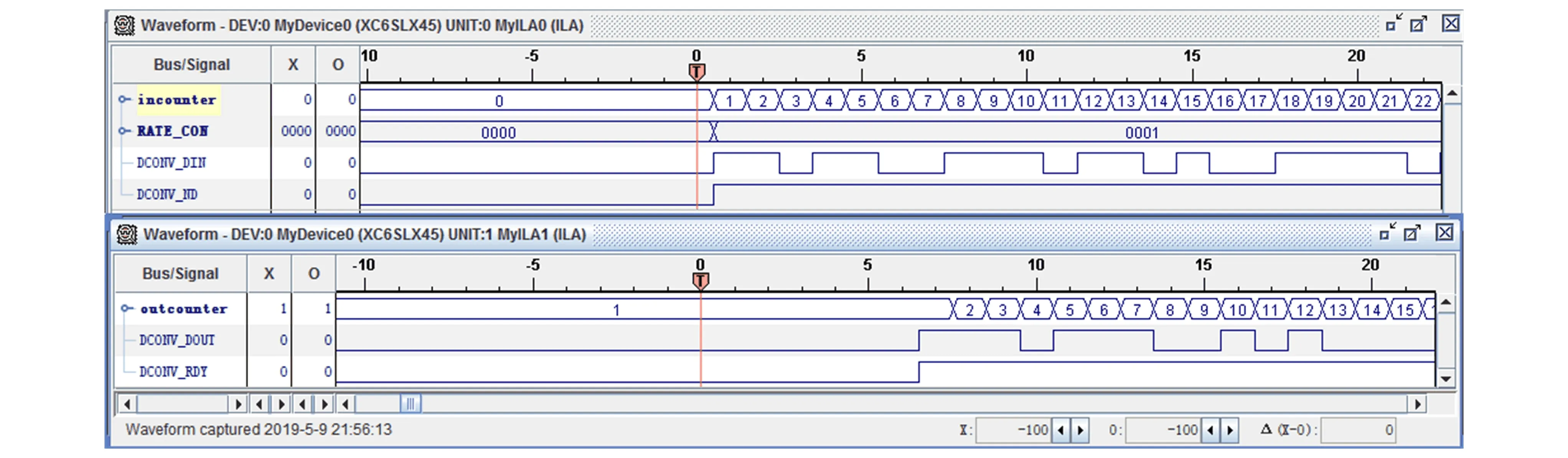

添加触发信号和待观察信号后重新编译代码,通过JTAG口把代码下载到Xilinx公司Spartan-6系列的XC6SLX45-CSG324型号芯片上,使用逻辑分析仪ChipScope Pro抓取多码率卷积编码器内部FPGA数据,采样主时钟为50 MHz,信号抓取结果如图7所示。

图7 2/3码率卷积编码模块Chipscope时序图

从图7可看出,输入主时钟频率为50 MHz,RATE_CON为0001时,选择2/3码率,对应的删余时钟频率为75 MHz,逻辑分析仪ChipScope Pro抓取的FPGA内部输入数据DCONV_Din为1,1,0,1,1,0,……时,采用2/3码率删余后,得到2/3码率删余编码输出数据DCONV_Dout为1,1,1,0,1,1,1,0,0,……,与图6的时序仿真结果对比,可以验证在高速的时钟下,多码率卷积编码模块硬件设计的正确性和可行性[8]。

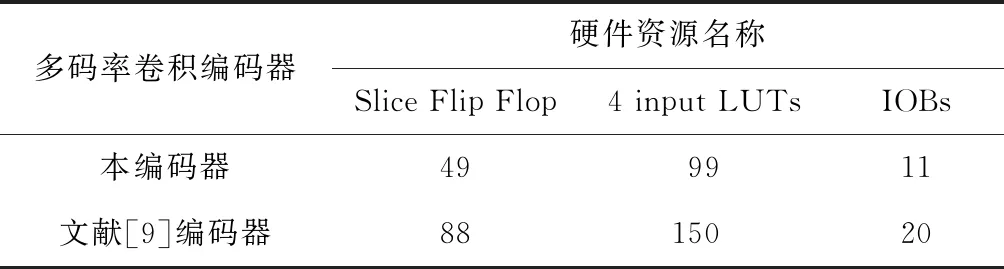

经过综合编译后生成的资源消耗与文献[9]设计的多码率卷积编码器比较如表4所示,资源消耗减少,因此设计的多码率卷积编码器性能更优。

表4 资源消耗表

6 结束语

利用FPGA设计可以应用在地面数字电视广播等通信系统中的多码率卷积编码器。首先,通过MATLAB算法对设计的多码率卷积编码器进行验证,其次,用Verilog HDL硬件描述语言对多码率卷积编码器进行时序仿真验证,最后,使用频率为50 MHz的主时钟,在Xilinx公司Spartan-6系列的XC6SLX45-CSG324型号芯片下完成多码率编码器的硬件在线调试。结果表明,设计的多码率卷积编码器达到了预期的设计要求,且占用硬件资源更少,可应用在地面数字电视广播[10]等通信系统。