基于FPGA的一种通用DBF运算单元实现

2020-10-15徐飞

徐 飞

(西安电子工程研究所 西安 710100)

0 引言

随着技术的进步和战场环境日趋复杂,当前的雷达越来越多的采用DBF体制。该体制雷达在不同的工作模式下,有时要求不同的数据率和波束个数,如搜索模式下要求数据率较低波束数较多,而跟踪模式下要求数据率高波束数较少。如果采用传统的DBF实现架构需要按最大数据率与最多波束数提供实现资源,给信号处理的硬件带来很大的压力。

本文将对DBF体制雷达信号处理机进行研究,提出一种能够满足数据率与波束数互换的通用实现方法。

1 DBF接收原理

为了便于计算,经常使用等距线阵对信号进行接收,即每个阵元等间距的排成一列,如图1所示。

对于窄带信号,其信号包络变化比较缓慢,因此,可以认为等距线阵每个阵元接收到信号的包络是相同的。对于远场信号S(n),用θ表示信号的入射角。若以第一个阵元作为参考,则相邻阵元间的相位差为ω,入射角θ与相位差之间的关系为

(1)

其中d表示阵元距离,λ表示信号波长。为了避免方向模糊,则阵元间距d应满足d≤λ/2的条件,否则过周期的角度可能也被认成信号的入射角。由此可知,第一个阵元收到的信号与同一时刻第k个阵元收到的信号之间的相位差为

(2)

可知,第k个阵元接收信号表示为S(n)e-j(k-1)ω。

对于由m个阵元组成的等距线阵,每个阵元接收信号的相位差所组成的向量

(3)

称为入射信号S(n)的方向向量[1]。

将该向量取共轭作为波束形成系数,进行式(4)的计算

y(n)=x(n)×A(θ)

(4)

其中,x(n)表示m个阵元第n个快拍的数据向量。

图1 等距线阵

可知,当信号的入射角为θ时y(n)的值最大。因此,可使用若干组波束形成系数覆盖所关注的角度空间。

2 基于FPGA的DBF传统实现方法

当前,DBF运算往往使用FPGA实现,FPGA中大量的乘加资源非常适合实现该运算。使用FPGA实现DBF运算的结构如图2所示。

从图2中可知,使用FPGA实现DBF运算的结构可分为三部分:并串转换与分发模块、乘累加模块与并串转换模块。并串转换与分发模块接收各个通道数据转换成串行数据,并接收各个通道在当前频率下的校正系数,实现通道校正处理。校正后的通道数据形成L(L为波束个数)路,给后续使用;每个乘累加模块接收校正后串行数据以及对应的DBF系数,实现各个通道的乘累加运算;并串转换是将每个DBF形成后的数据转成串行方便后续的处理。

3 基于FPGA的DBF通用实现方法

3.1 通用DBF 实现结构

本节要介绍一种通用的DBF实现结构,它能够在处理资源和模块工作时钟率不变的情况下实现处理数据率与波束个数的互换。为了方便描述,我们假设阵元数为32个,工作时钟率为160 MHz,数据率为5 MHz、10 MHz、20 MHz以及对应的波束个数为32、16、8。该实现结构如图3所示。

图2 DBF实现结构

图3 通用DBF实现结构

从图3中可以看到,通用DBF实现结构包括:串并转换模块、信号选择与分发模块、乘累加模块、信号合并与选择模块以及波束选择与并串转换模块。

3.2 通用DBF各功能模块介绍

串并转换模块共有4个,每个实现8路阵元数据的转换,在三种不同数据率情况下,它们的时序不同。如图4所示。

信号选择与分发模块实现串行数据的合成与分发。在5 MHz数据率情况下,将4个并串转换模块形成的串行数据合成一路,并将其复制32份给后面的32个乘累加模块。

10 MHz数据率情况下,将第1个与第3个并串转换模块生成的数据合成一路,并复制16份给后面的第1、3……31个乘累加模块;将第2个与第4个并串转换模块生成的数据合成一路,并复制16份给后面的第2、4……32个乘累加模块。

图4 并串转换模块各种数据率下串行数据时序

20MHz数据率情况下,将第1个并串转换模块生成的数据复制8份给后面的第1、5……29个乘累加模块;将第2个并串转换模块生成的数据复制8份给后面的第2、6……30个乘累加模块;将第3个并串转换模块生成的数据复制8份给后面的第3、7……31个乘累加模块;将第4个并串转换模块生成的数据复制8份给后面的第4、8……32个乘累加模块。

同时,在该模块实现通道校正运算。

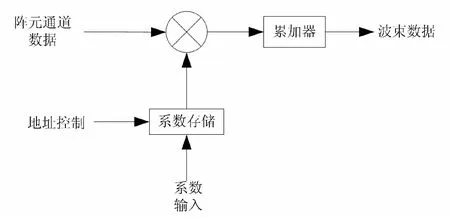

复乘累加模块,与传统实现方法一致。如图5所示。

图5 复乘累加模块实现结构

如图5所示,复乘累加模块由三部分组成。其中系数存储模块接收对应的DBF系数,供运算使用;复乘模块实现通道数据与DBF系数的复乘;累加模块将复乘后的数据进行累加。

信号合并与选择模块实现三种数据率下的处理。在5MHz数据率下,每个复乘累加模块的输出为1个波束,共形成32个波束;在10MHz数据率下,复乘累加模块的第1、2路输出合成波束1,第3、4路合成波束2,……第31、32路合成波束16,共形成16个波束;在20MHz数据率下,复乘累加模块的第1、2、3、4路输出合成波束1,第5、6、7、8路合成波束2,……第29、30、31、32路合成波束8,共形成8个波束。

并串转换模块是将对应的32、16或8个波束数据进行转换,合成一路数据便于后续处理。

3.3 仿真结果

在基于法线方向-6°~+70°范围内,从下向上排列32个波束。其中,发线方向(0°指向)对应波束数为3。现给设计程序加入该指向激励信号,通过modelsim仿真的结果如图6所示。

图6 通用DBF运算单元仿真结果

图6中,5 MHz数据率下实现全部32个波束处理;10 MHz数据率下实现前16个波束处理;20 MHz数据率下实现前8个波束处理。由仿真结果可见,均在波束3形成最大值,与理论设计一致。

4 结束语

本文所介绍的方法,能够在有限的资源使用情况下,通过数据率与波束数的互换,完成通用的DBF的实现,并经过仿真证明该方法正确可靠。